## Wirkung des Ladungsträgerplasmas auf das Abschaltverhalten von Insulated Gate Bipolar Transistoren

Dissertation

zur

Erlangung des akademischen Grades

Doktor-Ingenieur (Dr.-Ing.)

der Fakultät für Informatik und Elektrotechnik

der Universität Rostock

vorgelegt von

Dipl.-Ing. (FH) Jürgen Walter Böhmer

---

**Gutachter:**

1. Gutachter: Prof. Dr.-Ing. Hans-Günter Eckel, Universität Rostock

2. Gutachter: Prof. Dr.-Ing. Josef Lutz, TU Chemnitz

3. Gutachter: Dr.-Ing. Eberhard Ulrich Krafft, Siemens AG Nürnberg

**Datum der Einreichung:** 24.09.2013

**Datum der Verteidigung:** 18.02.2014

---

## Danksagung

Die hier vorliegende Arbeit entstand während meiner Tätigkeit an der Universität Rostock am Lehrstuhl für Leistungselektronik und elektrische Antriebe. Hiermit bedanke ich mich bei allen, welche zum Gelingen dieser Arbeit beigetragen haben.

Besonders danke ich Herrn Professor Dr.-Ing. Hans-Günter Eckel, der durch seine fachliche Unterstützung und sorgfältige Betreuung einen wesentlichen Beitrag zu dieser Arbeit geleistet hat. Ich danke Herrn Professor Dr.-Ing. Josef Lutz der TU Chemnitz für Übernahme des zweiten Gutachtens und Herrn Dr.-Ing. Eberhard Ulrich Krafft der Siemens AG in Nürnberg für die Erstellung des dritten Gutachtens. Weiterhin bedanke ich mich bei den Mitarbeitern der Siemens Traktionsumrichterentwicklung in Nürnberg für die interessanten Diskussionen und für die fachliche und materielle Unterstützung.

Ferner gilt mein Dank den Mitarbeitern des Lehrstuhls für das freundschaftliche und angenehme Arbeitsklima und die Unternehmungen nach Feierabend. Weiterhin bedanke ich mich für die fachlichen Gespräche und die Mithilfe bei der Realisierung von Messungen und Simulationen. Besonderer Dank gilt Herrn Dipl.-Ing. Daniel Wigger, Herrn Dipl.-Ing. Steffen Pierstorff und Herrn Dipl.-Ing. (FH) Tobias Appel, welche sich stets Zeit für fachliche Diskussionen genommen haben. Herrn M. Sc. Holger Wiencke und Herrn M. Sc. Jan Fuhrmann danke ich für die Mithilfe bei den Kurzschlussmessungen. Weiterhin gilt mein Dank Herrn Dipl.-Phys. Jörg Schumann und Herrn Dipl.-Ing. Marten Müller für die Unterstützung bei der Erstellung der Simulationen. Nicht zuletzt möchte ich mich bei Herrn Michael Müller und Herrn Michael Behrens unserer Werkstatt bedanken.

Mein Dank gilt auch universitätsübergreifend bei Herrn Dipl.-Ing. Thomas Basler der TU Chemnitz für den Informationsaustausch beim *Self Turn Off* des IGBTs im Kurzschlussfall.

Vielen Dank auch an meine Freunde, welche stets an mich geglaubt haben und immer motivierende Worte fanden. Danke für das Verständnis vor allem in der Zeit der schriftlichen Erstellung dieser Arbeit, bei der ich nicht immer an allen Aktivitäten teilnehmen konnte. Weiterhin bedanke ich mich für das Korrekturlesen meiner Arbeit.

Besonderer Dank gilt meinen Eltern Jutta und Karl sowie meiner Schwester Beate, welche mich bei meinem Entschluss unterstützt haben erneut die "Schulbank zu drücken", um damit ein Hochschulstudium zu absolvieren. Ohne eure jahrelange Unterstützung und motivierenden Worte wäre diese Arbeit niemals entstanden.

---

## Abstrakt

Der Grund für die gute Steuerbarkeit der Spannungsflanke beim IGBT und beim MOSFET ist die Millerkapazität. Diese koppelt den Kollektor beziehungsweise den Drain zurück auf das Gate. Im eingeschalteten Zustand tragen beim IGBT Elektronen und Löcher zum Stromfluss bei. Demnach ist der IGBT, anders als der MOSFET, ein bipolares Bauelement. Diese Arbeit zeigt, dass der zeitliche Verlauf des räumlichen Maximums der elektrischen Feldstärke maßgeblich das Schaltverhalten bestimmt. Auf Grund des Löcherstromes in der Raumladungszone beim Abschalten des IGBTs ist der Gradient der elektrischen Feldstärke und auch das räumliche Maximum der elektrischen Feldstärke während der Spannungsflanke höher als im stromlosen Zustand. Diese Gegebenheit führt zu unterschiedlichen Auswirkungen der Millerkapazität beim Abschalten von IGBT und MOSFET. Während des Abschaltvorganges des MOSFETs steuert der Gateentladestrom den zeitlichen Verlauf der elektrischen Feldstärke und die zeitliche Änderung der Drain-Source Spannung. Beim IGBT hingegen steuert der Gateentladestrom nur den zeitlichen Verlauf der elektrischen Feldstärke und indirekt die Änderung der Kollektor-Emitter Spannung. Daher kann das Abschaltverhalten des MOSFETs mit einem kapazitiven Ersatzschaltbild analysiert werden. Hingegen ist es beim IGBT sinnvoller, das Abschaltverhalten in direkter Abhängigkeit der elektrischen Feldstärke zu untersuchen. Dazu kann die dreidimensionale Struktur des IGBTs auf eine Dimension reduziert werden. Hiermit lassen sich viele der beim Abschalten auftretenden Effekte erklären. Diese werden im Rahmen dieser Dissertation diskutiert und anhand von Messungen und Simulationen mit einem Finite Elemente Simulator belegt.

---

## Abstract

The reason of the good controllability of the voltage slope at semiconductors like the IGBT and the MOSFET is the miller-capacitance. The miller-capacitance is the feedback of the collector respectively the drain to the gate. In turn-on state of IGBTs there are free electrons and holes to carry the collector current. Therefore the IGBT is instead of the MOSFET a bipolar device. During turn-off the miller-capacitance is charged by the gate current. This work shows that the time derivation of the peak electrical field influences the switching behaviour. Because of the hole concentration in the space charge region during turn-off of IGBTs the gradient of the electrical field and the time derivation of the peak electrical field during the voltage slope are higher than in the steady off state. This leads to a different behaviour of the miller-capacitance of MOSFET and IGBT. During turn-off of MOSFET the gate current controls the time derivation of the peak electrical field and the voltage slope of the drain-source voltage. In case of IGBT the gate current controls the time derivation of the peak electrical field and indirectly the voltage slope of the collector-emitter voltage. Therefore the turn-off behaviour of MOSFET can be explained by an equivalent circuit. In case of IGBTs it is helpful to analyse the turn-off behaviour by the electrical field strength. Hereby the three-dimensional structure of the IGBT can be reduced to one dimension. With this simplification it is possible to explain different effects during turn-off. These effects are discussed and documented in this PhD thesis by different measurements and simulations with a finite element simulator.

# Inhaltsverzeichnis

|                                                                                    |             |

|------------------------------------------------------------------------------------|-------------|

| <b>Abbildungsverzeichnis</b>                                                       | <b>VIII</b> |

| <b>Tabellenverzeichnis</b>                                                         | <b>XIII</b> |

| <b>Abkürzungsverzeichnis</b>                                                       | <b>XIV</b>  |

| <b>1. Einleitung</b>                                                               | <b>1</b>    |

| <b>2. Aufbau des IGBTs</b>                                                         | <b>4</b>    |

| 2.1. Punch Through IGBT . . . . .                                                  | 6           |

| 2.2. Non Punch Through IGBT . . . . .                                              | 7           |

| 2.3. Field Stop IGBT . . . . .                                                     | 9           |

| 2.4. Trench Gate IGBT und Carrier Stored IGBT . . . . .                            | 10          |

| <b>3. Funktionsweise von IGBTs</b>                                                 | <b>12</b>   |

| 3.1. Einschaltverhalten . . . . .                                                  | 12          |

| 3.2. Ausschaltverhalten . . . . .                                                  | 16          |

| 3.3. Kurzschlussverhalten . . . . .                                                | 18          |

| 3.3.1. Kurzschlussfall I . . . . .                                                 | 19          |

| 3.3.2. Kurzschlussfall II . . . . .                                                | 21          |

| <b>4. IGBT Ansteuerungen</b>                                                       | <b>23</b>   |

| 4.1. Ansteuerungsschaltungen nach dem Prinzip der Widerstandsansteuerung . . . . . | 23          |

| 4.2. Ansteuerungen zur Verbesserung der Schalteigenschaften . . . . .              | 24          |

| 4.2.1. Beeinflussung der Schalttransienten beim Einschalten . . . . .              | 25          |

| 4.2.2. Beeinflussung der Schalttransienten beim Ausschalten . . . . .              | 28          |

| 4.3. Ansteuerungsseitiger Schutz des IGBTs im Kurzschlussfall . . . . .            | 34          |

| 4.3.1. Kurzschlusserkennung . . . . .                                              | 34          |

| 4.3.2. Reduzierung des Kurzschlussstromes . . . . .                                | 36          |

| <b>5. Auswirkungen des Plasmas auf das Ausschaltverhalten von IGBTs</b>            | <b>38</b>   |

| 5.1. Kapazitives Verhalten des IGBTs . . . . .                                     | 43          |

| 5.1.1. Auswirkung auf den Verlauf der Kollektor-Emitter Spannung .                 | 45          |

|                                                                                                           |            |

|-----------------------------------------------------------------------------------------------------------|------------|

| 5.1.2. Auswirkung auf die Überspannung . . . . .                                                          | 47         |

| 5.1.3. Auswirkung des Gatestroms . . . . .                                                                | 48         |

| 5.2. Anstoßen an die Feldstopp-Schicht . . . . .                                                          | 49         |

| 5.2.1. Einfluss des Gatewiderstandes . . . . .                                                            | 52         |

| 5.2.2. Einfluss des Kollektorstromes . . . . .                                                            | 55         |

| 5.2.3. Einfluss der Zwischenkreisspannung . . . . .                                                       | 57         |

| 5.2.4. Einfluss der Sperrsichttemperatur . . . . .                                                        | 59         |

| <b>6. Schaltverhalten des MOSFETs</b>                                                                     | <b>61</b>  |

| 6.1. Allgemeines Schaltverhalten des MOSFETs . . . . .                                                    | 61         |

| 6.2. Kapazitives Verhalten des MOSFETs . . . . .                                                          | 63         |

| 6.2.1. Verlauf der Drain-Source Spannung . . . . .                                                        | 64         |

| 6.2.2. Auswirkung auf die Überspannung . . . . .                                                          | 66         |

| 6.2.3. Auswirkung des Gatestroms . . . . .                                                                | 66         |

| <b>7. Auswirkung der Millerkapazität auf das Ausschaltverhalten von IGBTs</b>                             | <b>68</b>  |

| 7.1. Vergleich der Millerkapazität beim MOSFET und beim IGBT (Self Turn Off Effekt) . . . . .             | 68         |

| 7.1.1. Der Self Turn Off Effekt beim Abschalten von IGBTs . . . . .                                       | 71         |

| 7.1.2. Der Self Turn Off Effekt beim Kurzschlussfall II . . . . .                                         | 75         |

| 7.2. Vergleich zwischen einer einfachen Widerstandsansteuerung und einer Widerstandsumschaltung . . . . . | 79         |

| 7.3. Einfluss der Temperatur auf das Abschaltverhalten von IGBTs . . . . .                                | 83         |

| 7.3.1. Messungen und Simulationen bei unterschiedlichen Sperrsichttemperaturen . . . . .                  | 84         |

| 7.3.2. Analytische Herleitung bei unterschiedlichen Sperrsichttemperaturen . . . . .                      | 89         |

| 7.4. Stromfehlverteilung beim Abschalten parallelgeschalteter Feldstopp-IGBTs . . . . .                   | 94         |

| 7.5. Konsequenzen für IGBT Ansteuerungsschaltungen . . . . .                                              | 99         |

| <b>8. Zusammenfassung</b>                                                                                 | <b>101</b> |

| <b>Anhang</b>                                                                                             | <b>104</b> |

| <b>A. Messung</b>                                                                                         | <b>104</b> |

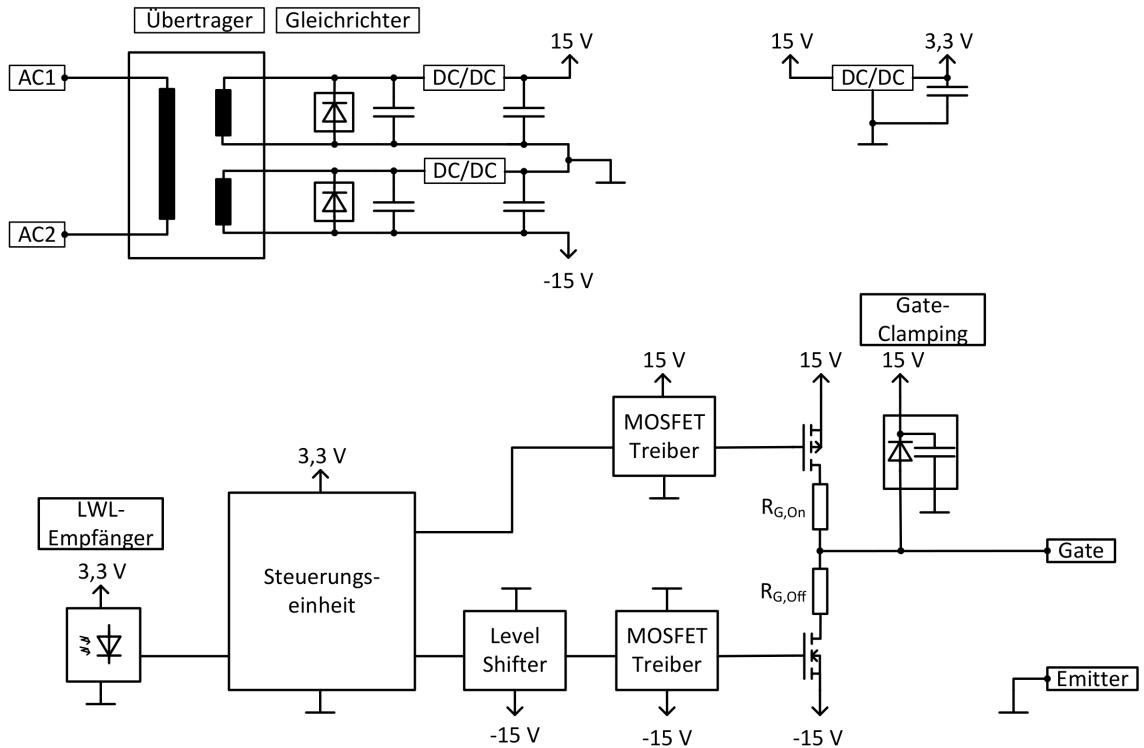

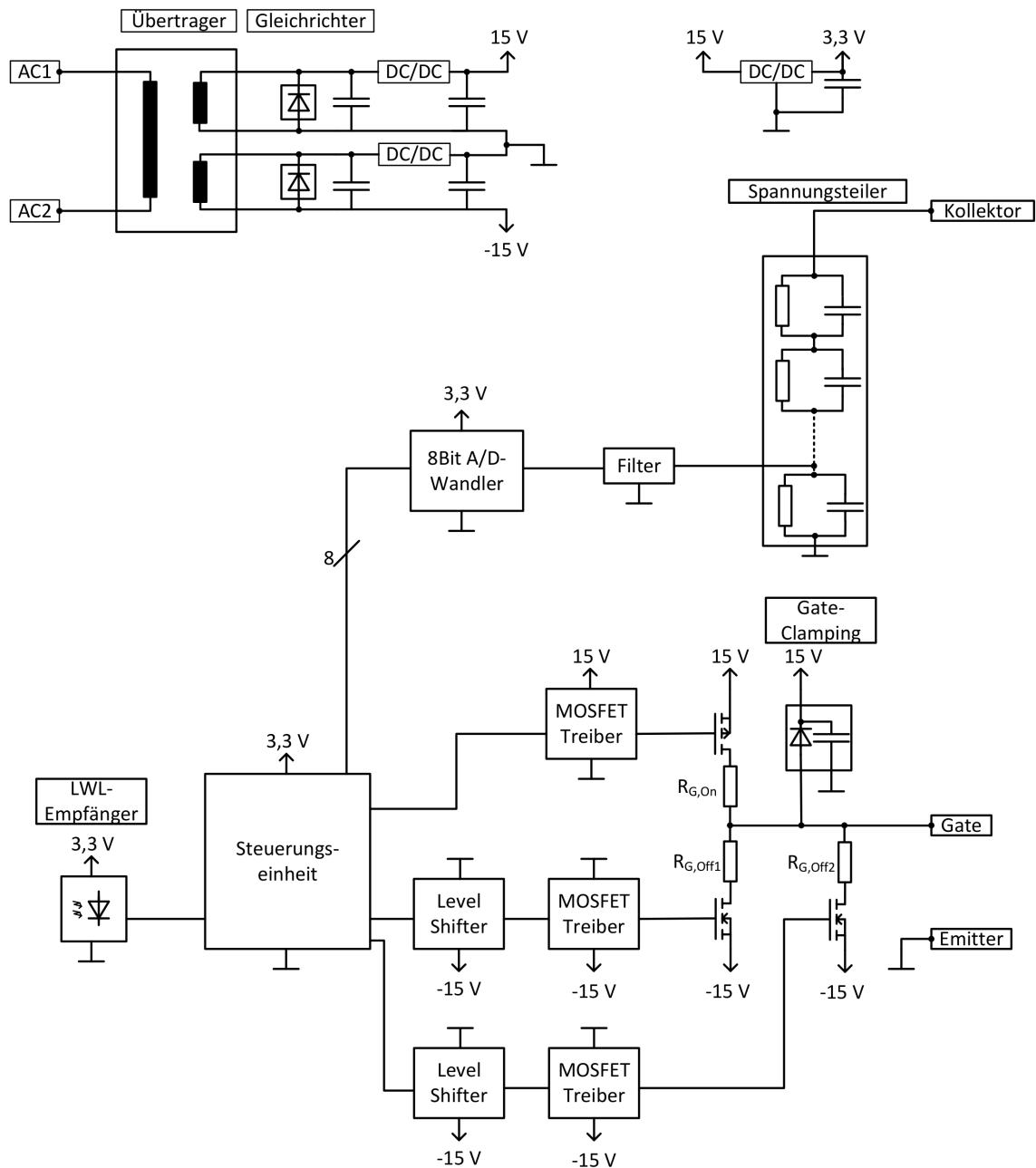

| A.1. Treiberschaltung der einfachen Widerstandsansteuerung . . . . .                                      | 104        |

| A.2. Treiberschaltung der Widerstandsumschaltung . . . . .                                                | 105        |

|                                                                                         |            |

|-----------------------------------------------------------------------------------------|------------|

| <b>B. Simulation</b>                                                                    | <b>107</b> |

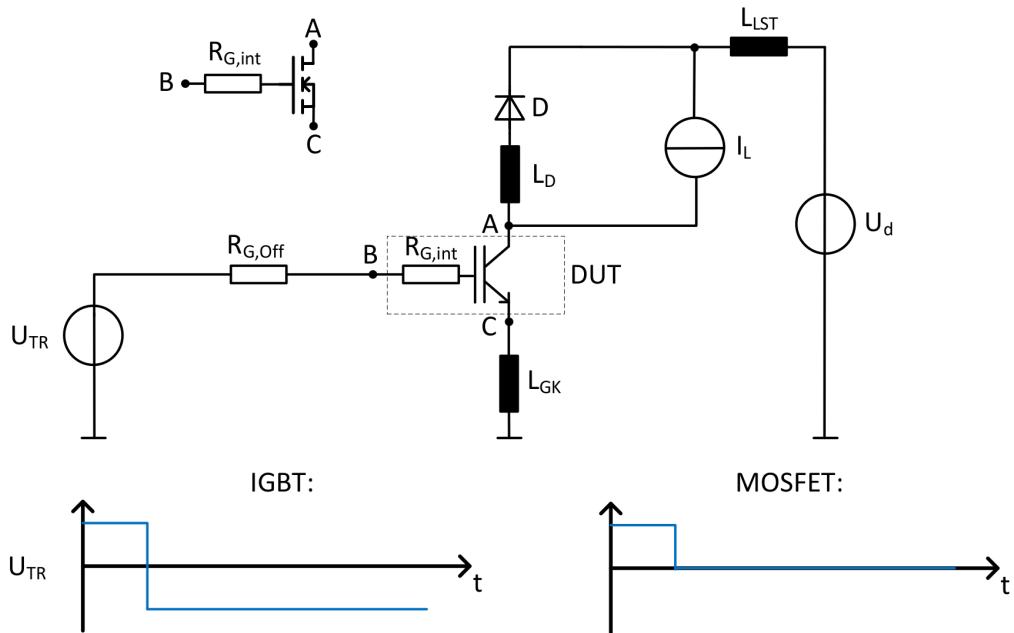

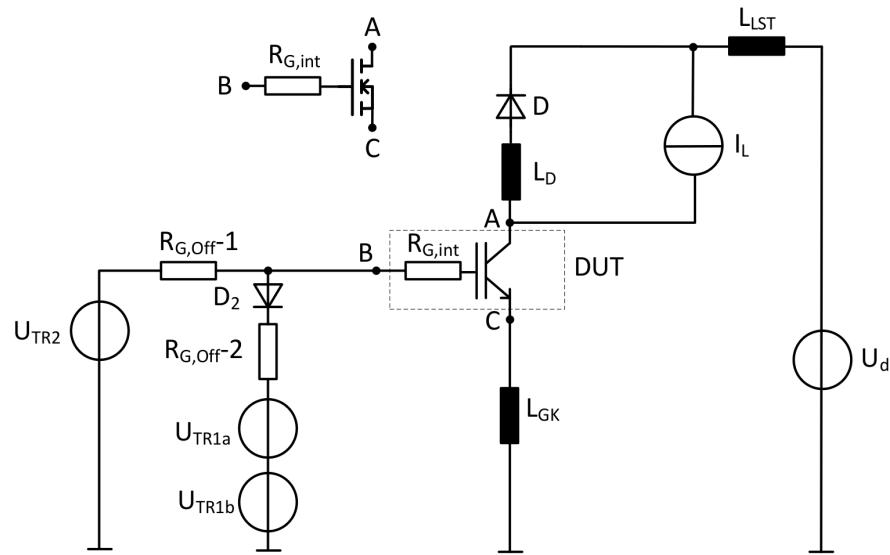

| B.1. Schaltbild für das Ausschaltverhalten mit einfacher Widerstandssteuerung . . . . . | 107        |

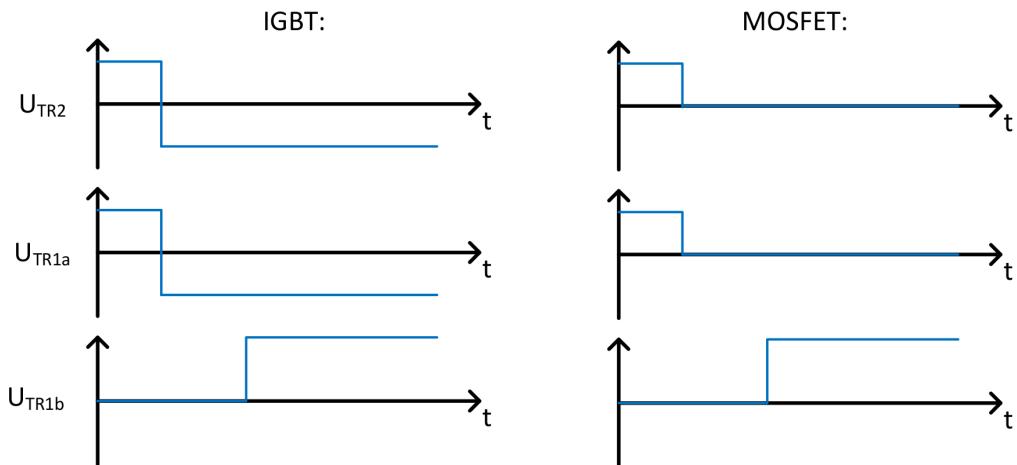

| B.2. Schaltbild für das Ausschaltverhalten mit Widerstandsumschaltung . . . . .         | 108        |

| B.3. Schaltbild für die Kurzschlussimulation . . . . .                                  | 109        |

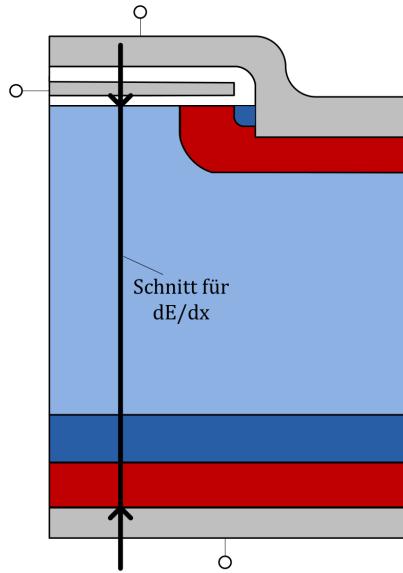

| B.4. Schnitt durch eine IGBT-Zelle . . . . .                                            | 110        |

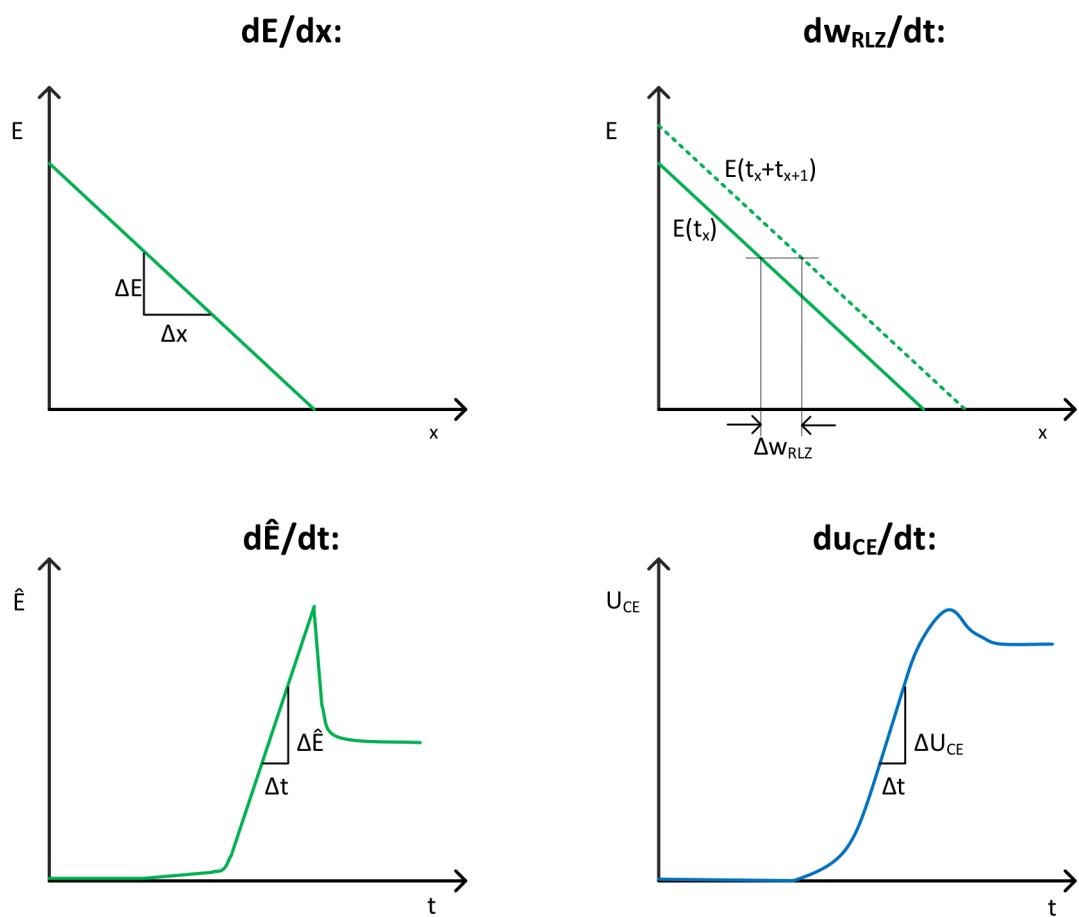

| B.5. Extraktion von Kenngrößen aus Simulationen . . . . .                               | 111        |

| <b>Literaturverzeichnis</b>                                                             | <b>113</b> |

| <b>Thesen</b>                                                                           | <b>120</b> |

| <b>Eidesstattliche Erklärung</b>                                                        | <b>122</b> |

# Abbildungsverzeichnis

|                                                                                                                               |    |

|-------------------------------------------------------------------------------------------------------------------------------|----|

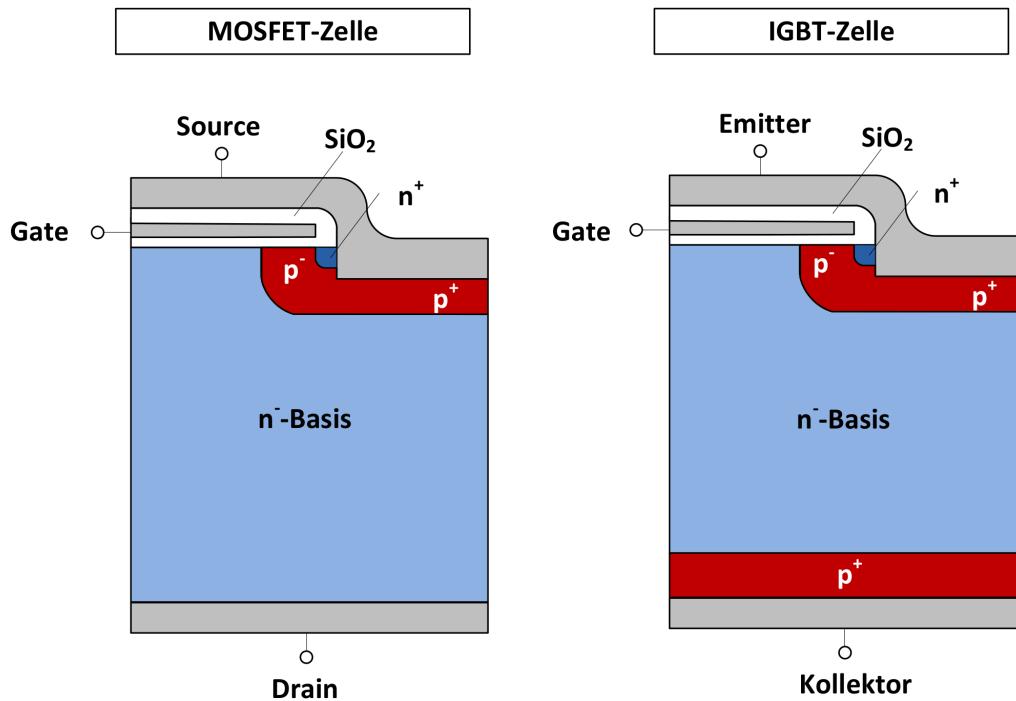

| 2.1. Querschnitt einer MOSFET-Zelle und einer IGBT-Zelle . . . . .                                                            | 4  |

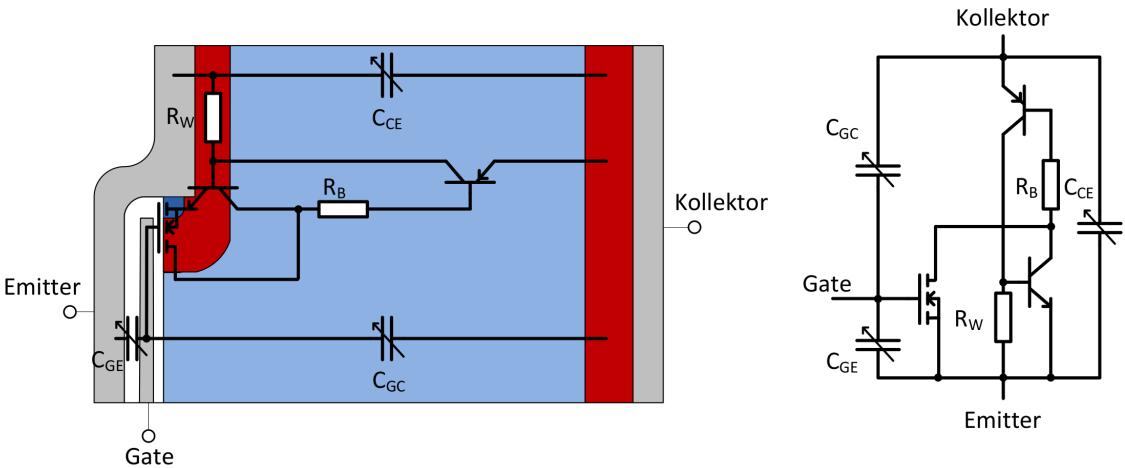

| 2.2. Ersatzschaltbild mit parasitären Elementen eines IGBTs . . . . .                                                         | 6  |

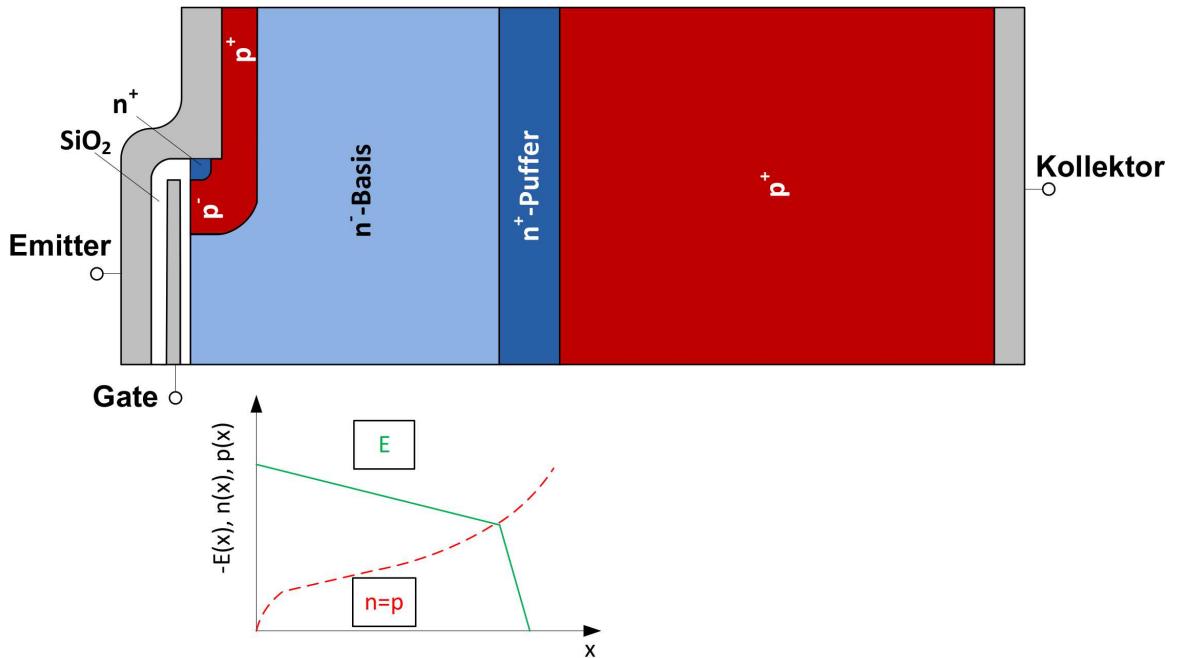

| 2.3. Querschnitt eines PT-IGBT mit Feldverlauf und Ladungsträgerkonzentration . . . . .                                       | 7  |

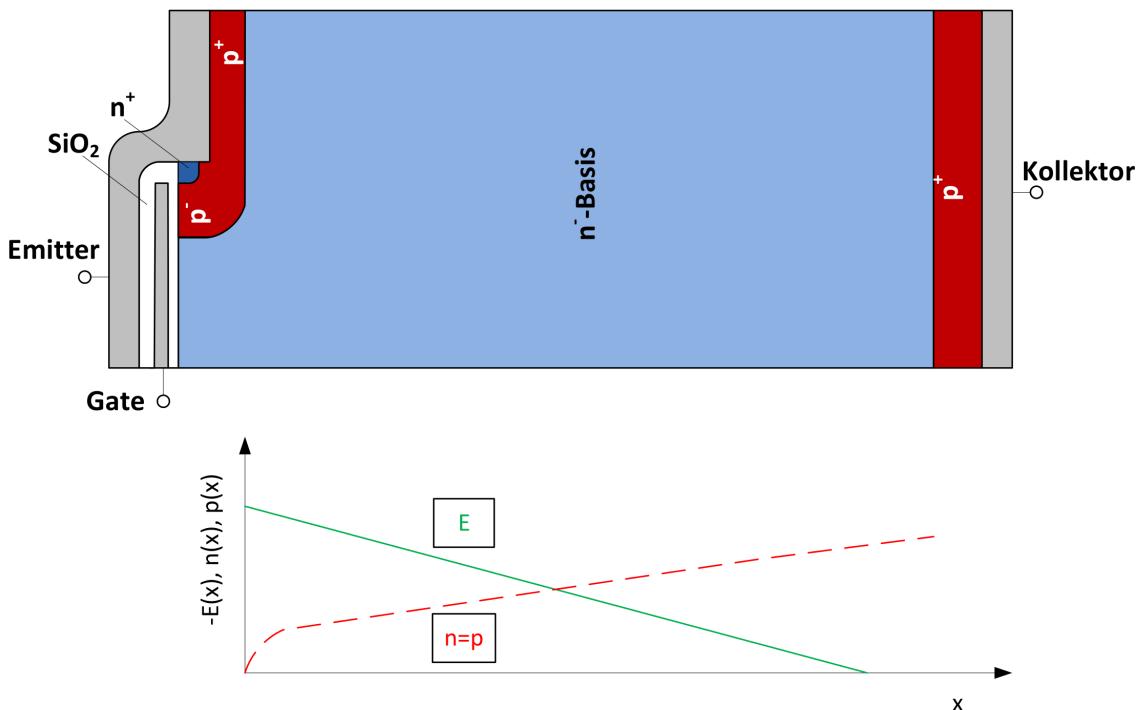

| 2.4. Querschnitt eines NPT-IGBT mit Feldverlauf und Ladungsträgerkonzentration . . . . .                                      | 8  |

| 2.5. Querschnitt eines FS-IGBT mit Feldverlauf und Ladungsträgerkonzentration . . . . .                                       | 9  |

| 2.6. Querschnitt einer Trench Gate Zelle und einer Carrier Stored Zelle . .                                                   | 11 |

| 3.1. Einphasiger Spannungzwischenkreisumrichter mit induktiver Last als Tiefsetzsteller . . . . .                             | 12 |

| 3.2. Funktionsweise einer NPT-Zelle . . . . .                                                                                 | 13 |

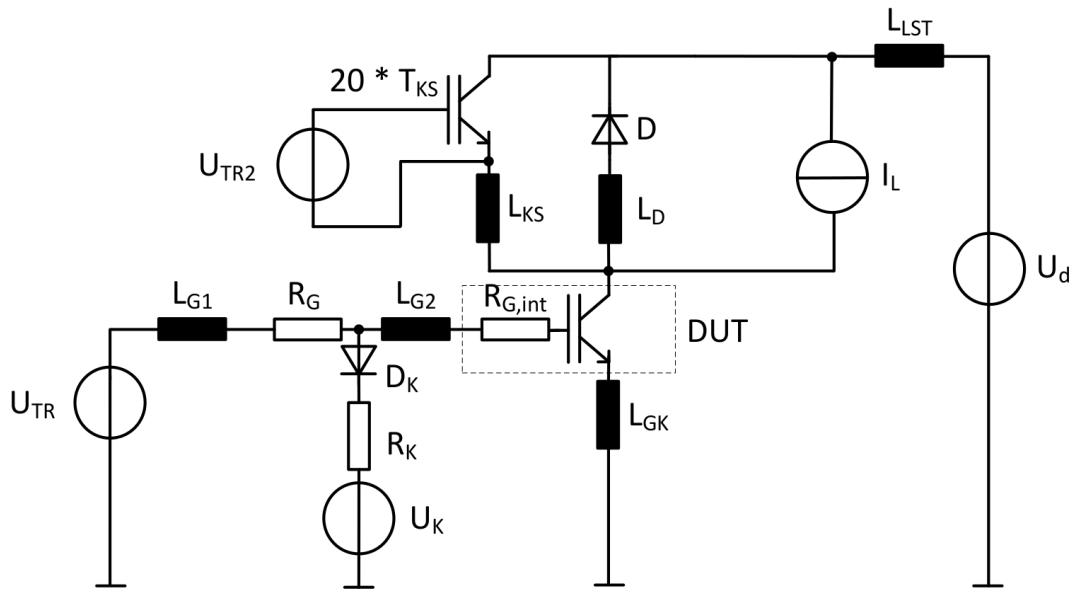

| 3.3. Messaufbau mit parasitären Elementen . . . . .                                                                           | 14 |

| 3.4. Einschaltverhalten eines 6,5 kV - 600 A IGBTs . . . . .                                                                  | 14 |

| 3.5. Ausschaltverhalten eines 6,5 kV - 600 A IGBTs . . . . .                                                                  | 17 |

| 3.6. Erweiterung des einphasigen Spannungzwischenkreisumrichters für Kurzschlussmessungen . . . . .                           | 19 |

| 3.7. Kurzschlussfall I eines 4,5 kV - 1200 A IGBTs . . . . .                                                                  | 20 |

| 3.8. Kurzschlussfall II eines 4,5 kV - 1200 A IGBTs . . . . .                                                                 | 21 |

| 4.1. Einfache Ansteuerungsschaltungen . . . . .                                                                               | 24 |

| 4.2. Ansteuerung mit einer H-Brücke nach [37, 42, 59] . . . . .                                                               | 24 |

| 4.3. Ansteuerung zur Reduzierung der Überstromspitze über eine externe Kapazität nach [19] und [30] . . . . .                 | 25 |

| 4.4. Ansteuerung zur Reduzierung der Überstromspitze mit Widerstands-umschaltung und Stromquelle nach [55] und [32] . . . . . | 26 |

| 4.5. Ansteuerung zur Reduzierung der Überstromspitze mit variabler Gatespannung nach [13] und [20] . . . . .                  | 26 |

| 4.6. Ansteuerung zur Reduzierung des Stromgradienten beim Einschalten nach [23] . . . . .                                     | 27 |

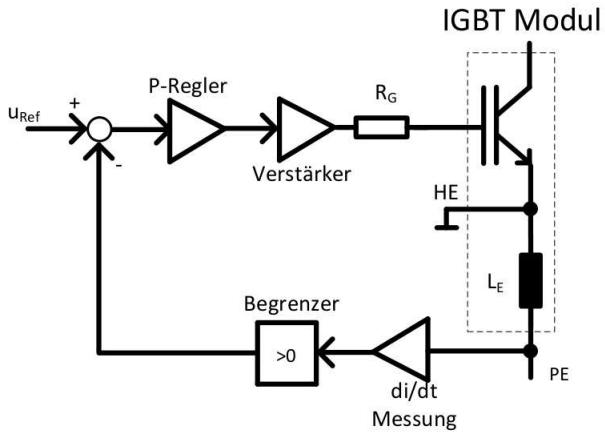

| 4.7. Geregelte Ansteuerung zur Reduzierung des Stromgradienten beim Einschalten nach [17] . . . . .                           | 28 |

|                                                                                                                                       |    |

|---------------------------------------------------------------------------------------------------------------------------------------|----|

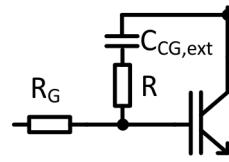

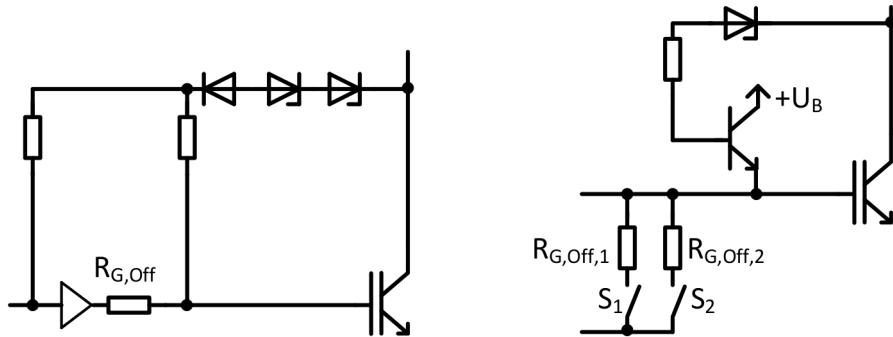

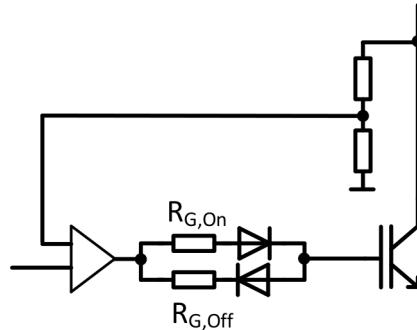

| 4.8. Ansteuerung zur Reduzierung des Spannungsgradienten nach [23] . . . . .                                                          | 29 |

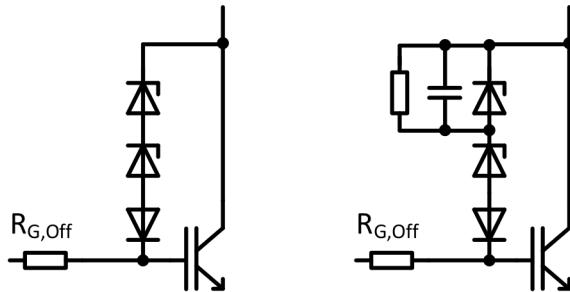

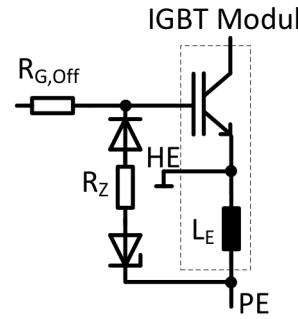

| 4.9. Aktive Überspannungsbegrenzungen mit Zenerdioden nach [59, 61]<br>und [50] . . . . .                                             | 29 |

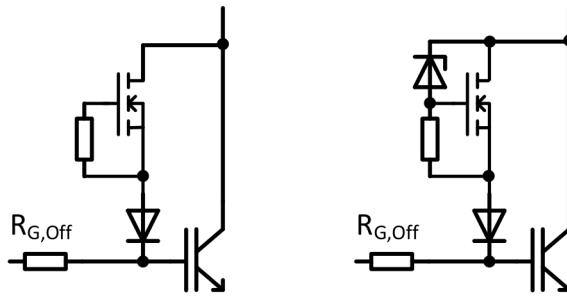

| 4.10. Aktive Überspannungsbegrenzungen mit MOSFET im Avalanche-Durchbruch und Verstärkung einer Zenerdiode mit MOSFET [47] . . . . .  | 30 |

| 4.11. Aktive Überspannungsbegrenzung mit Zenerdioden mit einer Widerstandsumschaltung nach [9] . . . . .                              | 30 |

| 4.12. Aktive Überspannungsbegrenzungen mit Zenerdioden und aktiver Verstärkung nach [49] und [9] . . . . .                            | 31 |

| 4.13. Aktive Überspannungsbegrenzung mit Spannungsteiler und aktiver Verstärkung nach [2] . . . . .                                   | 31 |

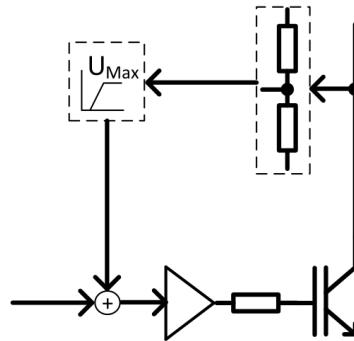

| 4.14. Aktive Überspannungsbegrenzung mit Erfassung der Kollektor-Emitter Spannung und aktiver Verstärkung nach [10] . . . . .         | 32 |

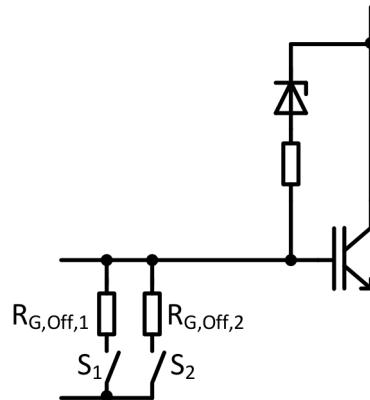

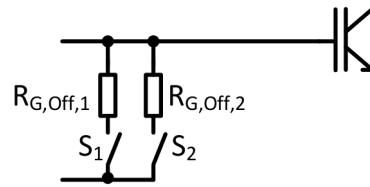

| 4.15. Überspannungsreduzierung mit Widerstandsumschaltung . . . . .                                                                   | 32 |

| 4.16. Ansteuerung zur Reduzierung des Stromgradienten beim Ausschalten nach [23] . . . . .                                            | 33 |

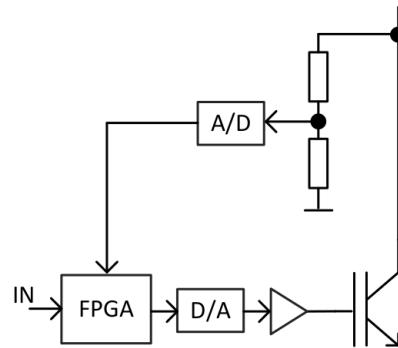

| 4.17. Aktive Überspannungsbegrenzung mit digitaler Regelung der Kollektor-Emitter Spannung nach [21, 22] . . . . .                    | 33 |

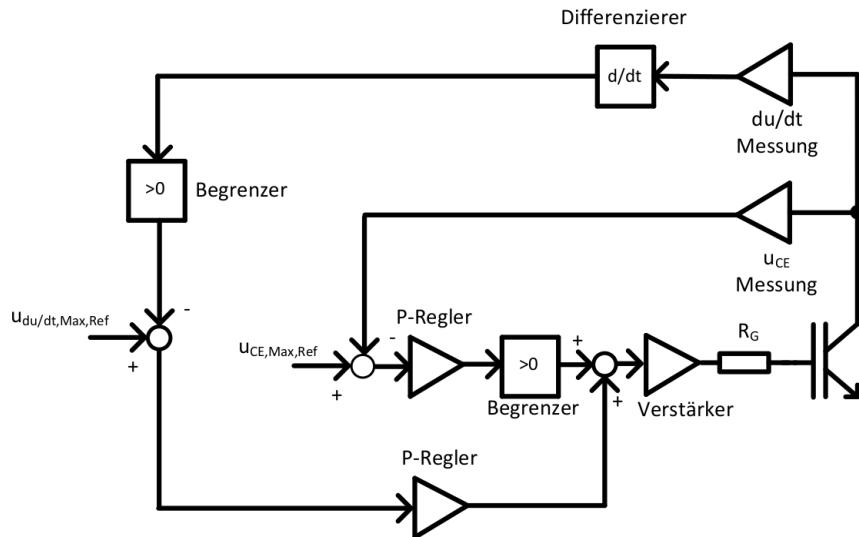

| 4.18. Geregelte Ansteuerung zur Regelung der Spannungsanstiegsgeschwindigkeit und aktiver Überspannungsbegrenzung nach [17] . . . . . | 34 |

| 4.19. Kurzschlusserkennung mit Abkoppeldiode nach [61] und [11] . . . . .                                                             | 35 |

| 4.20. Kurzschlusserkennung anhand der Gate-Emitter Spannung nach [31] .                                                               | 36 |

| 4.21. Passive Begrenzung der dynamischen Überstromspitze nach [59, 61] .                                                              | 37 |

| 4.22. Aktive Begrenzung des Kurzschlussstromes nach [39] . . . . .                                                                    | 37 |

| <br>                                                                                                                                  |    |

| 5.1. Querschnitt einer IGBT-Zelle beim Abschalten – Gate Kanal geschlossen . . . . .                                                  | 39 |

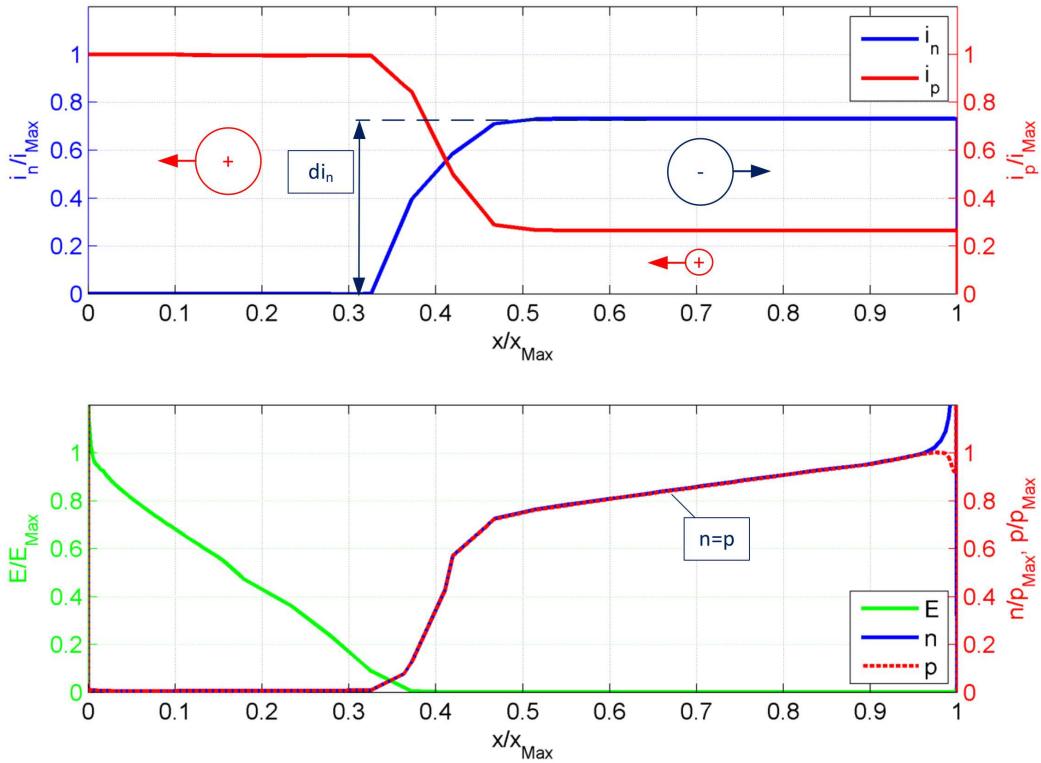

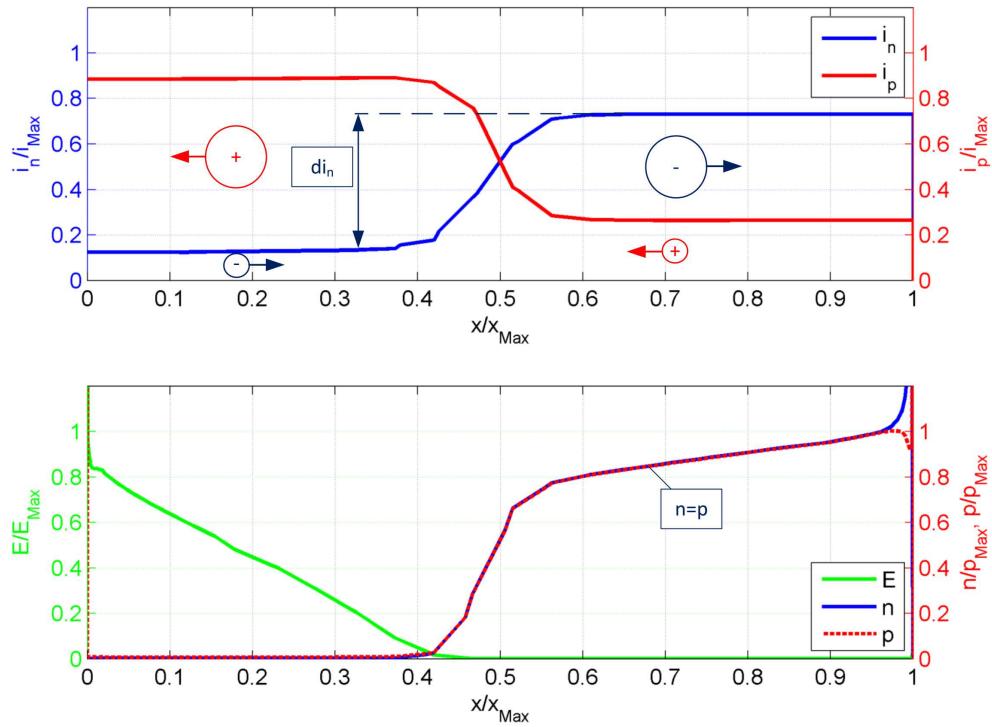

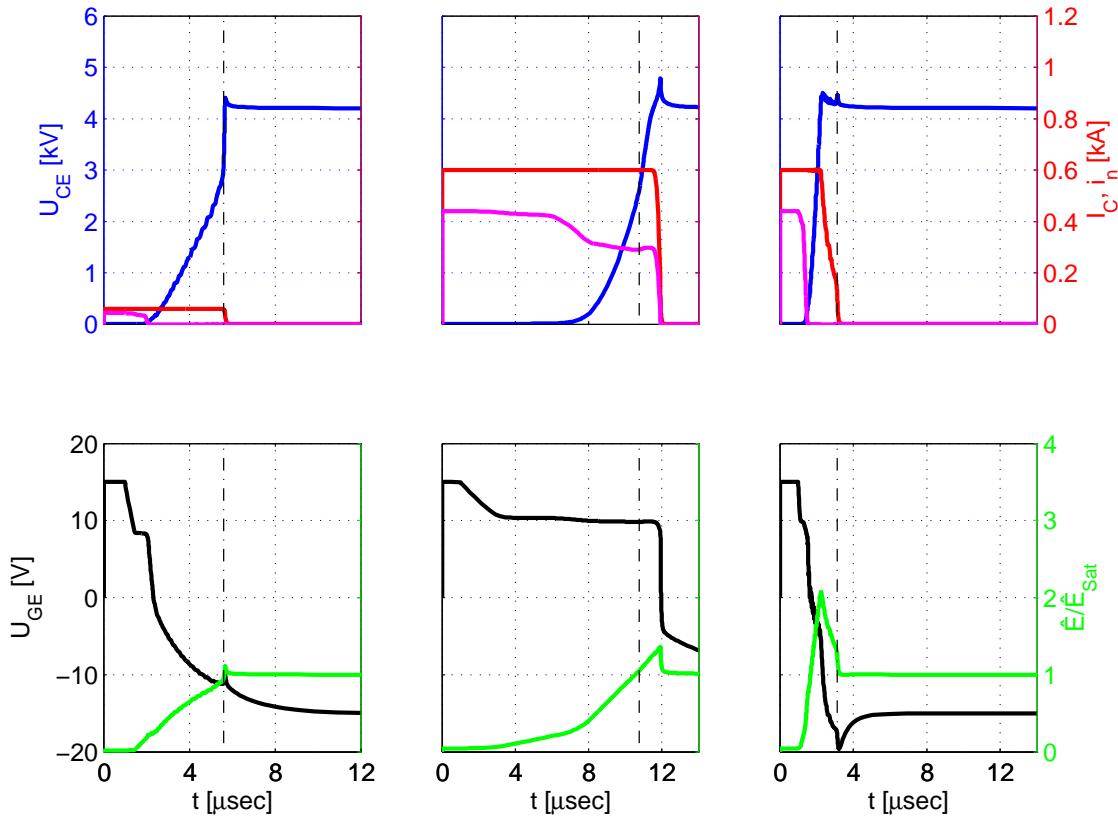

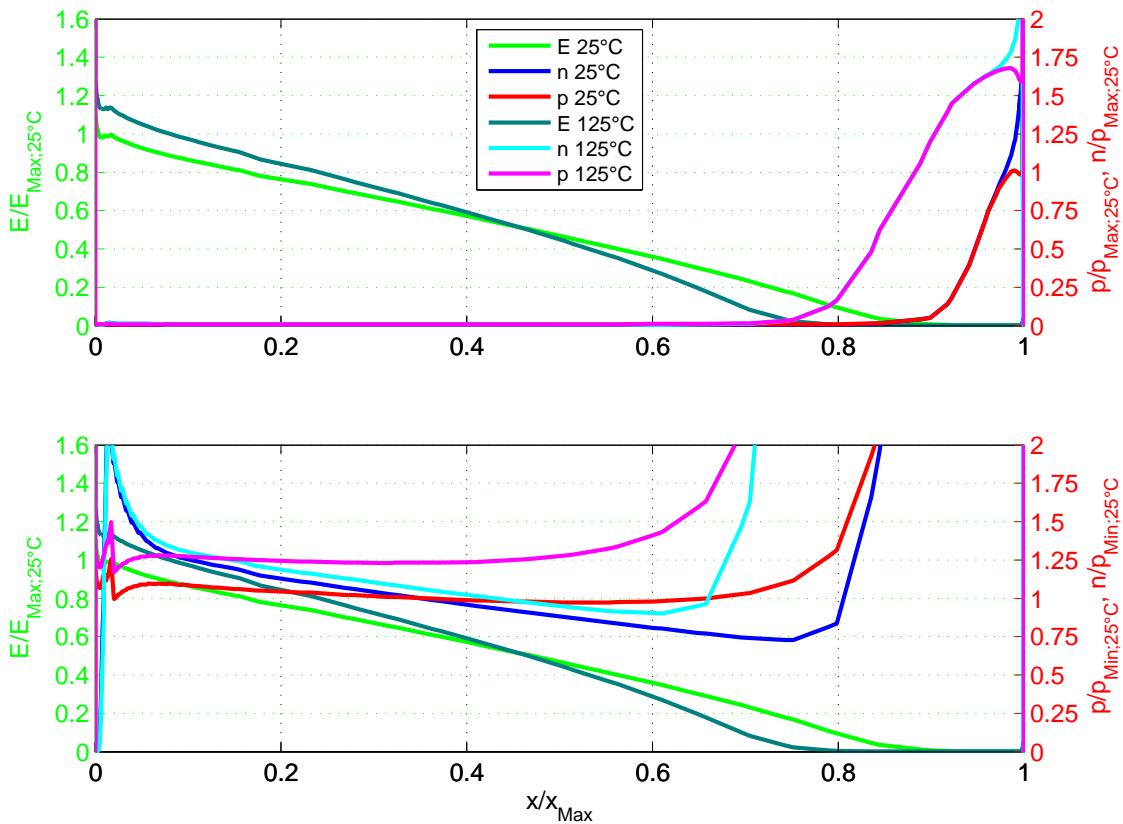

| 5.2. Simulation eines 6,5 kV IGBT bei 600 A und großen Gateentladestrom                                                               | 41 |

| 5.3. Querschnitt einer IGBT-Zelle während des Abschaltens . . . . .                                                                   | 42 |

| 5.4. Querschnitt einer IGBT-Zelle beim Abschalten – Gate Kanal offen .                                                                | 43 |

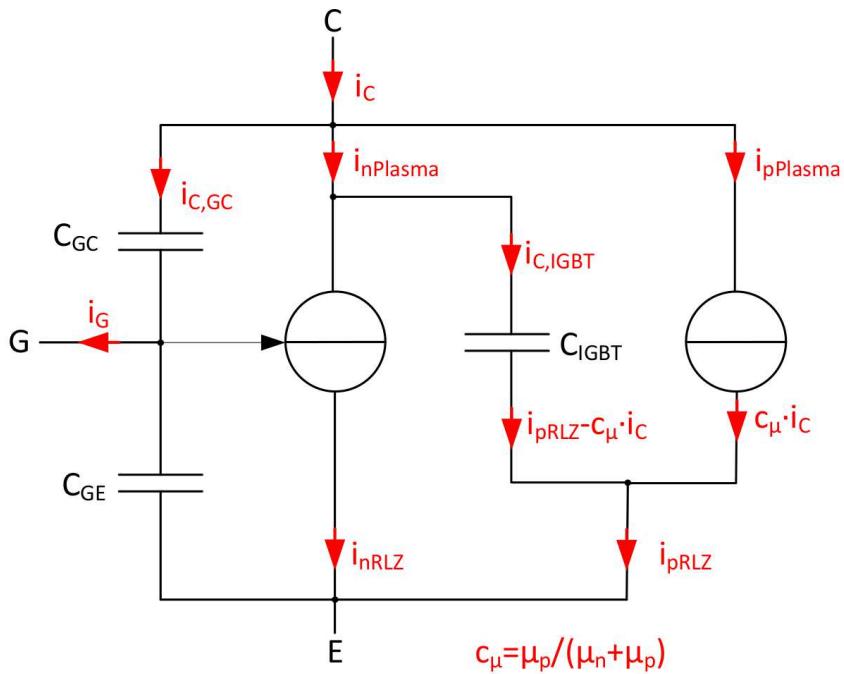

| 5.5. Kapazitives Ersatzschaltbild eines IGBTs mit gesteuerter Stromquelle                                                             | 44 |

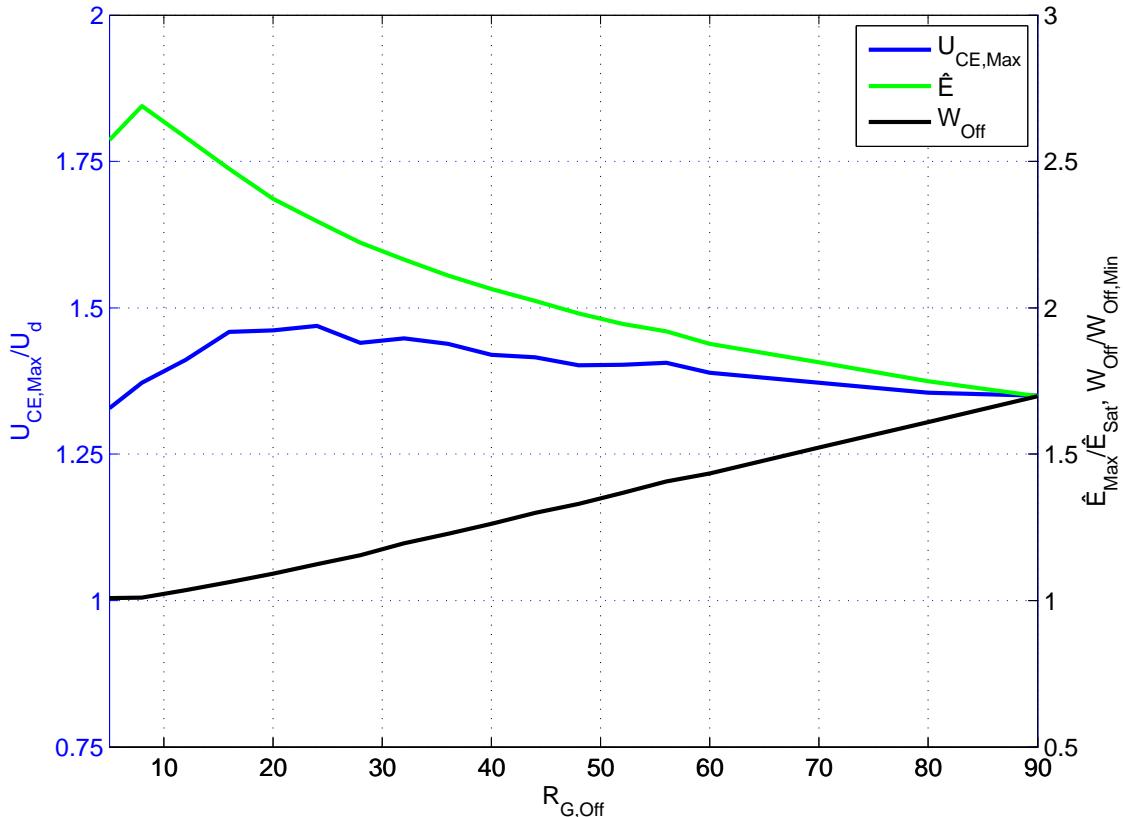

| 5.6. Wichtige Kenngrößen beim Abschalten von IGBTs. Simulation eines 6,5 kV IGBTs mit verschiedenen Gatewiderständen . . . . .        | 48 |

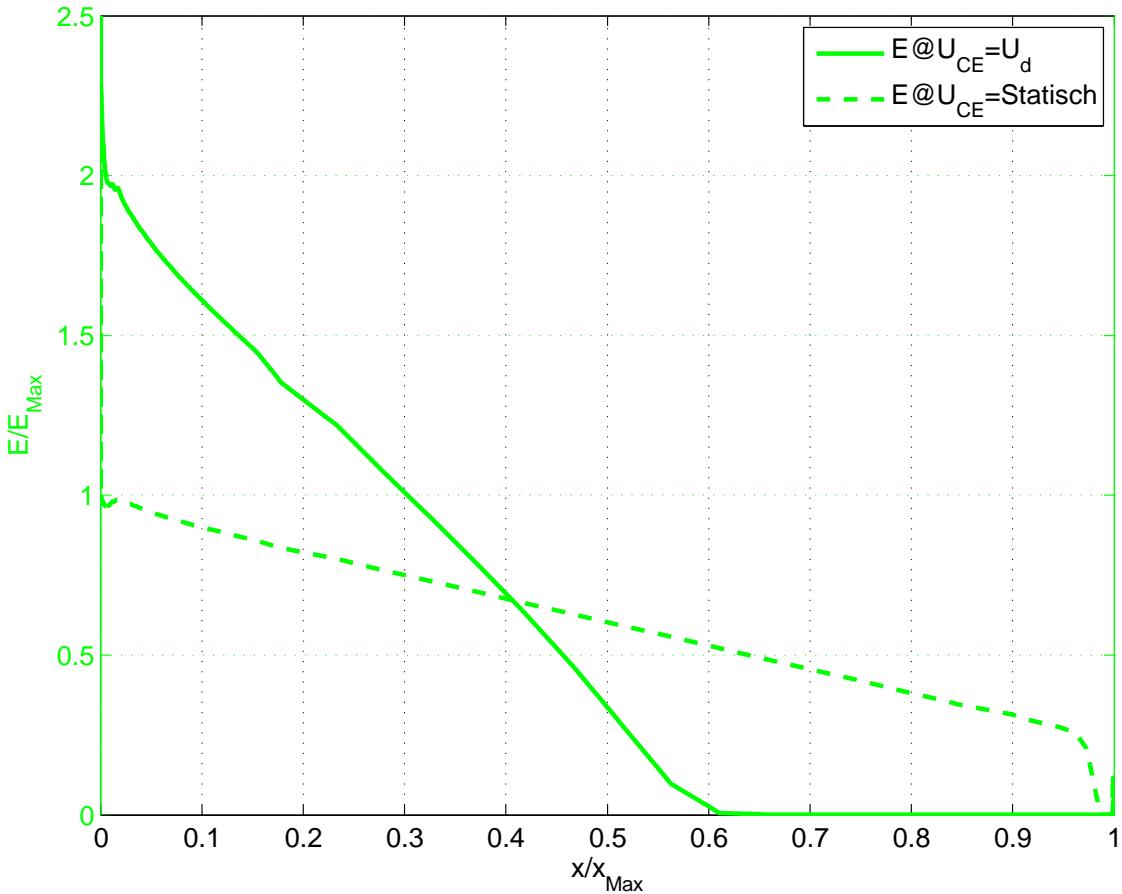

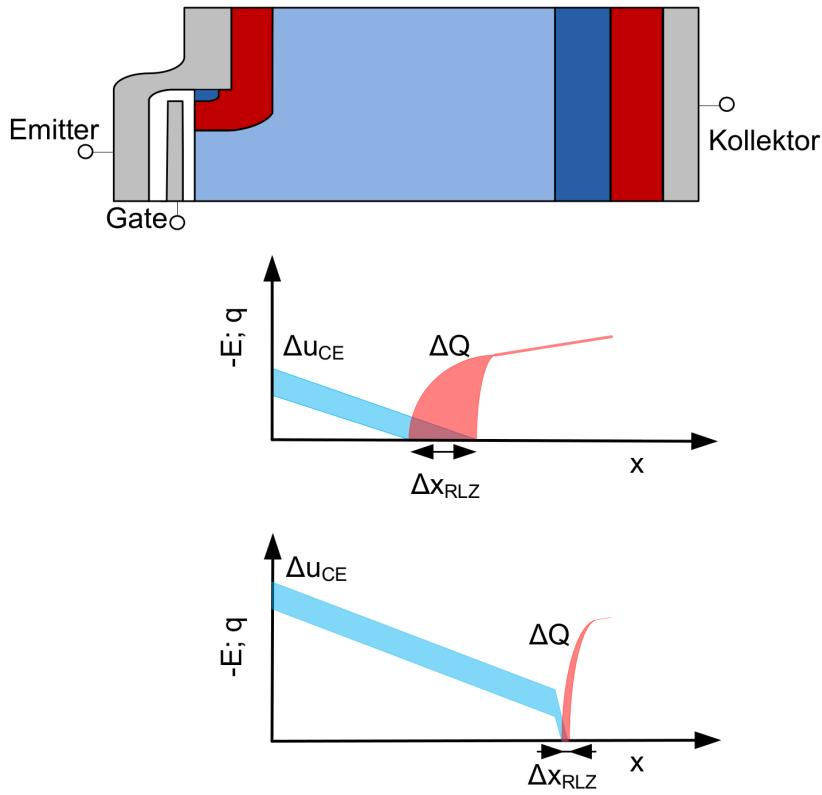

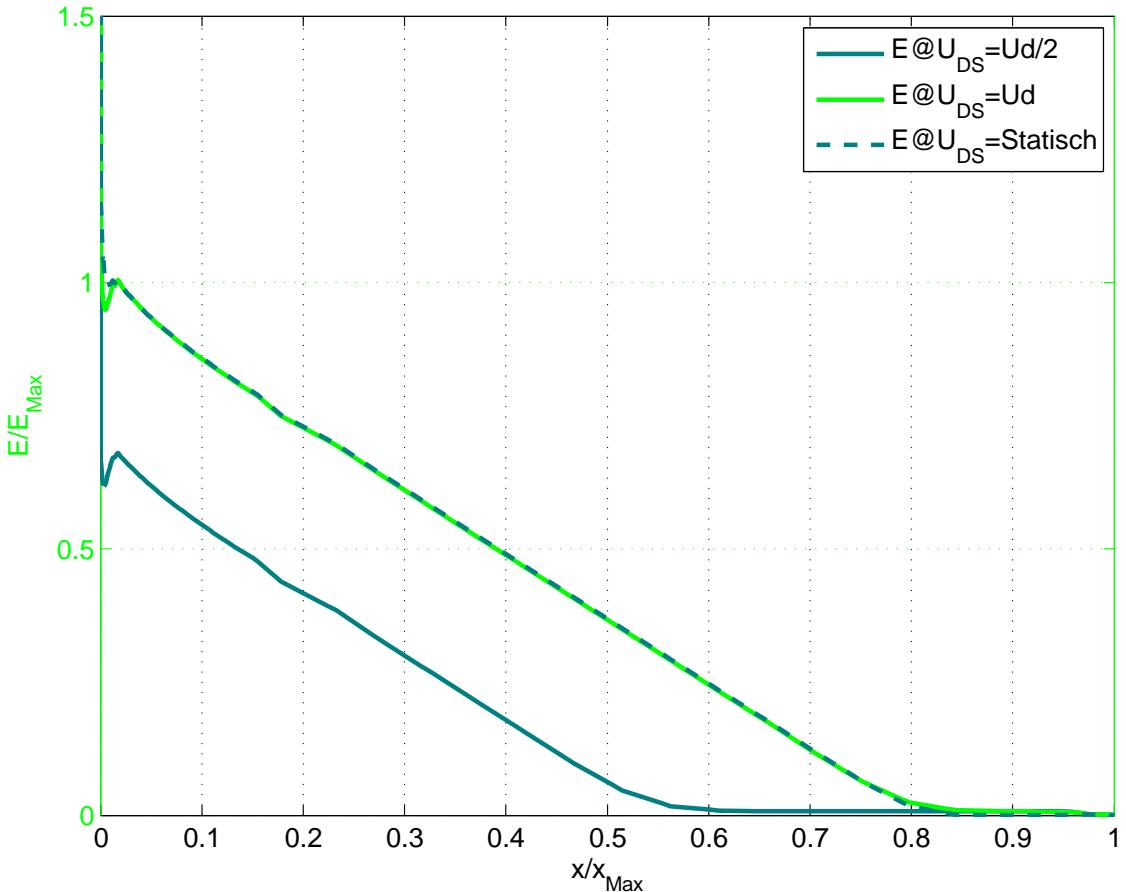

| 5.7. FS-IGBT: Anstoßen an die Feldstopp-Schicht während des Abschaltvorgangs . . . . .                                                | 50 |

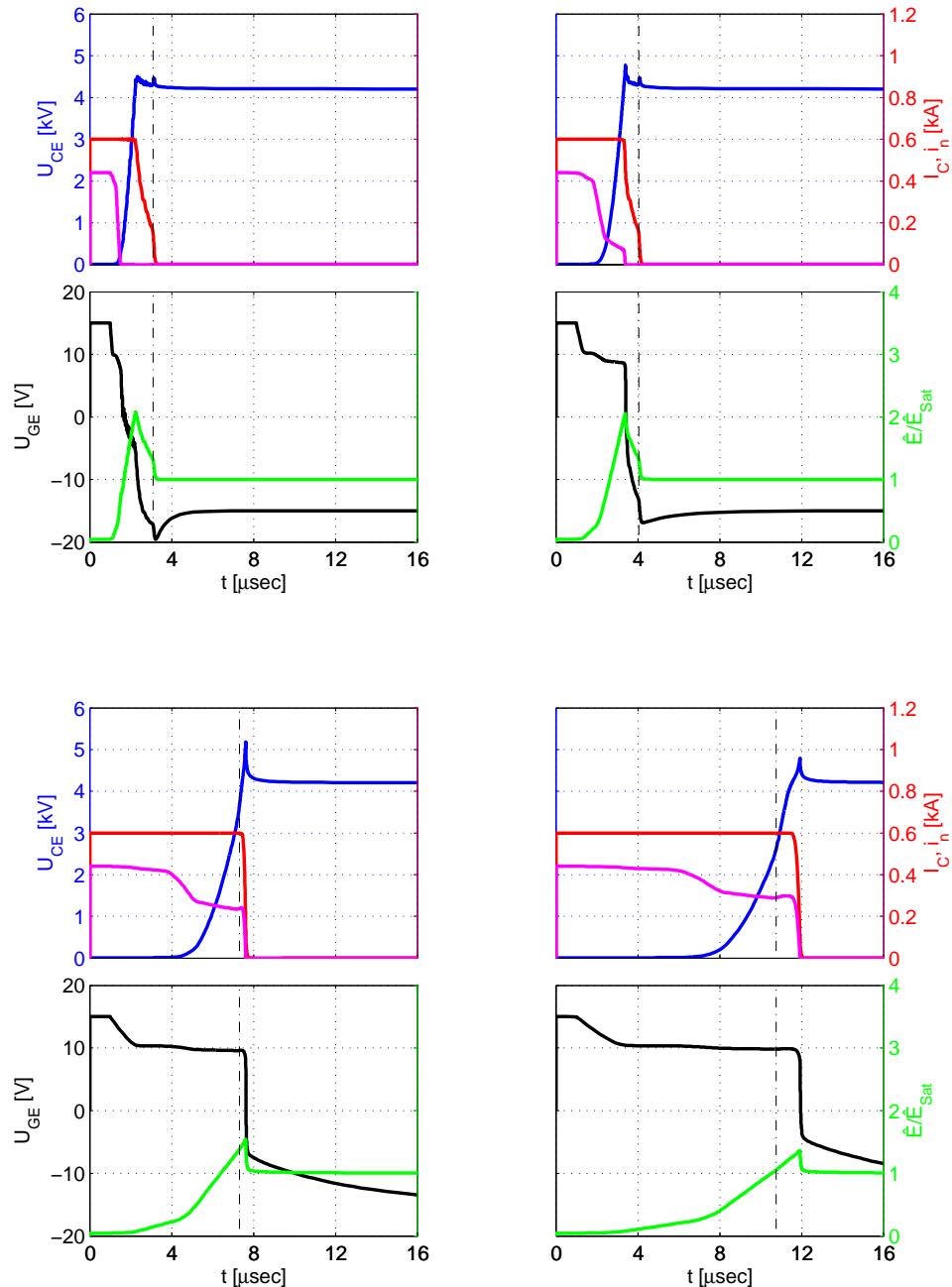

| 5.8. Simulation: Abschaltverhalten eines Feldstopp-IGBTs. Verschiedene Anstoßzeitpunkte an die FS-Schicht . . . . .                   | 52 |

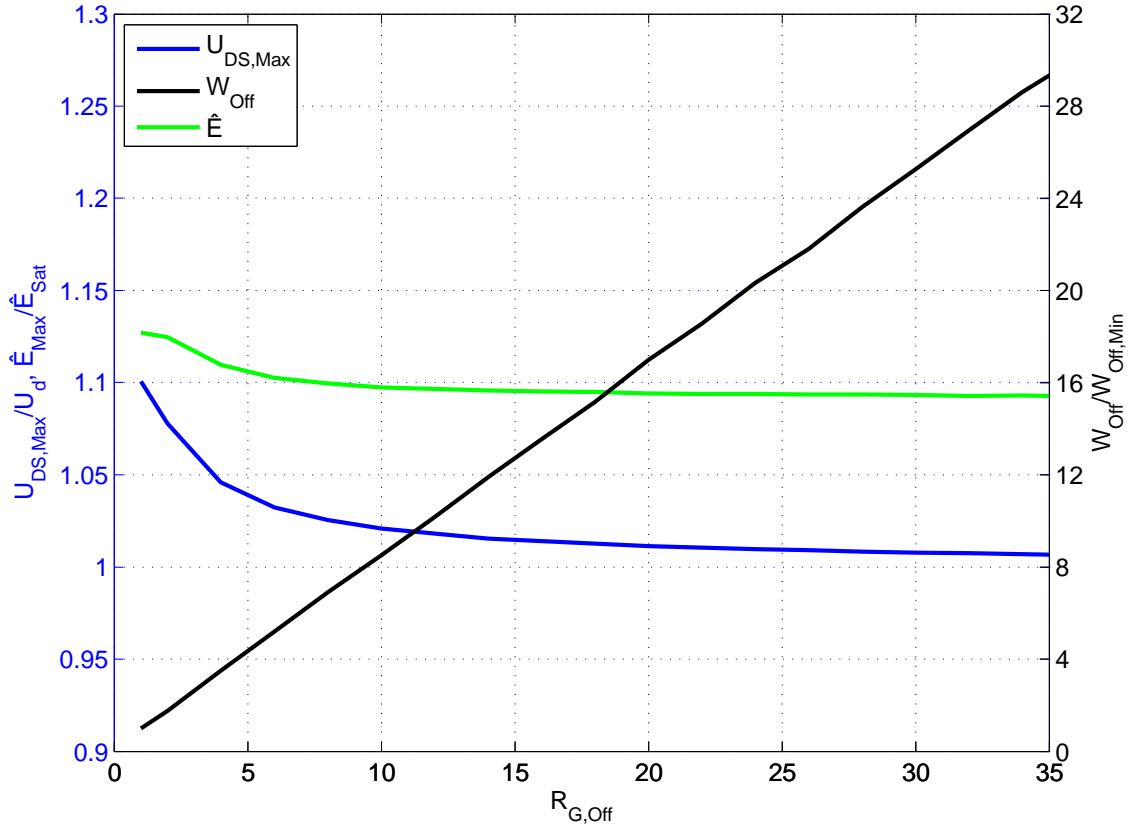

| 5.9. Simulation: Abschaltverhalten eines Feldstopp-IGBTs mit verschiedenen Gatewiderständen . . . . .                                 | 54 |

|                                                                                                                                                                                                          |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

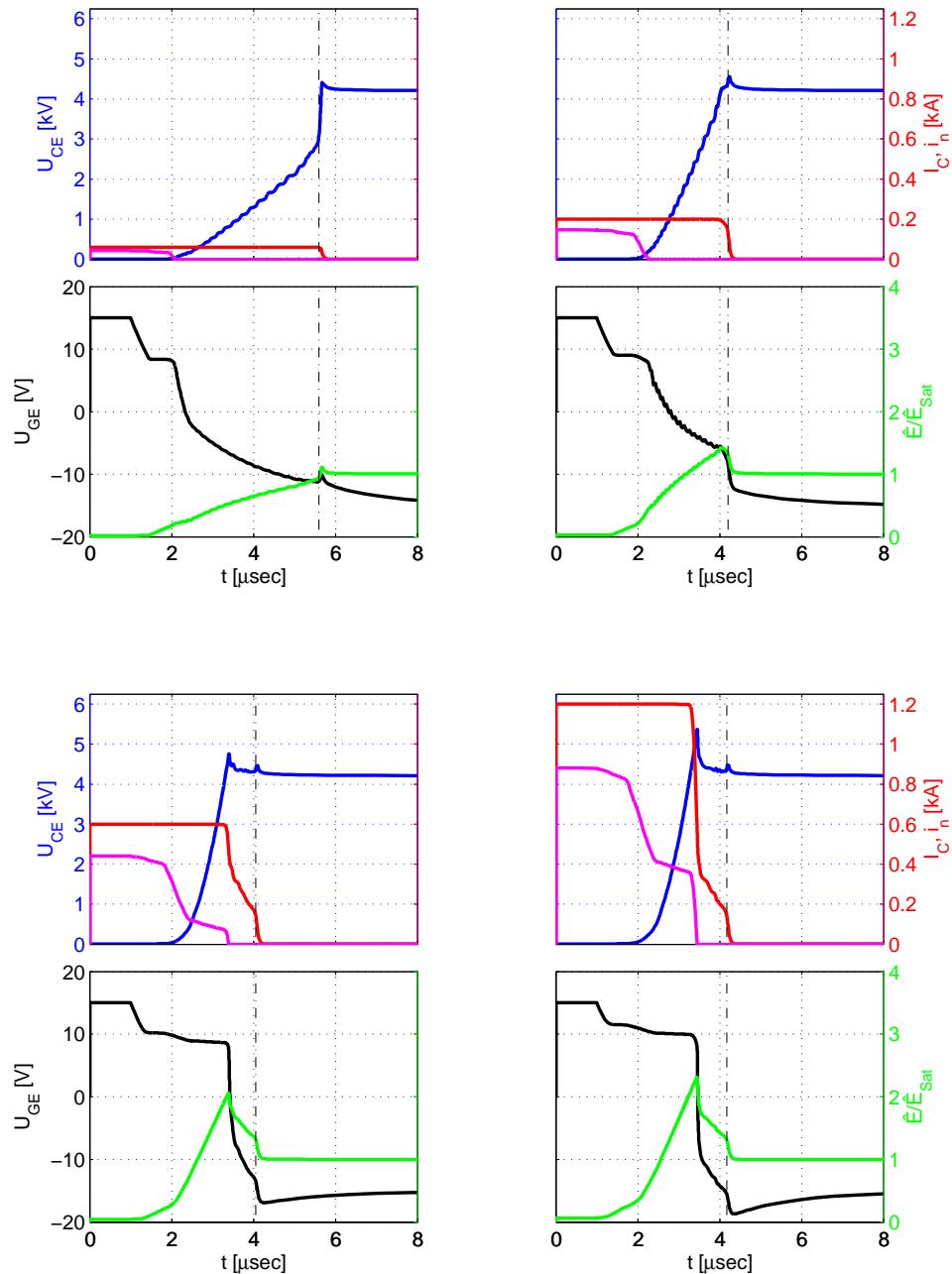

| 5.10. Simulation: Abschaltverhalten eines Feldstopp-IGBTs mit verschiedenen Kollektorströmen . . . . .                                                                                                   | 57 |

| 5.11. Simulation: Abschaltverhalten eines Feldstopp-IGBTs mit verschiedenen Zwischenkreisspannungen . . . . .                                                                                            | 58 |

| 5.12. Simulation: Abschaltverhalten eines Feldstopp-IGBTs mit verschiedenen Sperrsichttemperaturen . . . . .                                                                                             | 59 |

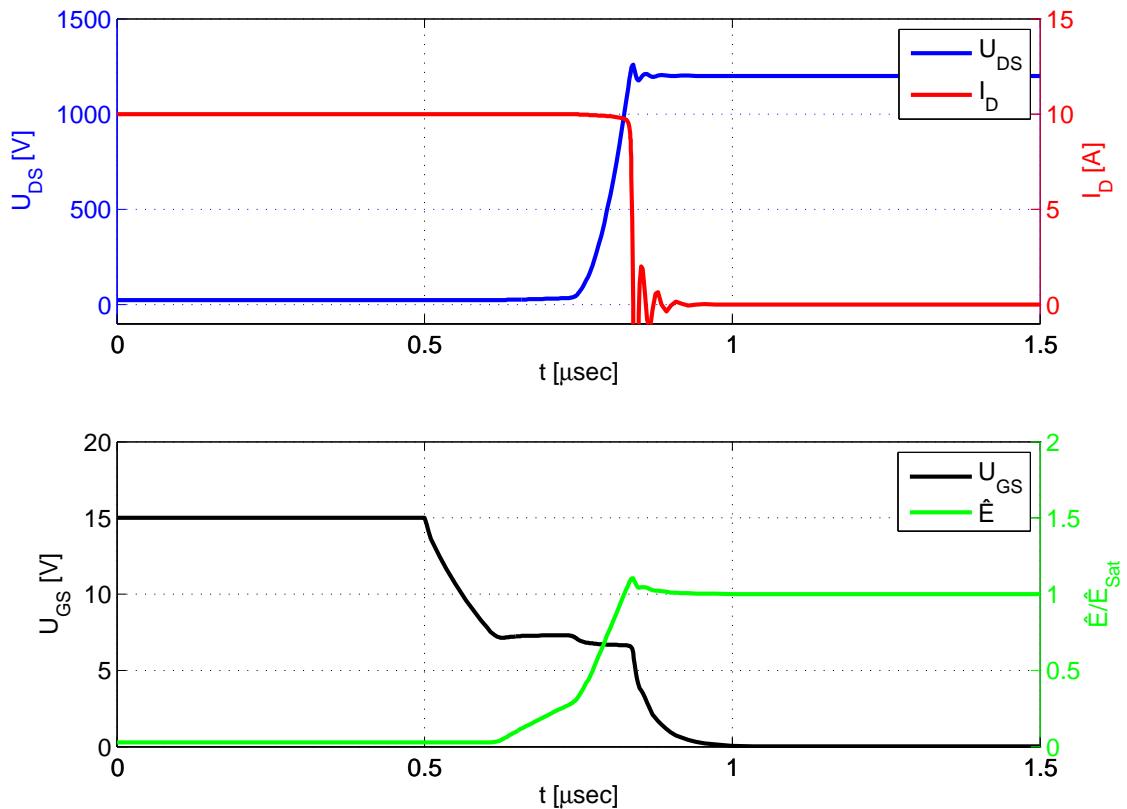

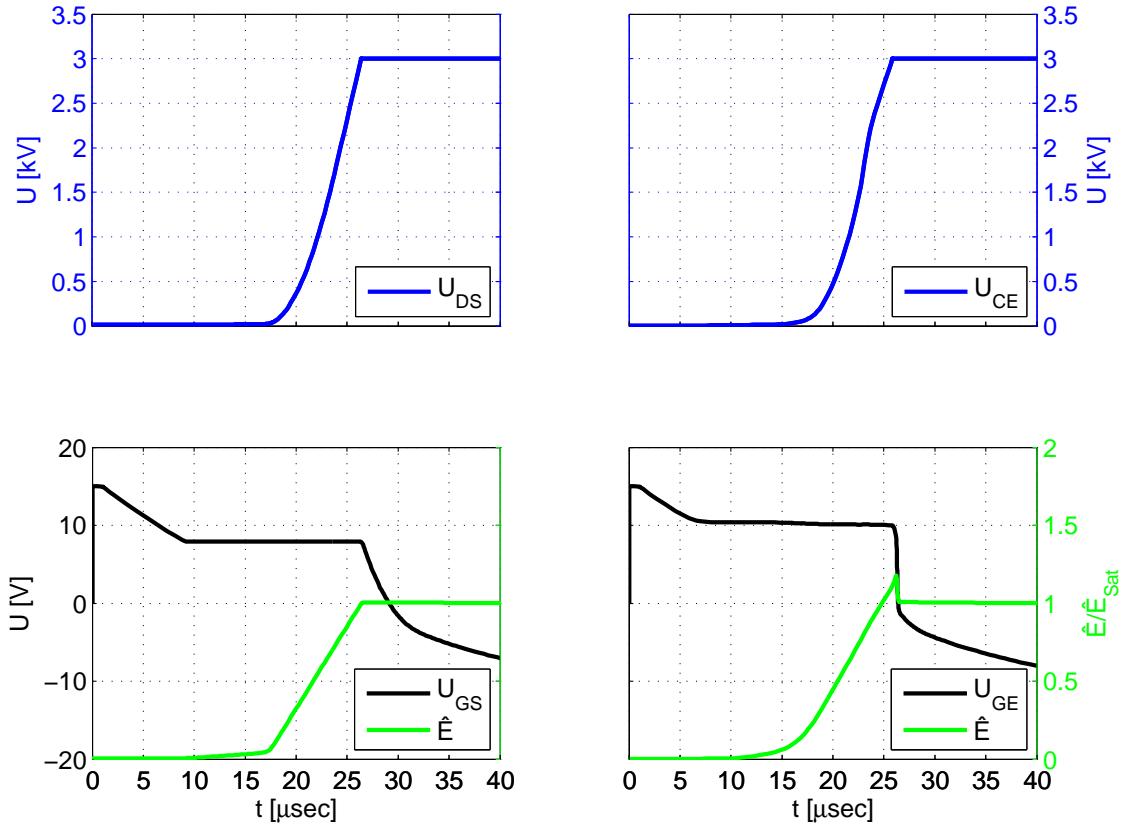

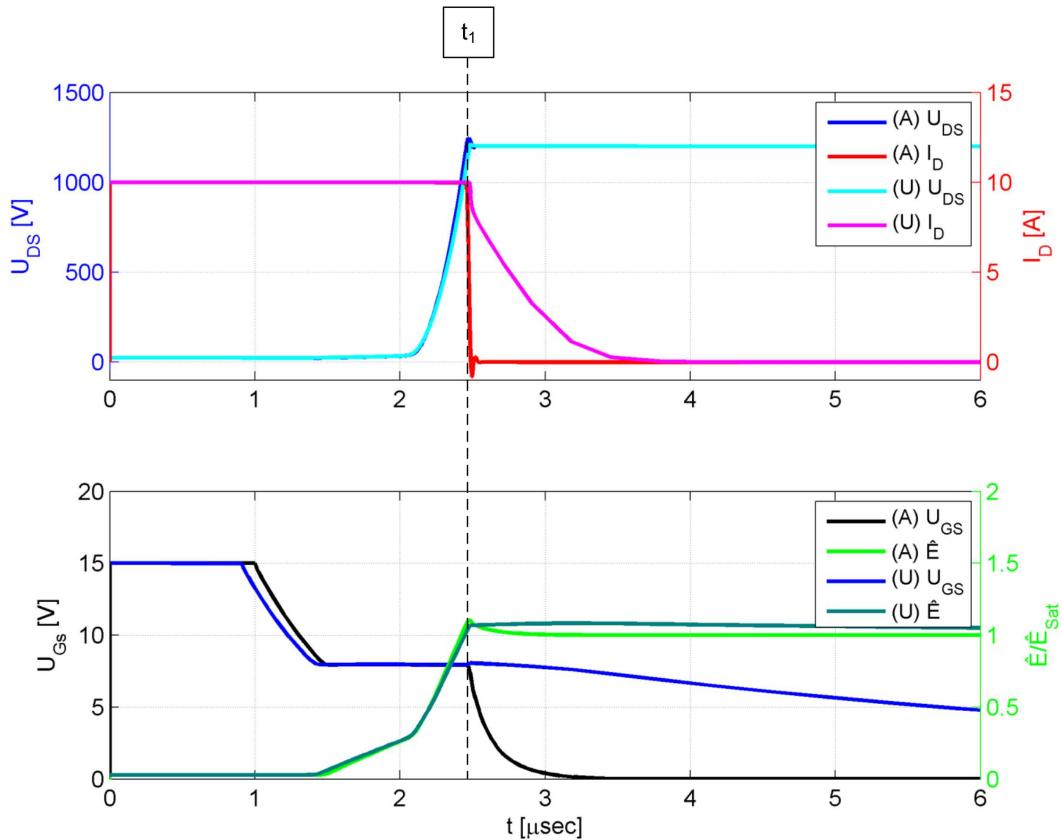

| <br>6.1. Simulation: Abschaltverhalten eines 6,5 kV MOSFET mit großem Gateentladestrom . . . . .                                                                                                         | 62 |

| 6.2. Querschnitt einer MOSFET-Zelle beim Abschalten . . . . .                                                                                                                                            | 63 |

| 6.3. Kapazitives Ersatzschaltbild eines MOSFETs mit gesteuerter Stromquelle . . . . .                                                                                                                    | 64 |

| 6.4. Wichtige Kenngrößen beim Abschalten von MOSFETs. Simulation eines 6,5 kV MOSFET mit verschiedenen Gatewiderständen . . . . .                                                                        | 67 |

| <br>7.1. Simulation: Vergleich des Schaltverhalten eines MOSFETs und eines IGBTs (ohne Überspannung) . . . . .                                                                                           | 71 |

| 7.2. Messung: Abschaltverhalten eines 6,5 kV - 600 A IGBTs – $i_G = 0$ für $t > t_1$ . . . . .                                                                                                           | 72 |

| 7.3. Simulation: Abschaltverhalten eines 6,5 kV IGBT – $i_G = 0$ für $t > t_1$ . . . . .                                                                                                                 | 73 |

| 7.4. Simulation: Abschaltverhalten eines 6,5 kV IGBT – $i_G = 0$ für $t > t_1$ ; Ausschnitt aus 7.3 . . . . .                                                                                            | 74 |

| 7.5. Simulation: Abschaltverhalten eines 6,5 kV MOSFETs – Vergleich zwischen einer einfachen Widerstandsansteuerung und Widerstandsumschaltung während der Spannungsflanke . . . . .                     | 75 |

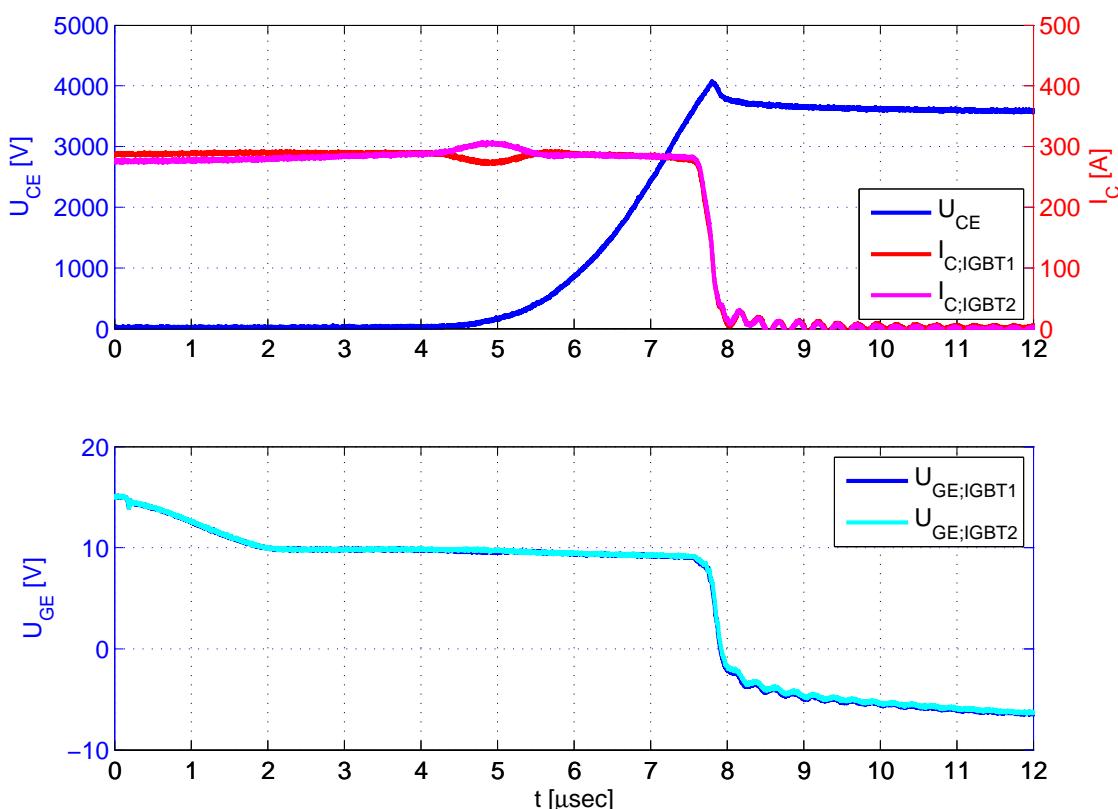

| 7.6. Messung eines 6,5 kV - 600 A IGBTs im Kurzschlussfall II zum Self Turn Off Effekt . . . . .                                                                                                         | 76 |

| 7.7. Messung: Kurzschlussfall II aus [4] zum Self Turn Off Effekt . . . . .                                                                                                                              | 77 |

| 7.8. Simulation: Kurzschlussfall II zum Self Turn Off Effekt . . . . .                                                                                                                                   | 78 |

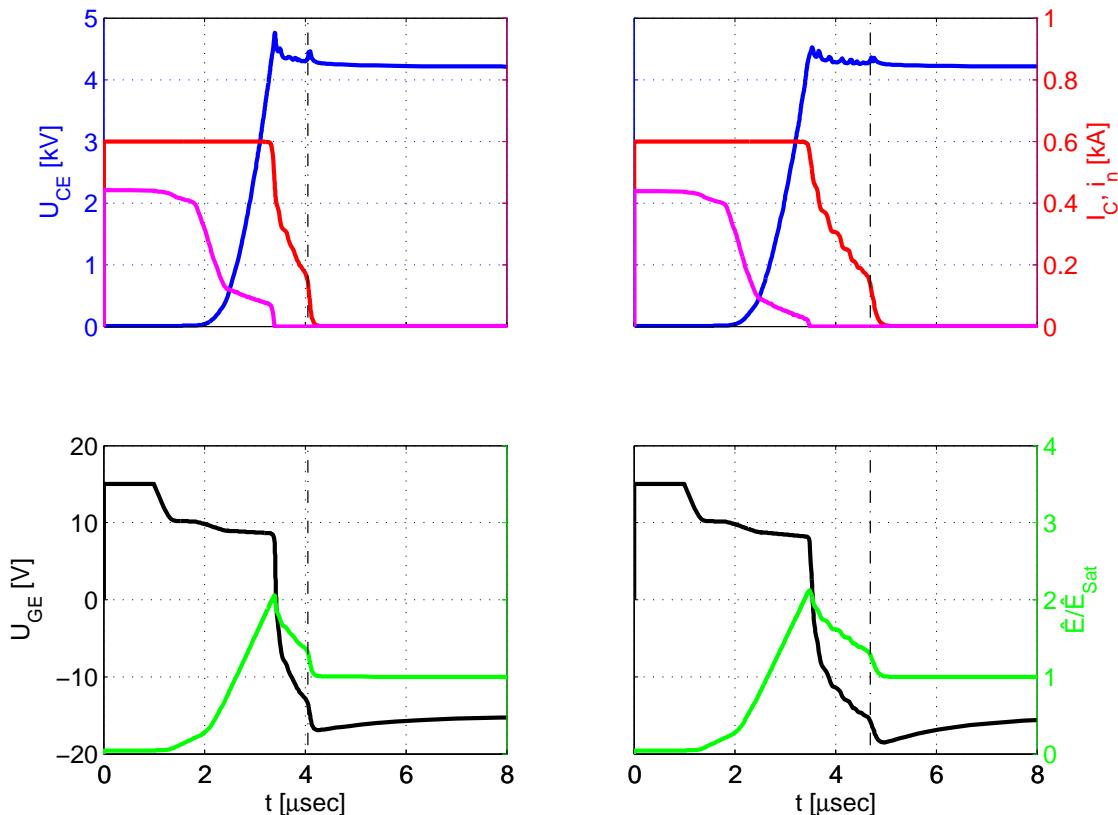

| 7.9. Messung: Abschaltverhalten eines 6,5 kV - 600 A IGBTs – Vergleich zwischen einer einfachen Widerstandsansteuerung und Widerstandsumschaltung zur Reduzierung der Verzugszeit . . . . .              | 79 |

| 7.10. Simulation: Abschaltverhalten eines 6,5 kV IGBTs – Vergleich zwischen einer einfachen Widerstandsansteuerung und Widerstandsumschaltung zur Reduzierung der Verzugszeit . . . . .                  | 81 |

| 7.11. Querschnitt durch eine IGBT-Zelle beim Abschalten im Zeitpunkt des Erreichens der Zwischenkreisspannung – Vergleich zwischen einfacher Widerstandsansteuerung und Widerstandsumschaltung . . . . . | 82 |

|                                                                                                                                                                                       |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.12. Simulation: Abschaltverhalten eines 6,5 kV MOSFETs – Vergleich zwischen einer einfachen Widerstandsansteuerung und Widerstandsumschaltung während der Spannungsflanke . . . . . | 83  |

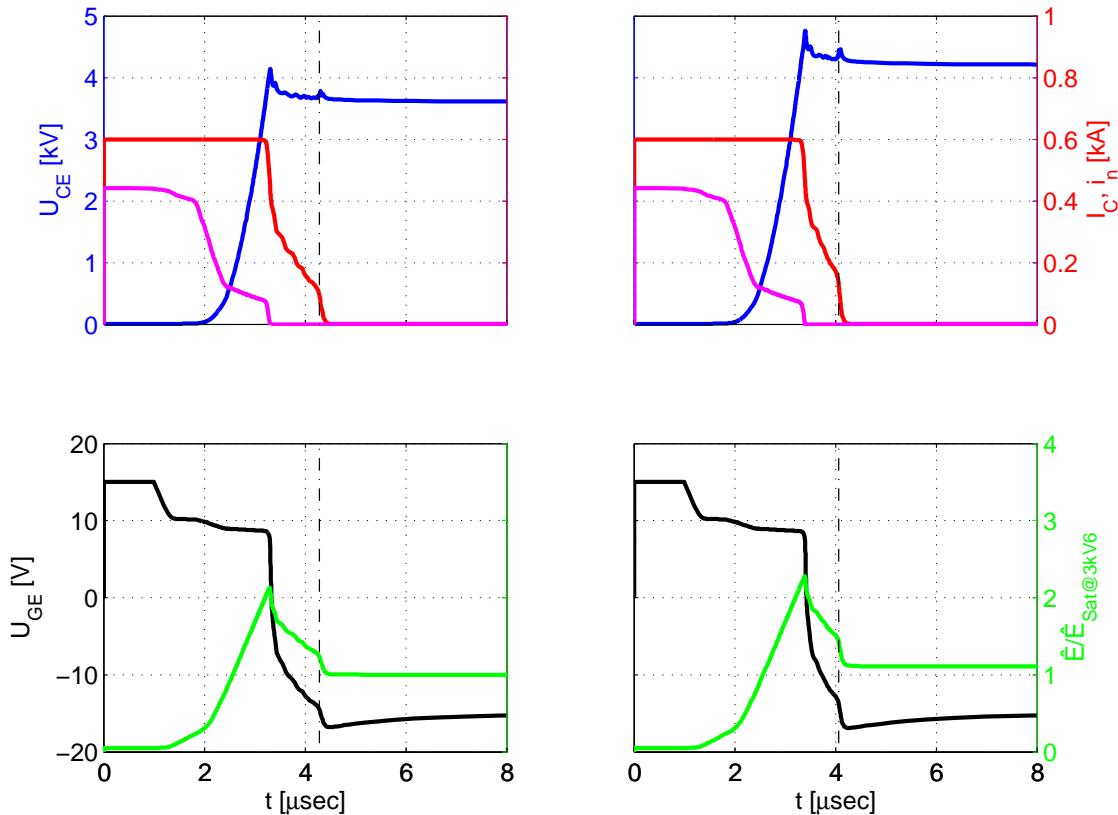

| 7.13. Messung: Abschaltverhalten eines 6,5 kV - 600 A IGBTs bei verschiedenen Sperrsichttemperaturen . . . . .                                                                        | 84  |

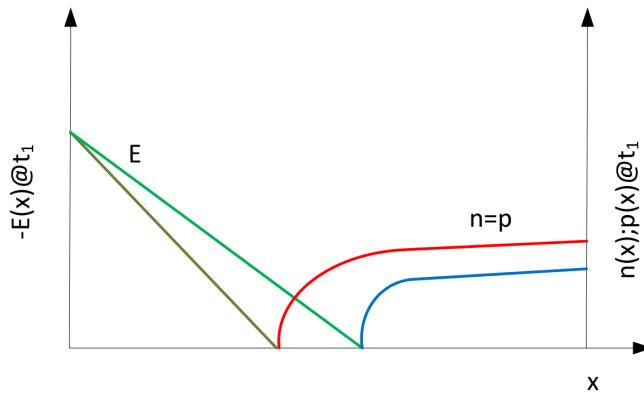

| 7.14. Zeichnung: Verlauf der Feldstärke und Ladungsträgerkonzentration bei verschiedenen Temperaturen . . . . .                                                                       | 85  |

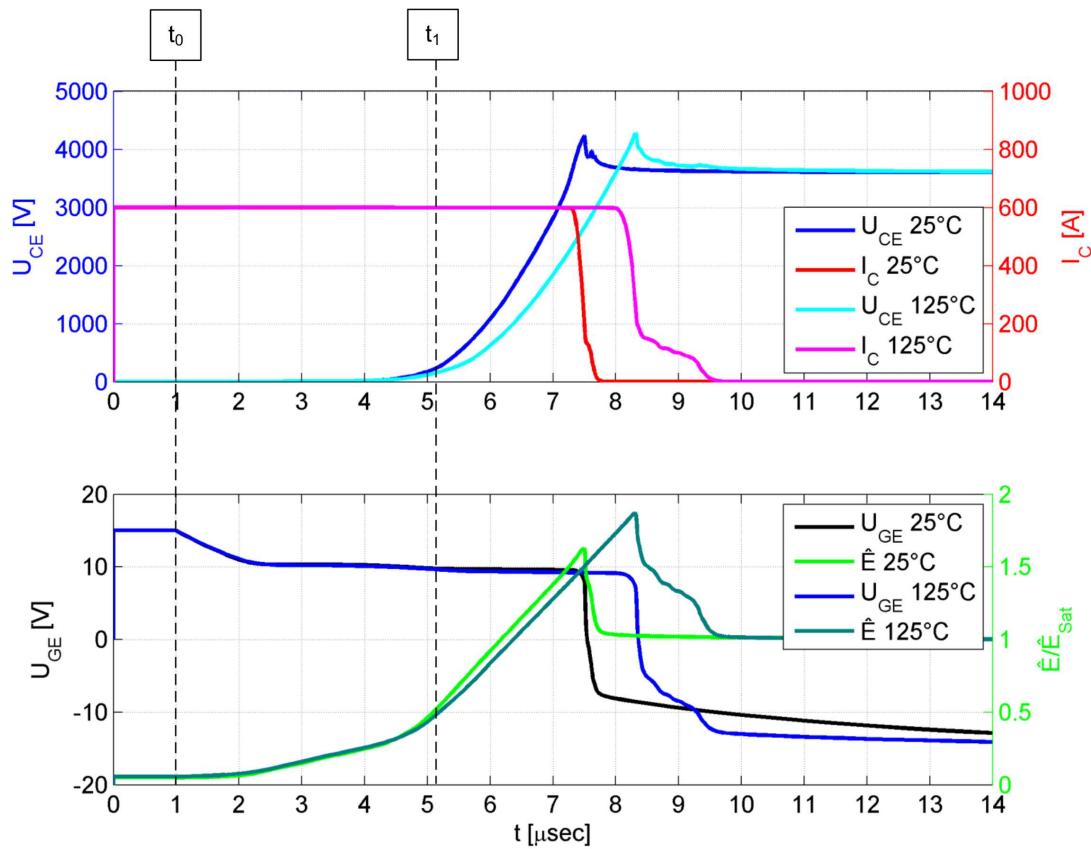

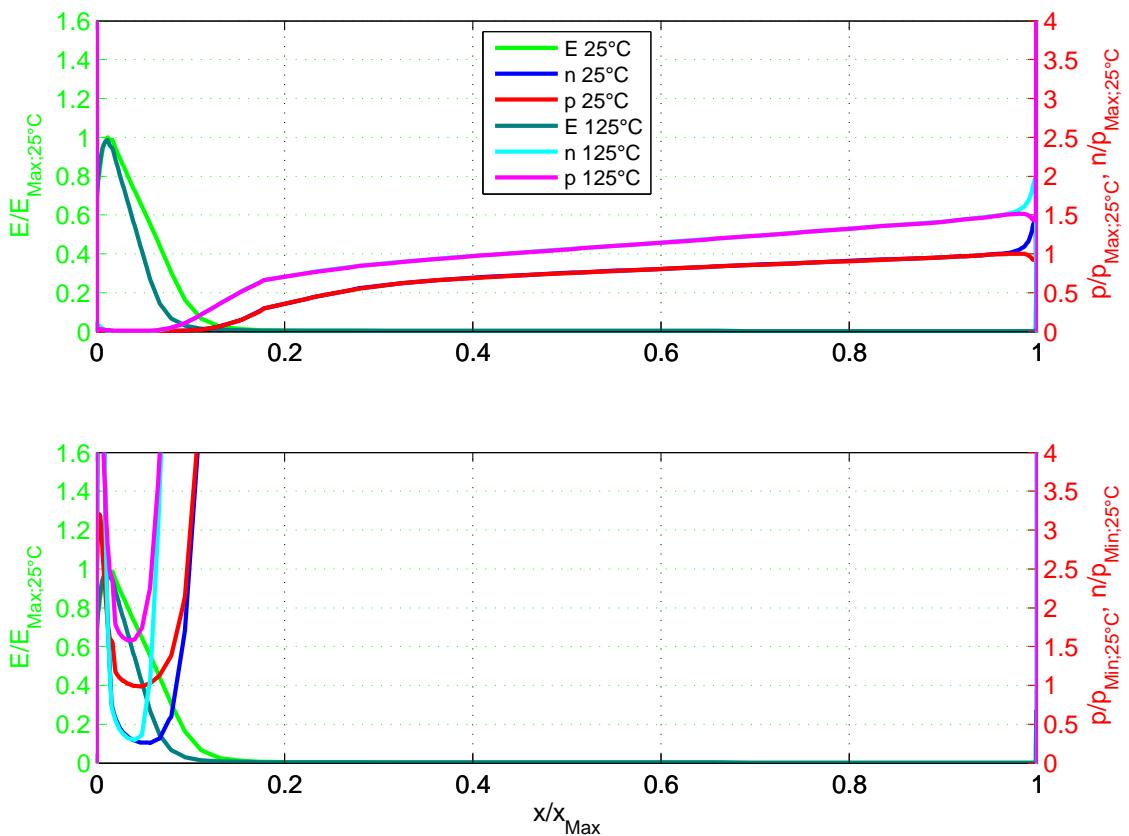

| 7.15. Simulation: Abschaltverhalten eines 6,5 kV IGBTs bei verschiedenen Sperrsichttemperaturen . . . . .                                                                             | 86  |

| 7.16. Simulation: Feldstärkeverlauf bei verschiedenen Temperaturen bei Erreichen von $t_1$ aus Abbildung 7.15 . . . . .                                                               | 87  |

| 7.17. Simulation: Feldstärkeverlauf bei verschiedenen Temperaturen bei Erreichen der Zwischenkreisspannung aus Abbildung 7.15 . . . . .                                               | 88  |

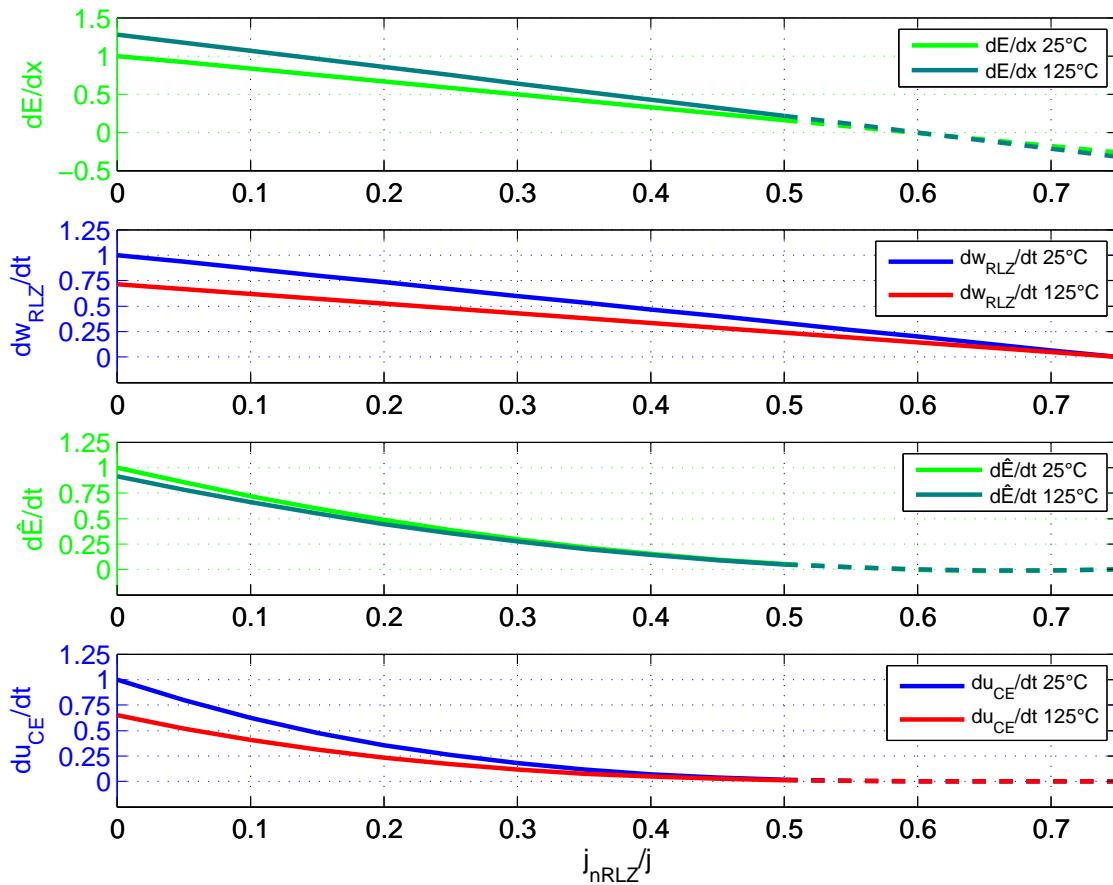

| 7.18. Analytisches Ergebnis bei verschiedenen Sperrsichttemperaturen mit angegebenen Maximalwerten . . . . .                                                                          | 93  |

| 7.19. Messung: Abschaltverhalten von selektierten 6,5 kV - 600 A IGBTs in Parallelschaltung – Ohne Stromfehlverteilung . . . . .                                                      | 95  |

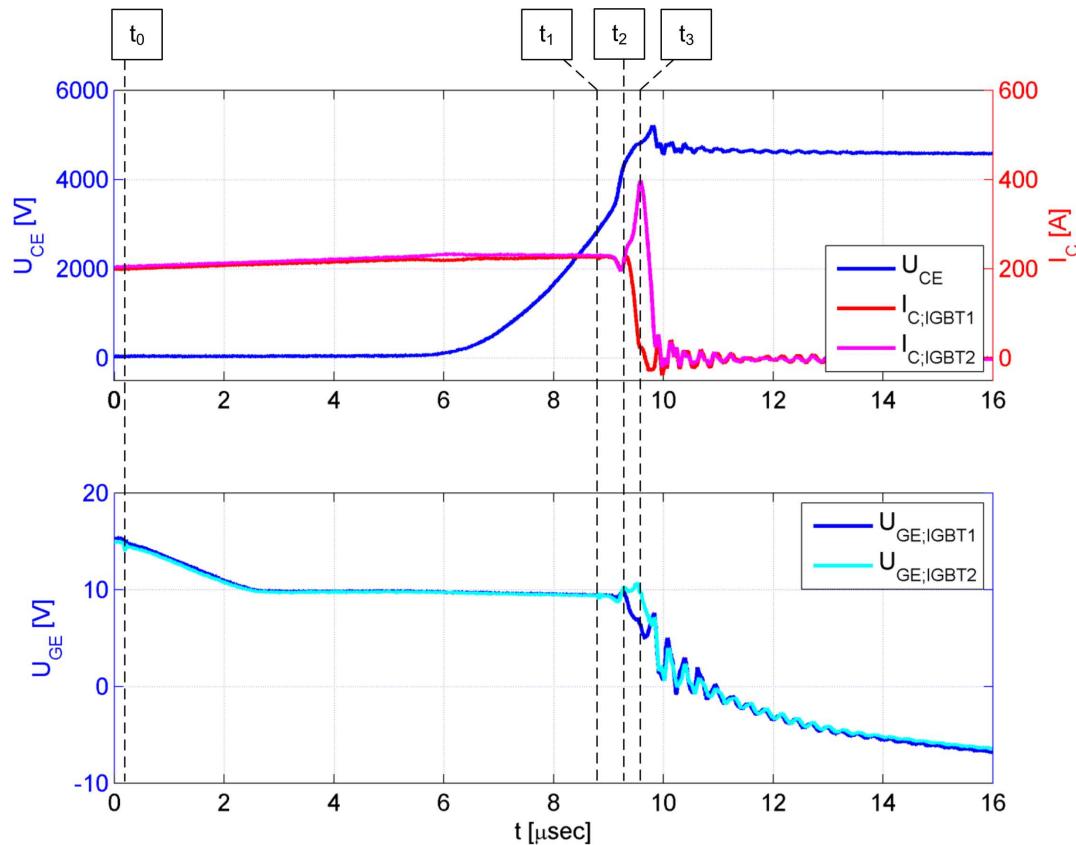

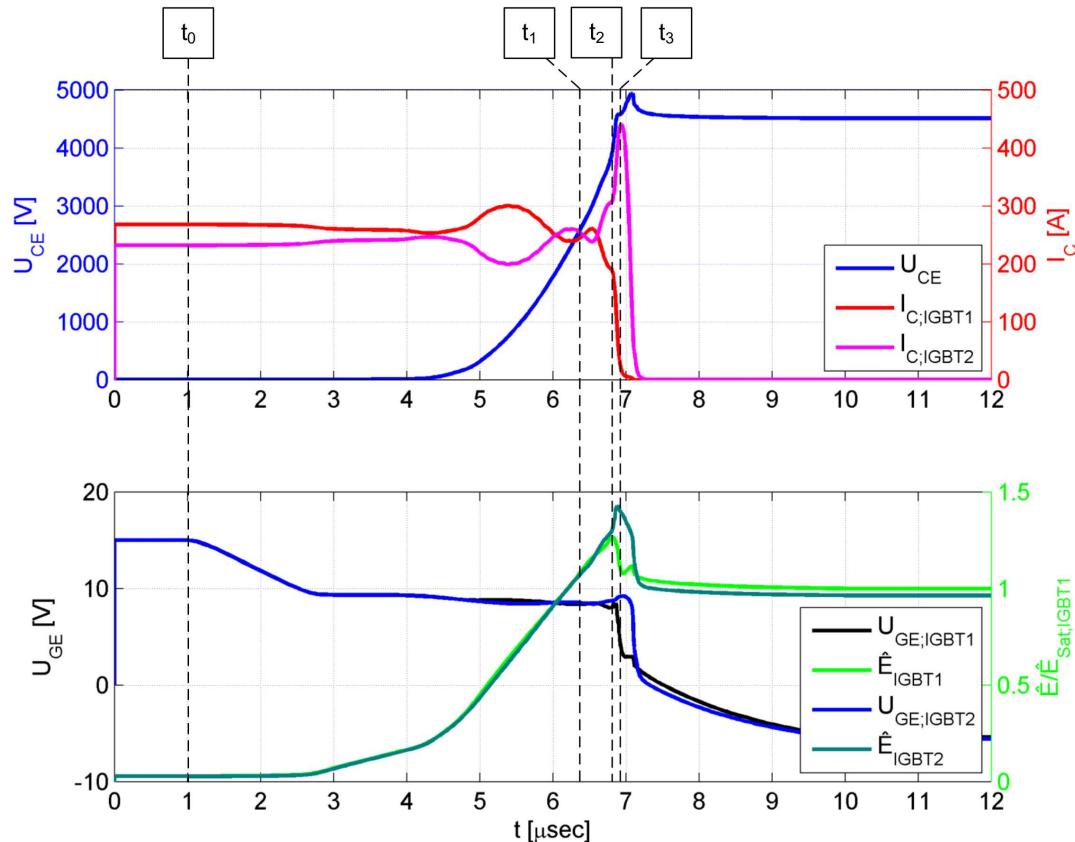

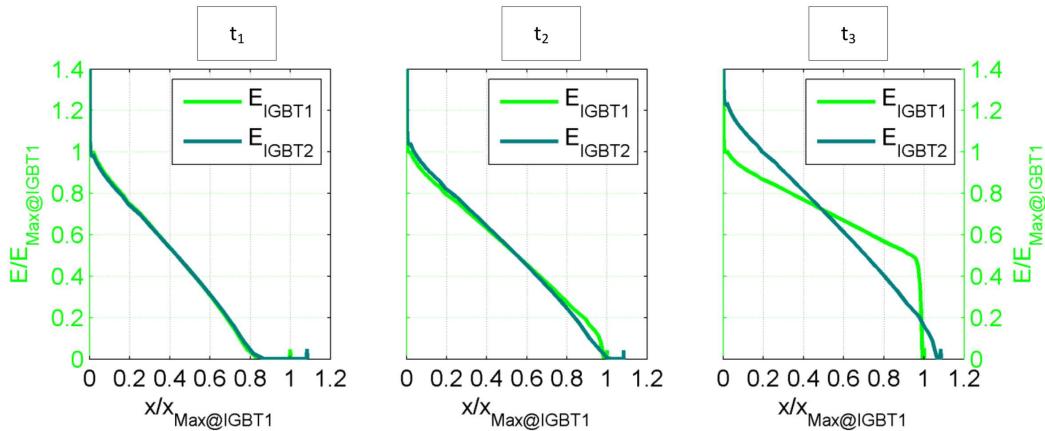

| 7.20. Messung: Abschaltverhalten von selektierten 6,5 kV - 600 A IGBTs in Parallelschaltung – Stromfehlverteilung bei $t_3$ . . . . .                                                 | 97  |

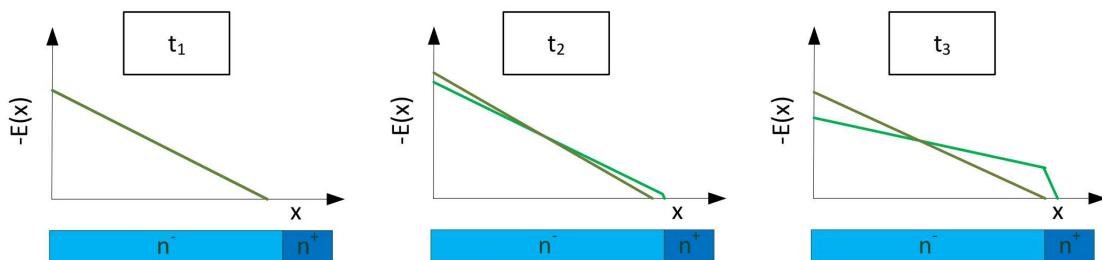

| 7.21. Zeichnung: Feldverlauf zu den Zeitschritten $t_1$ , $t_2$ und $t_3$ zu Abbildung 7.20 . . . . .                                                                                 | 97  |

| 7.22. Simulation: Abschaltverhalten von parallelgeschalteten 6,5 kV IGBTs – Stromfehlverteilung bei $t_3$ . . . . .                                                                   | 98  |

| 7.23. Simulation: Feldverlauf zu den Zeitschritten $t_1$ , $t_2$ und $t_3$ zu Abbildung 7.22 . . . . .                                                                                | 99  |

| <br>A.1. Prinzipschaltbild des verwendeten Treibers für einfache Widerstandsansteuerung . . . . .                                                                                     | 105 |

| A.2. Prinzipschaltbild des verwendeten Treibers für die Widerstandsumschaltung . . . . .                                                                                              | 106 |

| <br>B.1. Simulationsschaltung der einfachen Widerstandsansteuerung beim IGBT bzw. MOSFET . . . . .                                                                                    | 107 |

| B.2. Simulationsschaltung der Widerstandsumschaltung beim IGBT bzw. MOSFET . . . . .                                                                                                  | 109 |

| B.3. Simulationsschaltung des Kurzschlussverhaltens beim IGBT . . . . .                                                                                                               | 110 |

| B.4. Skizze des Simulationsmodells mit räumlicher Angabe der gemachten Schnitte . . . . .                                                                                             | 111 |

|                                                                                              |     |

|----------------------------------------------------------------------------------------------|-----|

| B.5. Extraktion der Simulationsdaten für den Vergleich der analytischen Herleitung . . . . . | 112 |

|----------------------------------------------------------------------------------------------|-----|

## **Tabellenverzeichnis**

|                                                                                                                           |    |

|---------------------------------------------------------------------------------------------------------------------------|----|

| 7.1. Driftgeschwindigkeiten bei verschiedenen Temperaturen bei einer Feldstärke von 50 kV/cm nach [28] . . . . .          | 90 |

| 7.2. Vergleich der Simulationsergebnisse mit den Ergebnissen der analytischen Herleitung bei $j_{nRLZ}/j = 0,1$ . . . . . | 94 |

## Abkürzungsverzeichnis

|              |                                                        |

|--------------|--------------------------------------------------------|

| $\epsilon$   | Dielektrizitätskonstante                               |

| $\hat{E}$    | Räumliches Maximum der elektrischen Feldstärke         |

| $\mu_n$      | Beweglichkeit freier Elektronen                        |

| $\mu_p$      | Beweglichkeit freier Löcher                            |

| $\rho$       | Raumladung                                             |

| $\tau$       | Zeitkonstante                                          |

| $+U_B$       | Positive Versorgungsspannung der Ansteuerungsschaltung |

| $-U_B$       | Negative Versorgungsspannung der Ansteuerungsschaltung |

| A            | Fläche                                                 |

| ASIC         | Application Specific Integrated Circuit                |

| C            | Kapazität                                              |

| $C_{CE}$     | Kollektor-Emitter Kapazität beim IGBT                  |

| $C_{CG,ext}$ | Externe Kapazität zwischen Kollektor und Gate          |

| $C_{DS}$     | Drain-Source Kapazität beim MOSFET                     |

| $C_{GC}$     | Millerkapazität beim IGBT                              |

| $C_{GD}$     | Millerkapazität beim MOSFET                            |

| $C_{GE,ext}$ | Externe Kapazität zwischen Gate und Emitter            |

| $C_{GE}$     | Gate-Emitter Kapazität beim IGBT                       |

| $C_{GS}$     | Gate-Source Kapazität beim MOSFET                      |

| $C_{IGBT}$   | Ersatzkapazität des IGBTs                              |

| CAD          | Computer Aided Design                                  |

| CS           | Carrier Stored                                         |

| CSTBT        | Carrier Stored Trench Gate Bipolar Transistor          |

| D            | Diode                                                  |

| $D_{el}$     | Elektrische Flussdichte                                |

| DUT          | Device Unter Test                                      |

| E            | Elektrische Feldstärke                                 |

| EMV          | Elektromagnetische Verträglichkeit                     |

| FEM          | Finite Elemente Methode                                |

| FPGA         | Field Programmable Gate Array                          |

| FS           | Field Stop oder Feldstopp                              |

| $g_m$        | Steilheit des Transistors                              |

| GTO          | Gate Turn Off (Thyristor)                              |

|                     |                                                             |

|---------------------|-------------------------------------------------------------|

| HE .....            | Hilfsemitter                                                |

| I .....             | Strom                                                       |

| i .....             | Zeitabhängiger Strom                                        |

| $i_{C,DS}$ .....    | Strom durch die Drain-Source Kapazität beim MOSFET          |

| $i_{C,GC}$ .....    | Strom durch die Millerkapazität beim IGBT                   |

| $i_{C,GD}$ .....    | Strom durch die Millerkapazität beim MOSFET                 |

| $i_{C,IGBT}$ .....  | Strom durch die Ersatzkapazität $C_{IGBT}$                  |

| $I_C$ .....         | Kollektorstrom beim IGBT                                    |

| $I_D$ .....         | Drainstrom beim MOSFET                                      |

| $I_G$ .....         | Gatestrom beim IGBT und MOSFET                              |

| $I_{Last}$ .....    | Strom durch die Lastinduktivität                            |

| $i_{nRLZ}$ .....    | Elektronenstrom in der Raumladungszone                      |

| $i_n$ .....         | Elektronenstrom                                             |

| $i_{pPlasma}$ ..... | Löcherstrom im Plasma                                       |

| $i_{pRLZ}$ .....    | Löcherstrom in der Raumladungszone                          |

| $i_p$ .....         | Löcherstrom                                                 |

| IGBT .....          | Insulated Gate Bipolar Transistor                           |

| IGCT .....          | Integrated Gate Commutated Thyristor                        |

| j .....             | Verschiebestromdichte                                       |

| $j_{C,GC}$ .....    | Verschiebestromdichte durch die Millerkapazität beim IGBT   |

| $j_{C,GD}$ .....    | Verschiebestromdichte durch die Millerkapazität beim MOSFET |

| $j_n$ .....         | Verschiebestromdichte des Elektronenstroms                  |

| $j_p$ .....         | Verschiebestromdichte des Löcherstroms                      |

| KS .....            | Kurzschluss                                                 |

| L .....             | Induktivität                                                |

| $L_\sigma$ .....    | Kommutierungskreisinduktivität                              |

| $L_{KS}$ .....      | Kurzschlussinduktivität                                     |

| LPT .....           | Light Punch Through                                         |

| MOSFET ....         | Metal Oxide Semiconductor Field Effect Transistor           |

| n .....             | Dichte freier Elektronen                                    |

| NPT .....           | Non Punch Through                                           |

| p .....             | Dichte freier Löcher                                        |

| PE .....            | Poweremitter                                                |

| PIN-Diode ...       | Positive Intrinsic Negative Diode                           |

| PT .....            | Punch Through                                               |

| Q .....             | Ladung                                                      |

| q .....             | Elementarladung                                             |

| $R_B$ .....         | Widerstand der n <sup>-</sup> -Basis                        |

|                  |                                                         |

|------------------|---------------------------------------------------------|

| $R_{G,int}$      | Interner Gatewiderstand                                 |

| $R_{G,off}$      | Ausschaltgatewiderstand                                 |

| $R_{G,On}$       | Einschaltgatewiderstand                                 |

| $R_W$            | Widerstand der p-Wanne                                  |

| $RLZ$            | Raumladungszone                                         |

| $S$              | Allgemein Schalter                                      |

| $SiO_2$          | Siliziumdioxid                                          |

| $SOA$            | Safe Operating Area                                     |

| $SPT$            | Soft Punch Through                                      |

| $T$              | Transistor                                              |

| $t$              | Zeit                                                    |

| $T_j$            | Sperrsichttemperatur                                    |

| $T_{KS}$         | Kurzschlusschalter                                      |

| $TWPT$           | Thin Wafer Punch Through                                |

| $U$              | Spannung                                                |

| $u$              | Zeitabhängige Spannung                                  |

| $U_{CE,max}$     | Maximale Kollektor-Emitter Spannung beim IGBT           |

| $U_{CE,Sat}$     | Sättigungsspannung im eingeschalteten Zustand beim IGBT |

| $U_{CE}$         | Kollektor-Emitter Spannung beim IGBT                    |

| $U_{DS,Max}$     | Maximale Drain-Source Spannung beim MOSFET              |

| $U_{DS}$         | Drain-Source Spannung beim MOSFET                       |

| $U_d$            | Zwischenkreisspannung                                   |

| $U_{FR}$         | Forward Recovery Spannung der Diode                     |

| $U_{GC}$         | Spannung über der Millerkapazität beim IGBT             |

| $U_{GD}$         | Spannung über der Millerkapazität beim MOSFET           |

| $U_{GE,Plateau}$ | Wert des Millerplateau beim IGBT                        |

| $U_{GE}$         | Gate-Emitter Spannung beim IGBT                         |

| $U_{GS}$         | Gate-Source Spannung beim MOSFET                        |

| $U_{IN}$         | Eingangsspannung                                        |

| $U_{Max}$        | Maximale Spannung                                       |

| $U_{Th}$         | Schwellspannung                                         |

| $U_{TR,Off}$     | Negative statische Gatespannung                         |

| $U_{TR,On}$      | Positive statische Gatespannung                         |

| $v_n$            | Geschwindigkeit der Elektronen                          |

| $v_p$            | Geschwindigkeit der Löcher                              |

| $W_{Off}$        | Ausschaltverluste                                       |

| $x$              | Dicke des Bauelements                                   |

| $x_{RLZ}$        | Weite der Raumladungszone                               |

# 1. Einleitung

IGBTs (*Insulated Gate Bipolar Transistors*) haben sich innerhalb der letzten drei Dekaden als leistungselektronische Bauelemente etabliert. Diese vereinen die positiven Ansteuerungseigenschaften eines *Metal Oxide Semiconductor Field Effect Transistor* (MOSFET) mit den Durchlasseigenschaften eines bipolaren Bauelements. Durch die Verfügbarkeit von IGBT-Modulen mit einer Sperrspannung von bis zu 6,5 kV werden diese erfolgreich in Mittel- und Hochspannungsanwendungen eingesetzt, welche bislang nur Thyristorstrukturen wie dem GTO (*Gate Turn Off Thyristor*) und dem IGCT (*Integrated Gate Commutated Thyristor*) vorbehalten waren. Die Stromtragfähigkeit heutiger IGBT-Module reicht von wenigen Ampere bis einigen tausend Ampere und lässt sich durch Parallelschaltung von IGBT-Modulen noch weiter erhöhen. Neben der Steigerung der Leistungsdichte wurden in den letzten Jahren auch die statischen und dynamischen Eigenschaften von IGBTs verbessert. Dazu gehört sowohl die Reduktion auftretender Schaltverluste als auch die Verbesserungen der Robustheit beim Abschalten von Überstrom.

Obwohl der IGBT seit geraumer Zeit auf dem Markt erhältlich ist, konnten in der aktuellen Literatur bisher nicht alle Effekte beim Abschalten des Bauteils erklärt werden. Um das Ausschaltverhalten des IGBTs zu analysieren und die positiven Ansteuerungseigenschaften dieser Halbleiter ausnutzen zu können, ist ein hohes Maß an Verständnis des Schaltverhaltens erforderlich. Motivation dieser Arbeit ist es daher, hierfür einen Beitrag zu leisten.

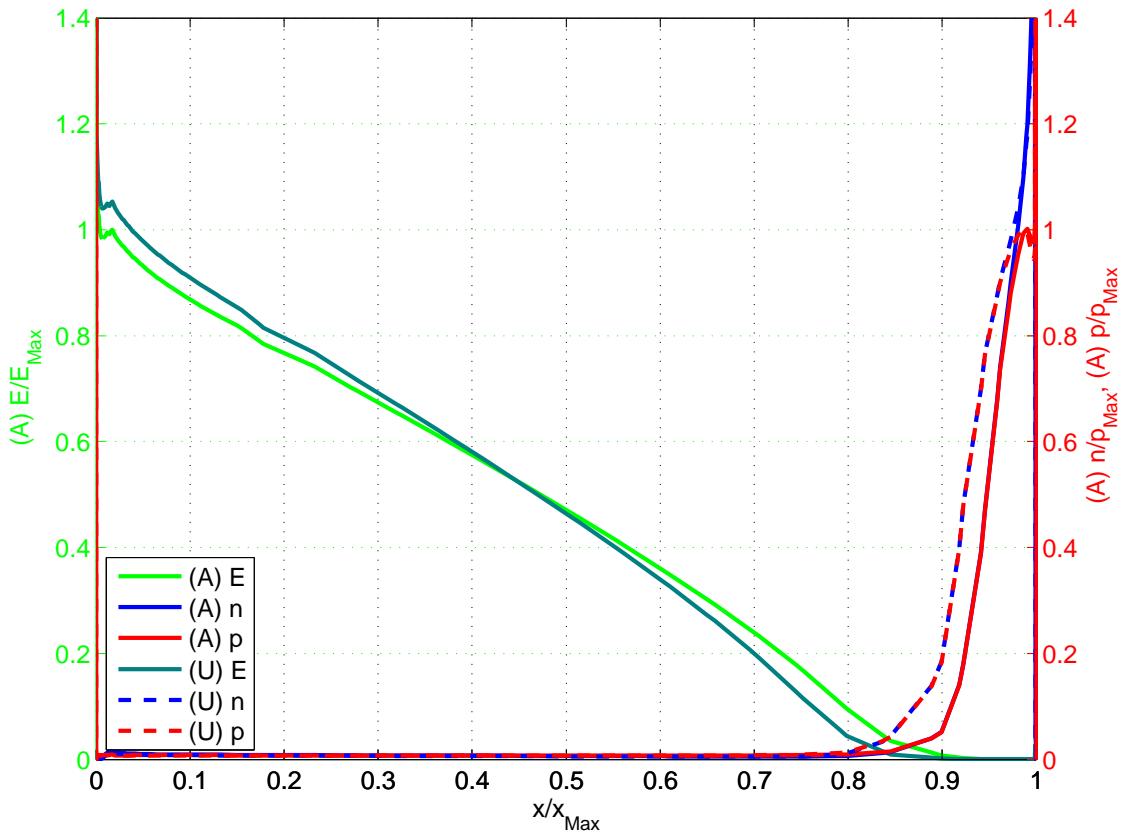

Der Grund für die gute Steuerbarkeit der Spannungsflanke bei IGBT und MOSFET ist die sogenannte Millerkapazität. Anders als beim MOSFET tragen beim IGBT sowohl Elektronen als auch Löcher zum Stromfluss bei. Hierdurch ist nicht nur das Schaltverhalten unterschiedlich, sondern auch die Wirkung der Millerkapazität. Im Rahmen dieser Arbeit wird der Fokus auf das Abschaltverhalten von IGBT und MOSFET gelegt. Dieses wird im Folgenden unter verschiedenen Aspekten näher untersucht und die Unterschiede zwischen diesen Leistungshalbleitern herausgearbeitet. Es wird gezeigt, dass gerade beim Abschaltverhalten von IGBTs Effekte auftreten, welche mit einfachen Ersatzschaltbildern nur unvollständig zu erklären sind. Diese lassen sich allerdings analysieren, indem die dreidimensionale Struktur des IGBTs auf eine Dimension reduziert wird und direkt die auftretenden Feldstärken

in der Raumladungszone betrachtet werden.

Zur Herleitung und Veranschaulichung dieser Effekte tragen sowohl Messungen am IGBT als auch Simulationsergebnisse von MOSFET und IGBT bei. Die Messungen wurden hierfür an einem Hochspannungsprüfplatz durchgeführt. Die Simulationen wurden mit einem zweidimensionalen Bauteilsimulator (Taurus Medici) der Firma Synopsis® erstellt. Dieses CAD-Simulationstool bedient sich der Finite Elemente Methode (FEM). Mit diesem Bauteilsimulator ist es nicht nur möglich, den zeitlichen Verlauf des Schaltverhaltens von Halbleitern zu simulieren. Es können auch Schnitte durch die Bauteilzellen gelegt werden, um somit den Feldstärkeverlauf und die Ladungsträgerkonzentration im Bauteil zu extrahieren. Das in dieser Arbeit verwendete Simulationsmodell des IGBTs stammt von einem Halbleiterhersteller und bildet das Verhalten eines auf dem Markt verfügbaren 6,5 kV – 600 A IGBTs nach.

In den einleitenden Kapiteln werden zunächst eine MOSFET- und eine IGBT-Zelle vergleichend dargestellt. Weiterhin werden verschiedene IGBT-Zellstrukturen vorgestellt. Eingegangen wird hierbei sowohl auf Unterschiede im stromlosen als auch im eingeschalteten Zustand. Darauf aufbauend wird auf die allgemeine Funktionsweise sowie das grundsätzliche Schaltverhalten des IGBTs eingegangen. Basierend auf einer durchgeführte Literaturrecherche erfolgt zudem die Darstellung bekannter Ansteuerungsschaltungen und Schutzschaltungen für IGBTs.

Das fünfte Kapitel widmet sich den Auswirkungen des Elektronen-Loch Plasmas auf das Ausschaltverhalten des IGBTs. Insbesondere die aus der Literatur bekannten Effekte wie die Feldaufteilung und der Verlauf des Maximums der elektrischen Feldstärke werden anhand von Simulationen analysiert. In Anlehnung an [53] werden zudem die Spannungs- und Stromverläufe des IGBTs auf Basis eines Ersatzschaltbildes erläutert. Dieses Model verliert jedoch mit dem Anstoßen der Raumladungszone an die Feldstopp-Schicht seine Übersichtlichkeit. Basierend auf [16] wurde der Anstoßzeitpunkt mit Hilfe von Simulationen in Abhängigkeit des Gateentladewiderstandes, des Kollektorstromes und der Zwischenkreisspannung analysiert. Im Rahmen der vorliegenden Arbeit wurde dies um den Aspekt der Sperrsichttemperatur erweitert.

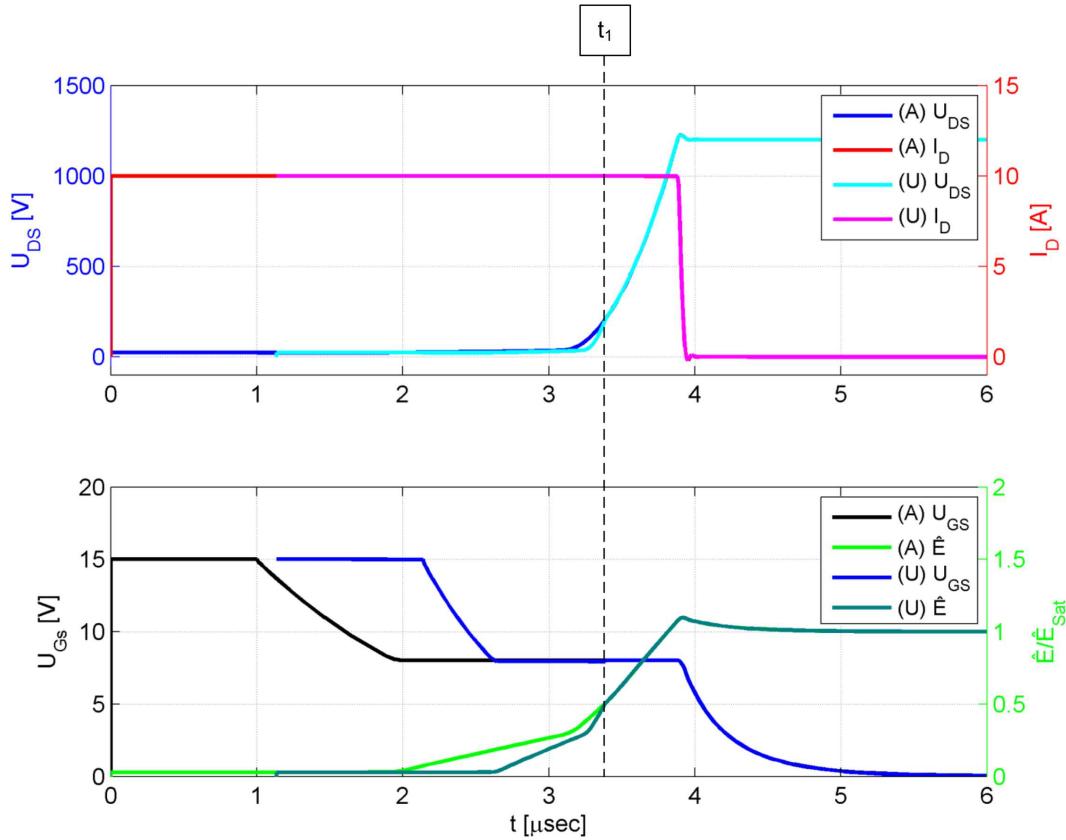

Im sechsten Kapitel werden der Verlauf des Maximums der elektrischen Feldstärke und der Gradient der elektrischen Feldstärke beim MOSFET mit Hilfe von Simulationen analysiert und der Unterschied zum Abschaltverhalten des IGBTs herausge-

arbeitet. Weiterhin werden die Schalttransienten anhand des allgemein bekannten Ersatzschaltbildes erläutert.

Bis hierher wurden vornehmlich die Unterschiede zwischen diesen Leistungshalbleitern sowie die daraus resultierenden Effekte beim Ausschalten des IGBTs dargestellt und anhand von Messungen und Simulationen nachvollzogen. Im weiteren Verlauf wird unter anderem gezeigt, dass der Gateentladestrom nicht den Spannungsanstieg der Kollektor-Emitter Spannung einstellt, sondern das räumliche Maximum der elektrischen Feldstärke. Wie in [7] veröffentlicht können unter Berücksichtigung dieser Erkenntnis Effekte wie der *Self Turn Off* Prozess analysiert werden, wenn anstelle eines Ersatzschaltbildes die auftretenden Feldstärken in der Raumladungszone betrachtet werden. Auf Basis dieser Erkenntnis, wird ein Vergleich zwischen einer einfachen Widerstandsansteuerung und einer Widerstandsumschaltung zur Reduzierung der Verzugszeit zwischen Ausschaltsignal und Beginn der steigenden Kollektor-Emitter Spannung durchgeführt und die Unterschiede der Kurvenverläufe analysiert. Weiterhin ermöglicht diese Betrachtungsweise eine Analyse der Sperrsichttemperatur auf das Ausschaltverhalten von IGBTs, welche in [5] veröffentlicht wurde. Darüber hinaus kann mit der Erkenntnis aus [7] eine präzise Erklärung der Gegebenheiten einer Stromfehlverteilung parallelgeschalteter IGBTs gegeben werden, welche in [8] publiziert wurde.

## 2. Aufbau des IGBTs

Dieses Kapitel beschreibt den grundsätzlichen Aufbau sowie verschiedene Strukturen von IGBT-Zellen. Als eine Weiterentwicklung des MOSFETs besitzt der IGBT eine zusätzliche hochdotierte  $p^+$ -Schicht am rückseitigen Emitterkontakt. Abbildung 2.1 stellt beide Bauteile vergleichend dar. Zunächst wird auf eine planare Gatestruktur eingegangen. Bedingt durch diesen Aufbau vereint der IGBT die positiven Ansteuereigenschaften eines MOSFETs mit den Durchlasseigenschaften eines bipolaren Leistungshalbleiters. In der Leistungselektronik werden, auf Grund der besseren Ladungsträgerbeweglichkeit von Elektronen gegenüber Löchern, fast ausschließlich IGBTs mit selbst sperrendem n-Kanal verwendet [34].

Abbildung 2.1.: Querschnitt einer MOSFET-Zelle (links) und einer IGBT-Zelle (rechts). Zeichnung nicht maßstabsgetreu.

Bei einem IGBT bestehen die Anschlusskontakte aus Polysilizium. Hierbei werden Gate und Emitter elektrisch durch Siliziumdioxid ( $\text{SiO}_2$ ) isoliert. Der schwach dotierte p<sup>-</sup>-Bereich ergibt zusammen mit dem hochdotierten p<sup>+</sup>-Gebiet die so genannte p-Wanne. Angrenzend an p-Wanne und Emitter befindet sich ein hochdotiertes n<sup>+</sup>-

Gebiet. Zwischen diesem  $n^+$ -Gebiet und der  $n^-$ -Basis bildet das niedrig dotierte  $p^-$ -Gebiet der p-Wanne einen n-leitenden MOS-Kanal sobald die Gate-Emitter Spannung über die Schwellspannung gestiegen ist. Insgesamt fungiert somit das emitterseitige  $n^+$ -Gebiet mit der p-Wanne und der  $n^-$ -Basis als npn-Transistor. Jener ergibt wiederum zusammen mit dem pnp-Transistor – aus p-Wanne,  $n^-$ -Basis und kollektorseitiger  $p^+$ -Schicht – eine Thyristorstruktur. Durch diese Struktur ist es möglich, dass der parasitäre Thyristor einrastet und der IGBT nicht mehr über den Gateanschluss steuerbar ist (*Latch Up*). Dies führt zu einer Zerstörung des Bauelements durch thermische Überlastung [3, 27, 61].

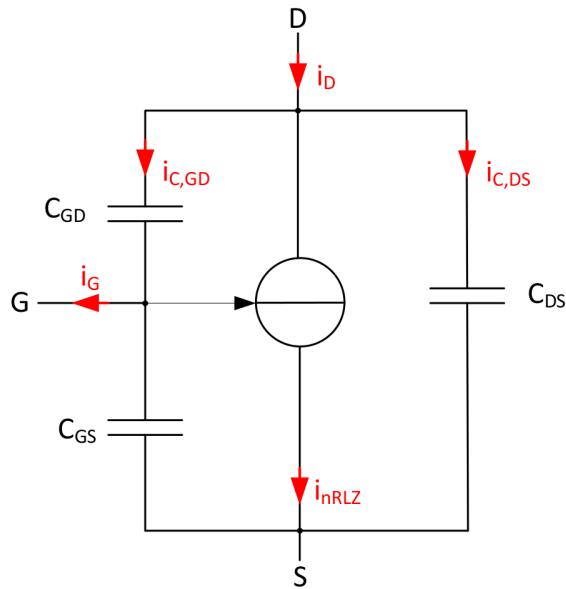

Abbildung 2.2 zeigt den Querschnitt durch eine IGBT-Zelle mit den parasitären Elementen in Anlehnung an [59] und [61]. Dabei bildet  $R_B$  den Widerstand der  $n^-$ -Basis, welcher sowohl die Stromverstärkung des pnp-Transistors als auch den Emitterwirkungsgrad beeinflusst. Mittels geeigneter Dotierung der p-Wanne wird der laterale Widerstand  $R_W$  im hochdotierten Gebiet der p-Wanne so eingestellt, dass der npn-Transistor im Normalbetrieb nicht durchschalten kann. Hierdurch wird insgesamt die Gefahr des Einrastens vermindert. Als zusätzliche Maßnahme zur Reduktion der *Latch Up* Gefahr wird der Löcherstrom durch Einstellung der Stromverstärkung im pnp-Transistor klein gehalten [61].

Aufgrund des Aufbaus ergeben sich drei parasitäre Kapazitäten, welche bei jedem Schaltvorgang umgeladen werden müssen.

- Kapazität zwischen Gate und Emitter  $C_{GE}$ : Entsteht auf Grund der Isolierung aus Siliziumdioxid zwischen Gate und Emitter.

- Kapazität zwischen Kollektor und Emitter  $C_{CE}$ : Sperrschichtkapazität zwischen  $n^-$ -Basis und p-Wanne.

- Kapazität zwischen Gate und Kollektor  $C_{GC}$ : Überschneidung der Gatemetallisierung und der  $n^-$ -Basis (Millerkapazität).

Begründet durch ihren Aufbau unterscheidet man grundsätzlich zwei IGBT-Typen: Der *Punch Through* IGBT (PT-IGBT) und der *Non Punch Through* IGBT (NPT-IGBT). Nachfolgende Weiterentwicklungen zur Verminderung der Durchlassverluste resultieren in der Entwicklung des *Field Stop* IGBTs sowie des *Trench Gate* IGBTs und des *Carrier Stored* IGBTs. In den nachfolgenden Unterkapiteln werden die verschiedenen IGBT-Konzepte vorgestellt.

Abbildung 2.2.: Ersatzschaltbild mit parasitären Elementen eines IGBTs. Zeichnung der IGBT-Zelle nicht maßstabsgetreu.

## 2.1. Punch Through IGBT

Die Herstellung eines PT-IGBT, welcher der erste verfügbare IGBT-Typ war, erfolgt auf einem  $p^+$ -Substrat. Über Epitaxie werden auf diesem Substrat der  $n^+$ -Puffer und die niedrig dotierte  $n^-$ -Basis abgeschieden. Durch das dicke und hoch dotierte  $p^+$ -Gebiet am Kollektor können verhältnismäßig viele Ladungsträger in die  $n^-$ -Basis injiziert werden. Hierdurch wird die Gefahr des Einrastens bei diesem IGBT-Typ erhöht. Um den Emitterwirkungsgrad zu reduzieren und damit die *Latch Up* Gefahr zu verkleinern, muss die Stromverstärkung des pnp-Transistors (vgl. Abbildung 2.2), wie zuvor erklärt, abgesenkt werden. Zusätzlich werden beim PT-IGBT durch Gold-dotierung oder Elektronenbestrahlung Rekombinationszentren in der  $n^+$ -Schicht am Emitter eingesetzt. Auf diese Weise wird sowohl die Ladungsträgerlebensdauer als auch die *Latch Up* Gefahr abgesenkt [41]. Da sich dies negativ auf das Schaltverhalten auswirkt, muss bei der Herstellung ein Kompromiss zwischen Durchlassspannung und Schaltverhalten gewählt werden [61]. Weiterhin steigt mit höherer Temperatur des IGBTs die Plasmakonzentration und es ergibt sich ein negativer Temperaturkoeffizient der Sättigungsspannung ( $U_{CE,Sat}$ ) und ein stark positiver Temperaturkoeffizient der Ausschaltverluste ( $W_{off}$ ). Beides wirkt sich negativ auf die Schaltbarkeit parallelgeschalteter PT-IGBTs aus [34].

Abbildung 2.3 zeigt den Querschnitt einer PT-Zelle. Während des gesperrten Zustands wird in der  $n^-$ -Basis nur ein geringer Teil der elektrischen Feldstärke abgebaut. Anschließend erfolgt im hoch dotierten  $n^+$ -Puffer mit einem hohen Gradienten der Abbau der verbleibenden Feldstärke. Es resultiert ein trapezförmiger Feldverlauf. Zudem ergibt sich durch eine hohe Ladungsträgerdichte am Kollektor ein hoher

Abbildung 2.3.: Querschnitt eines PT-IGBT mit Feldverlauf im Sperren und Ladungsträgerkonzentration im Durchlass. Zeichnung nicht maßstabsgetreu.

Tailstrom beim Abschalten des PT-IGBT. Dieser ist jedoch von relativ kurzer Dauer, da die Ladungsträger schnell ausgeräumt werden können, sobald das elektrische Feld die hochdotierte Pufferschicht erreicht.

## 2.2. Non Punch Through IGBT

Im Gegensatz zum PT-IGBT erfolgt die Herstellung des NPT-IGBT auf einem homogenen n<sup>-</sup>-Substrat. Das p<sup>+</sup>-Gebiet am Kollektor wird durch Rückseitenimplantation aufgebracht. Diese Herstellungstechnologie erlaubt es, das p<sup>+</sup>-Gebiet dünn zu halten, wodurch der Emitterwirkungsgrad herabgesetzt wird. Diese Maßnahme minimiert beim NPT-IGBT die Gefahr des Einrastens [34, 41]. Eine Ladungsträgerlebensdauereinstellung ist dabei nicht notwendig [61].

Wie in Abbildung 2.4 zu sehen ist, wird das elektrische Feld im gesperrten Zustand ausschließlich über die komplette n<sup>-</sup>-Basis abgebaut. Das resultierende dreieckförmige elektrische Feld erfordert ein dickeres n<sup>-</sup>-Gebiet als bei einem PT-IGBT der selben Spannungsklasse. In Folge der erhöhten Ausdehnung dieses Bauelements steigt die Durchlassspannung. Des Weiteren ist das Ausräumen der Ladungsträger zum Ende des Abschaltvorganges deutlich verlangsamt. Insgesamt ergibt sich im Vergleich zu einem PT-IGBT ein längerer Tailstrom, welcher durch den geringeren

Abbildung 2.4.: Querschnitt eines NPT-IGBT mit Feldverlauf im Sperren und Ladungsträgerkonzentration im Durchlass. Zeichnung nicht maßstabsgetreu.

Emitterwirkungsgrad und die dadurch niedrigere Ladungsträgerkonzentration am Rückseitenemitter jedoch kleiner ist.

### 2.3. Field Stop IGBT

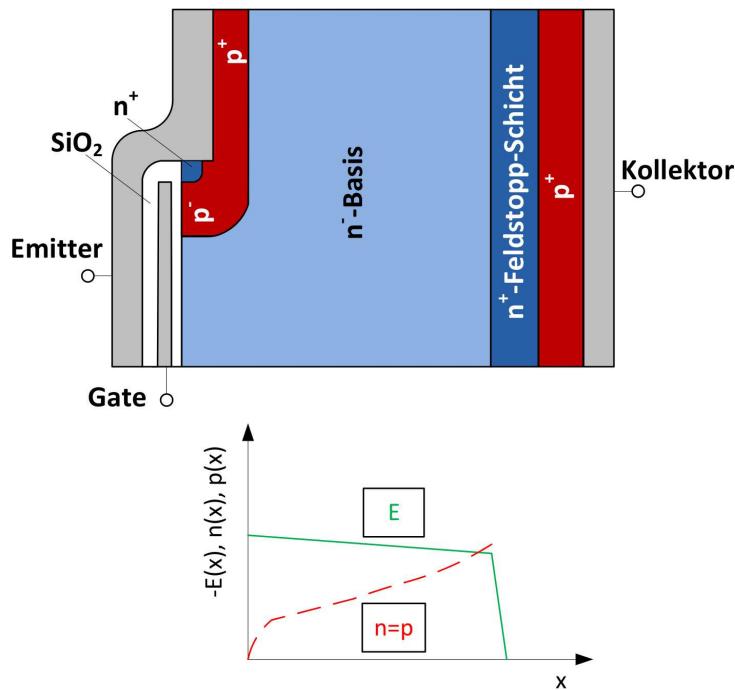

Der *Field Stop* IGBT kann grundsätzlich als Weiterentwicklung des NPT-IGBT verstanden werden. Um die Durchlassverluste zu reduzieren, wird hier vor der p<sup>+</sup>-Schicht am Kollektor eine hochdotierte n<sup>+</sup>-Schicht eingefügt (Abbildung 2.5). Die Herstellung erfolgt ähnlich wie beim NPT-IGBT und es resultiert daher grundsätzlich ein niedriger Emitterwirkungsgrad. Durch die kollektorseitige n<sup>+</sup>-Schicht (Feldstopp-Schicht) verhält sich das elektrische Feld jedoch wie beim PT-IGBT. Somit ist es möglich, die Dicke der n<sup>-</sup>-Basis weiter zu reduzieren und dadurch die Durchlassverluste zu minimieren. Betrachtet man die Ladungsträgerdichte an der Feldstopp-Schicht, so ist jene durch den dünnen Rückseitenemitter (p<sup>+</sup>-Gebiet am Kollektor) geringer als beim PT-IGBT. Erreicht das elektrische Feld beim Abschaltvorgang die Feldstopp-Schicht, werden die verbleibenden Ladungsträger in kürzester Zeit ausgeräumt. Folglich ergibt sich bei diesem IGBT-Typ ein niedriger und kurzer Tailstrom zum Ende des Ausschaltens. Je nach Hersteller werden IGBTs dieser Bauweise unterschiedlich benannt: *Field Stop* IGBT (FS-IGBT: Infineon [29]), *Soft Punch Through* IGBT (SPT-IGBT: ABB [46]), *Thin Wafer Punch Through* IGBT (TWPT-IGBT: Toshiba [35]) oder *Light Punch Through* IGBT (LPT-IGBT: Mitsubishi [38]). Im weiteren Verlauf der Arbeit findet ausschließlich der Begriff *Field Stop* IGBT beziehungsweise der deutsche Begriff Feldstopp-IGBT Verwendung.

Abbildung 2.5.: Querschnitt eines FS-IGBT mit Feldverlauf im Sperren und Ladungsträgerkonzentration im Durchlass. Zeichnung nicht maßstabsgetreu.

## 2.4. Trench Gate IGBT und Carrier Stored IGBT

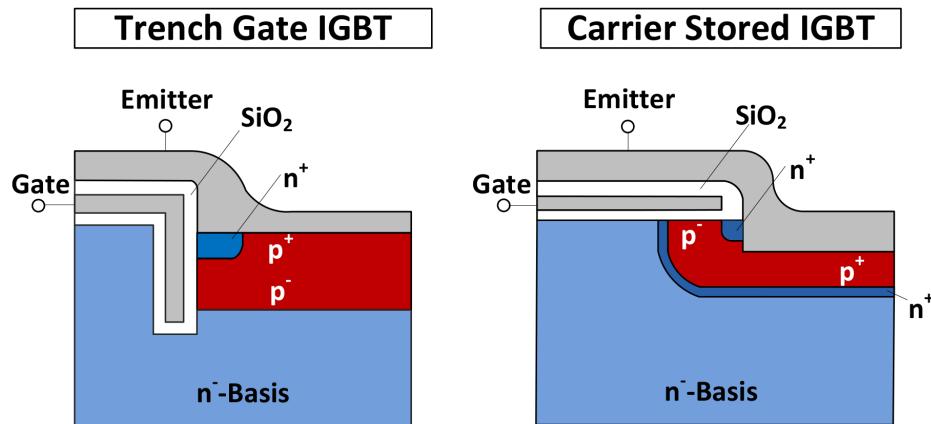

Weitere Innovationen zur Reduktion der Durchlassverluste und der Durchlassspannung stellen der *Trench Gate* IGBT und der *Carrier Stored* IGBT dar. Bei beiden Typen führen Veränderungen an der Vorderseite der Zellstruktur zu einem Verhalten, welches einer PIN-Diode (*Positive Intrinsic Negative Diode*) ähnelt. Um dies zu erreichen, wird im eingeschalteten Zustand die Ladungsträgerkonzentration der n<sup>-</sup>-Basis am Emitter erhöht. Im Folgenden werden diese IGBT-Typen kurz erläutert und in Abbildung 2.6 vergleichend gegenüber gestellt.

Beim *Trench Gate* IGBT wird der MOS-Kanal in Form eines Grabens vertikal ausgeführt. Beim MOSFET führt diese *Trench Gate* Technologie zur Verringerung des Kanalwiderstandes, welche bei bipolaren hochsperrenden Bauelementen jedoch eine Nebensächliche Rolle spielt. Dies verschlechtert zunächst die Kurzschlussfestigkeit des IGBTs. Um die Kurzschlussfestigkeit beizubehalten, wird nicht jedes Gate von außen kontaktiert. Diese werden Tote-Trench-Gates oder *Plugged Cells* genannt. Alternativ wird der Abstand der Zellen vergrößert (*wide pitch*). Dies erhöht zwar den Kanalwiderstand des IGBTs, führt aber zu einer Ladungsträgeranhebung am Emitter, welche vermutlich auf die höhere Stromdichte an den verbleibenden Zellen zurückzuführen ist. Neben der Verminderung der Durchlassverluste ergeben sich weitere Vorteile. So können zum einen die Durchbruchspannung und die Stromtragfähigkeit erhöht werden und zum anderen die *Latch Up* Gefahr minimiert werden [41, 23]. Nachteilig ist jedoch eine höhere Gatekapazität, welche bei jedem Schaltvorgang umgeladen werden muss. Dies erhöht den Anspruch an die Leistungsauslegung der Ansteuerungsschaltung [61]. Ein Beispiel eines *Trench Gate* IGBT mit *Field Stop* Schicht ist der IGBT der dritten Generation von Infineon [43].

Der *Carrier Stored* IGBT bedient sich eines anderen Verfahrens um die Ladungsträgerkonzentration im Durchlass zu erhöhen. In diesem Fall wird eine zusätzliche n<sup>+</sup>-dotierte Schicht an der p-Wanne eingeführt (Löcherbarriere), dies führt zur Anhebung der Ladungsträgerkonzentration an der Oberseite des Bauelements. Hierdurch steigt die Emittereffizienz. Einen Nachteil dieses Konzeptes stellt die verringerte Sperrfähigkeit durch die zusätzliche n<sup>+</sup>-Schicht an der p-Wanne dar. Um die Sperrfähigkeit des Bauelements dennoch zu erhalten, muss dieses dicker ausgelegt werden. Hierdurch werden wiederum die Durchlassspannung und damit auch die Durchlassverluste erhöht und ein kleiner Anteil des Vorteils geht somit wieder verloren [34]. Ein Bauteil, in dem das *Carrier Stored* Konzept Anwendung findet, ist der SPT<sup>+</sup>-IGBT der Firma ABB [12]. Mitsubishi setzt mit dem CSTBT (*Carrier Stored Trench*

*Gate Bipolar Transistor) auf eine Kombination aus Trench Gate IGBT und Carrier Stored IGBT [56].*

Abbildung 2.6.: Querschnitt einer Trench Gate Zelle (links) und einer Carrier Stored Zelle (rechts). Zeichnung nicht maßstabsgetreu.

### 3. Funktionsweise von IGBTs

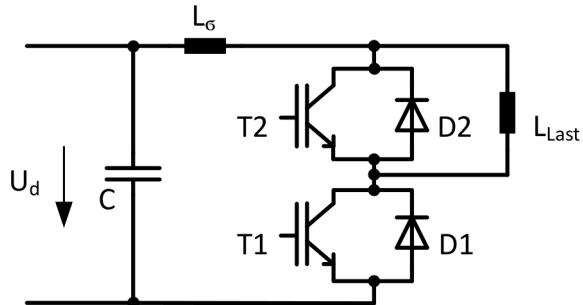

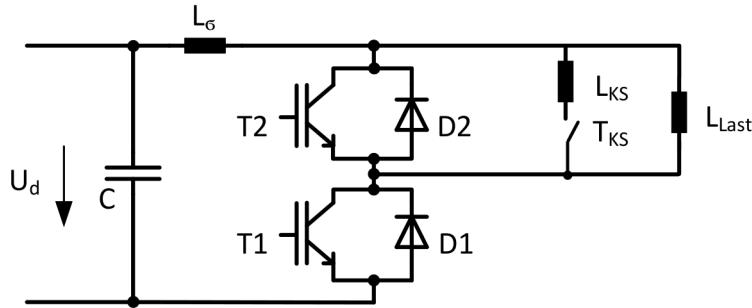

Dieses Kapitel beschreibt die Funktionsweise des IGBTs anhand eines einphasigen Spannungszwischenkreisumrichters (Halbbrücke) mit induktiver Last als Tiefsetzsteller. Die durch den Aufbau entstehenden parasitären Induktivitäten des Kommutierungskreises werden in Abbildung 3.1 zu einer Ersatzinduktivität  $L_\sigma$  zusammengefasst. Der Kommutierungskreis besteht aus einem IGBT (T1), einer gegenüberliegenden Freilaufdiode (D2) und einem Zwischenkreiskondensator C. Wird der IGBT (T1) eingeschaltet, so fließt ein Strom von der Zwischenkreiskapazität durch die Lastinduktivität zum IGBT – der Laststrom baut sich auf. Schaltet man den IGBT hingegen ab, so kommutiert der Strom vom IGBT (T1) in die Freilaufdiode (D2). Während der Schaltvorgänge können die Zwischenkreisspannung und der Laststrom als konstant angenommen werden.

Abbildung 3.1.: Einphasiger Spannungszwischenkreisumrichter mit induktiver Last als Tiefsetzsteller;  $T1, T2 = \text{IGBT}$ ;  $D1, D2 = \text{Diode}$

#### 3.1. Einschaltverhalten

Das Einschalten des IGBTs erfolgt, indem zwischen Gate und Emitter von T1 eine positive Spannung angelegt wird. Ansteuerseitig geschieht dies meist über eine schaltbare Spannungsquelle, welche hierfür über einen Widerstand mit dem Gate des IGBTs verbunden ist. Überschreitet die Gate-Emitter Spannung die Schwellspannung ( $U_{Th}$ ) des MOS-Kanals, entsteht auf Grund der Inversion ein leitender

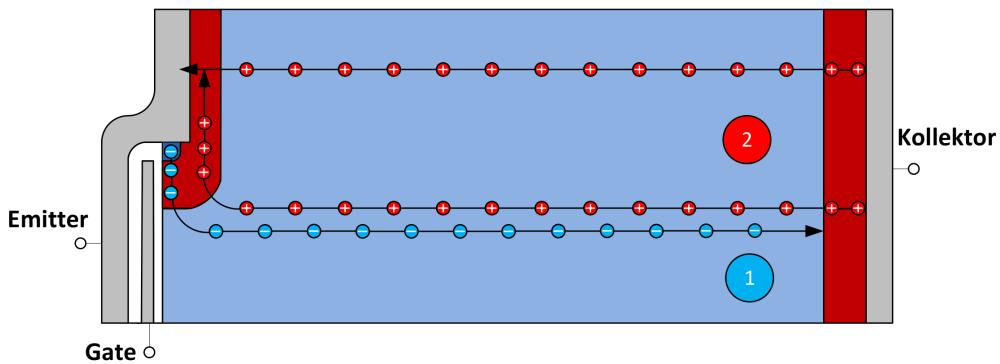

n-Kanal im p<sup>-</sup>-Gebiet der p-Wanne. Aus dem emitterseitigen n<sup>+</sup>-Gebiet in der p-Wanne fließen Elektronen als Majoritätsträger durch den leitenden Kanal in die n<sup>-</sup>-Basis und weiter in Richtung des Kollektors ab. Dieser Stromfluss in der n<sup>-</sup>-Basis führt zum Abbau der Raumladungszone und die elektrische Feldstärke sinkt. Bis hierhin verhält sich der IGBT wie ein n-Kanal MOSFET. Die Elektronen in der n<sup>-</sup>-Basis fließen zum Kollektor und überfluten den kollektorseitigen p<sup>+</sup>n<sup>-</sup>-Übergang, so dass dieser leitend wird. Dadurch werden Löcher als Minoritätsträger in die n<sup>-</sup>-Basis injiziert, welche zum Emitter fließen und den emitterseitigen n<sup>-</sup>-p<sup>+</sup>-Übergang leitend machen. Der Löcherstrom kann über den Emitter abfließen, wie Abbildung 3.2 verdeutlicht. Die Elektronen und Löcher bilden in der n<sup>-</sup>-Basis das Plasma, welches die Leitfähigkeit des IGBTs erhöht. Hierdurch kommt der für Bipolartransistoren übliche niedrige Spannungsabfall U<sub>CE,Sat</sub> im Durchlass zustande.

Abbildung 3.2.: Funktionsweise einer NPT-Zelle beim Einschalten. Zeichnung nicht maßstabsgetreu.

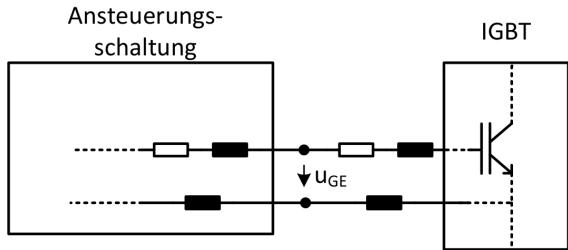

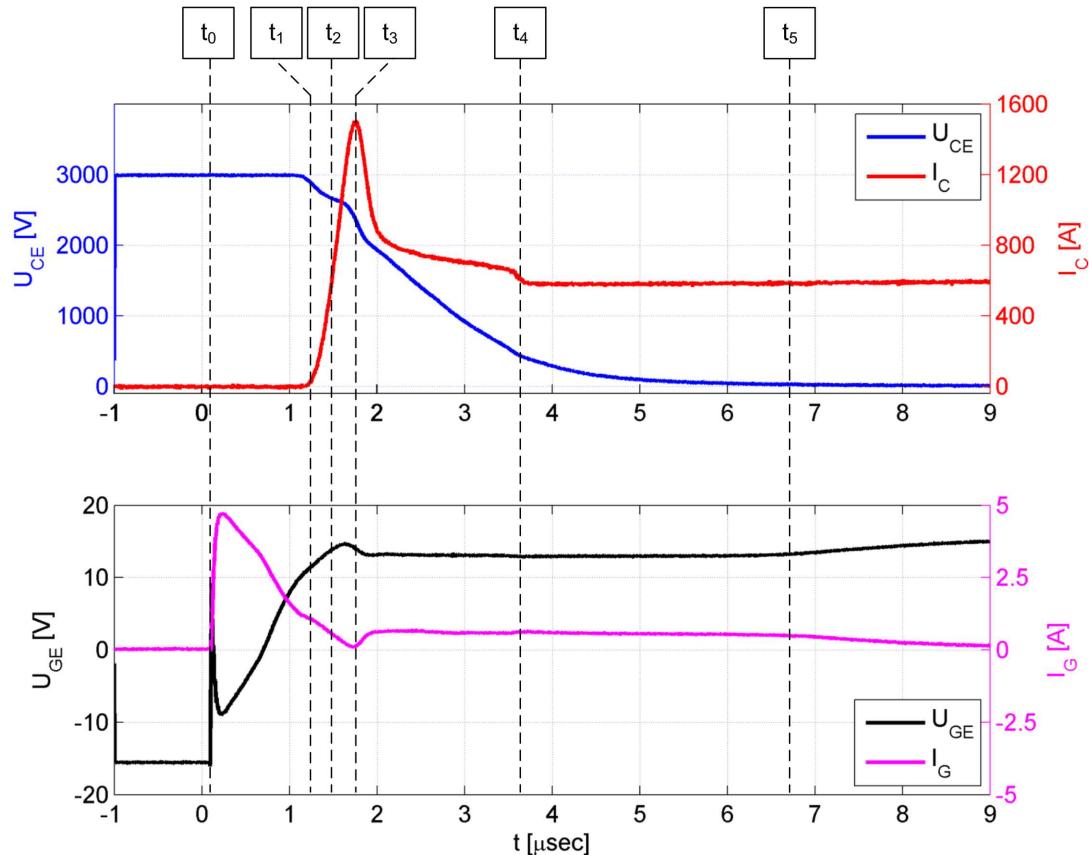

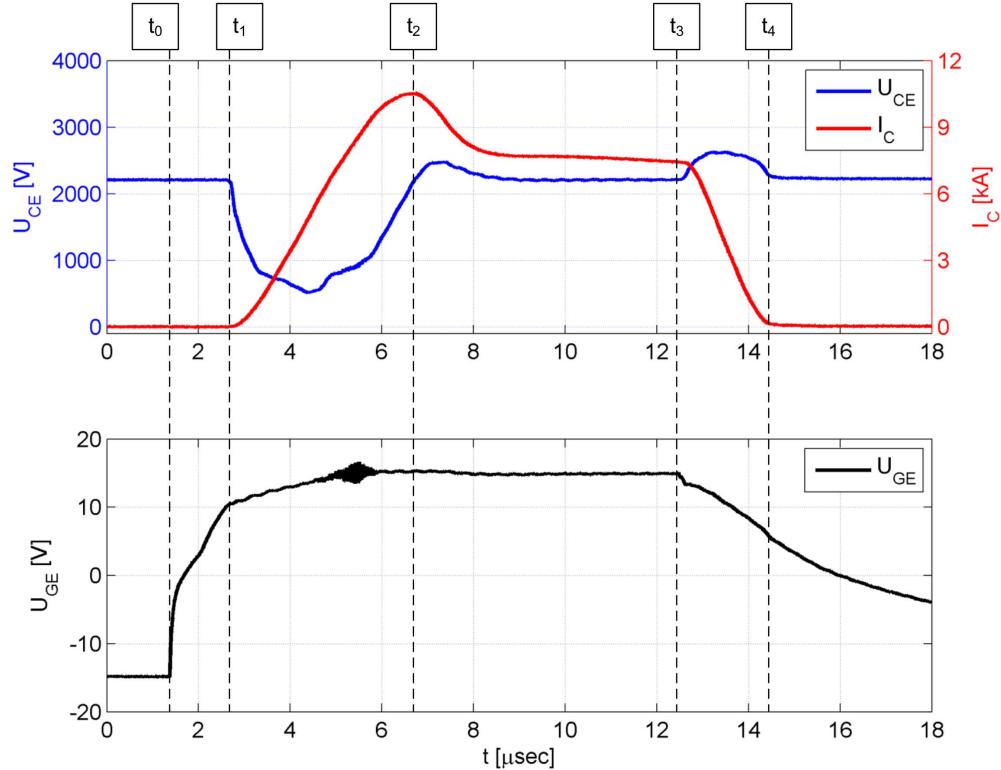

Abbildung 3.4 zeigt das Schaltverhalten eines 6,5 kV Feldstopp-IGBT beim Einschalten. Im ausgeschalteten Zustand liegt die volle Zwischenkreisspannung über dem Bauelement an. Dieser Messung liegt zugrunde, dass der IGBT T1 bereits leitend war, dann ausgeschaltet wurde und der Strom in die Diode D2 kommutiert ist (vgl. Abbildung 3.1). Während die Diode noch leitend ist, wird der IGBT T1 eingeschaltet und der Strom kommutiert von der Diode zurück in den IGBT. Die Gate-Emitter Spannung wurde direkt an der Ansteuerungsschaltung gemessen. Bedingt durch parasitäre Elemente zwischen der Ansteuerungsschaltung und dem IGBT kommt es zu Beginn des Umladevorganges des Gates zu einem induktiven Spannungsabfall zum Zeitpunkt t<sub>0</sub>. Abbildung 3.3 veranschaulicht den Aufbau.

Zum Zeitpunkt t<sub>0</sub> beginnt der Umladevorgang des Gates mit einer positiven Spannung auf 15 V (U<sub>TR,On</sub>). Der Verlauf der Gatespannung wird durch den Gatewiderstand auf der Ansteuerungsschaltung, dem internen Gatewiderstand des Moduls

Abbildung 3.3.: Messaufbau mit parasitären Elementen. Messung der Gate-Emitter Spannung am Ausgang der Ansteuerungsschaltung

Abbildung 3.4.: Einschaltverhalten eines 6,5 kV - 600 A IGBTs (FZ600R65KF1) mit induktiver Last – Kommutierung von Freilaufdiode auf IGBT – Messung mit einfacher Nennstrom bei 3000 V Zwischenkreisspannung – Oben: Kollektor-Emitter Spannung und Kollektorstrom; Unten: Gatespannung am Ausgang der Ansteuerungsschaltung und Gatestrom

$(R_{G,int})$  und der Eingangskapazität bestimmt. Diese wiederum setzt sich aus der Gate-Emitter Kapazität ( $C_{GE}$ ) und der Millerkapazität ( $C_{GC}$ ) zusammen. Letztere ist zu Beginn des Einschaltvorganges gegenüber der Gate-Emitter Kapazität relativ klein

und spielt hier daher eine untergeordnete Rolle. Der Verlauf der Gatespannung ergibt sich aus folgender Zeitkonstante:

$$\tau = (C_{GE} + C_{GC}) \cdot (R_{G,On} + R_{G,int}) \quad (3.1)$$

Während der Schaltvorgänge kann der Gatestrom aus der angelegten Treiberspannung ( $U_{TR,On}$ ), der Gatespannung ( $u_{GE}$ ) und dem Gatewiderstand ( $R_{G,On}$ ) ermittelt werden. Hierbei wurden die parasitären Elemente des Gatekreises aus Abbildung 3.3 vernachlässigt:

$$i_G = \frac{U_{TR,On} - u_{GE}}{R_{G,On}} \quad (3.2)$$

Der Kollektorstrom des IGBTs beginnt zu steigen, wenn das Gate bei  $t_1$  die Schwellspannung  $U_{Th}$  erreicht. Die Stromänderung  $di_C/dt$  ist sowohl vom Gatestrom als auch von der Steilheit  $g_m(i_C)$  des IGBTs abhängig. Sie führt dazu, dass es wegen der parasitären Induktivität  $L_\sigma$  im Kommutierungskreis (Abbildung 3.1) zu einem Spannungseinbruch der Kollektor-Emitter Spannung kommt.

$$U_d - u_{CE} = L_\sigma \cdot \frac{di_C}{dt} \quad (3.3)$$

Der Strom durch die Diode kommutiert nun in den IGBT. Hingegen verbleibt der Strom der Lastinduktivität unverändert und die Diode verbleibt im leitenden Zustand. Zum Zeitpunkt  $t_2$  erreicht der Kollektorstrom des IGBTs die Höhe des Laststroms. Aufgrund der Speicherladung wird der Strom durch die Diode negativ (*Reverse Recovery*). Auf diese Weise werden Ladungsträger aus der Diode aktiv abgebaut. Am Zeitpunkt  $t_3$  erreicht der Strom durch die Diode einen negativen Spitzenwert. Aus dem Laststrom und dem negativen Strom durch die Diode setzt sich der Strom zusammen, welcher durch den IGBT fließt.

Als Folge des Ausräumens der Speicherladung kann die Diode zwischen  $t_2$  und  $t_3$  Sperrspannung aufnehmen und die Kollektor-Emitter Spannung des IGBTs sinkt. Zum Zeitpunkt  $t_4$  sind die Ladungsträger aus der Diode abgebaut und der IGBT trägt nur noch den Laststrom. Um die Sättigungsspannung des IGBTs im Durchlass zu erreichen, muss die Millerkapazität  $C_{CG}$  vollständig vom Gatestrom umgeladen werden. Der Strom durch die Millerkapazität bestimmt dabei den Gradienten der Kollektor-Emitter Spannung. Die Rückwirkung der Millerkapazität auf das Gate führt während des Umladevorganges zu einem Plateau der Gatespannung (Millerpla-

teau). Das Millerplateau ergibt sich dabei aus der Schwellspannung, dem Laststrom und der Steilheit des IGBTs [52].

$$U_{GE,Plateau} = U_{Th} + \frac{I_{Last}}{g_m(i_C)} \quad (3.4)$$

Zum Zeitpunkt  $t_5$  ist der Umladevorgang abgeschlossen und die Kollektor-Emitter Spannung erreicht die Sättigungsspannung. Nach  $t_5$  wird das Gate auf die angelegte Treiberspannung  $U_{TR,On}$  von 15 V nachgeladen.

### 3.2. Ausschaltverhalten

Zum Abschalten von IGBTs wird üblicherweise das Gate über einen Widerstand auf 0 V oder eine negative Spannung, in diesem Fall -15 V ( $U_{TR,Off}$ ), entladen. Hierdurch fällt die Gatespannung auf einen Wert unterhalb der Schwellspannung ab und der n-leitende Kanal im p<sup>-</sup>-Gebiet der p-Wanne wird abgeschnürt. Als Folge reißt der Elektronenstrom zum Kollektor ab. Der Abbau von den in der n<sup>-</sup>-Basis verbleibenden Minoritätsträgern erfolgt hauptsächlich über das Ausbreiten der Raumladungszone. Zum Ende des Abschaltvorganges breitet sich diese jedoch nur noch bedingt aus. Daher werden die restlichen Ladungsträger lediglich langsam abgebaut. Diese Umstände führen zu dem für Bipolartransistoren üblichen Tailstrom.

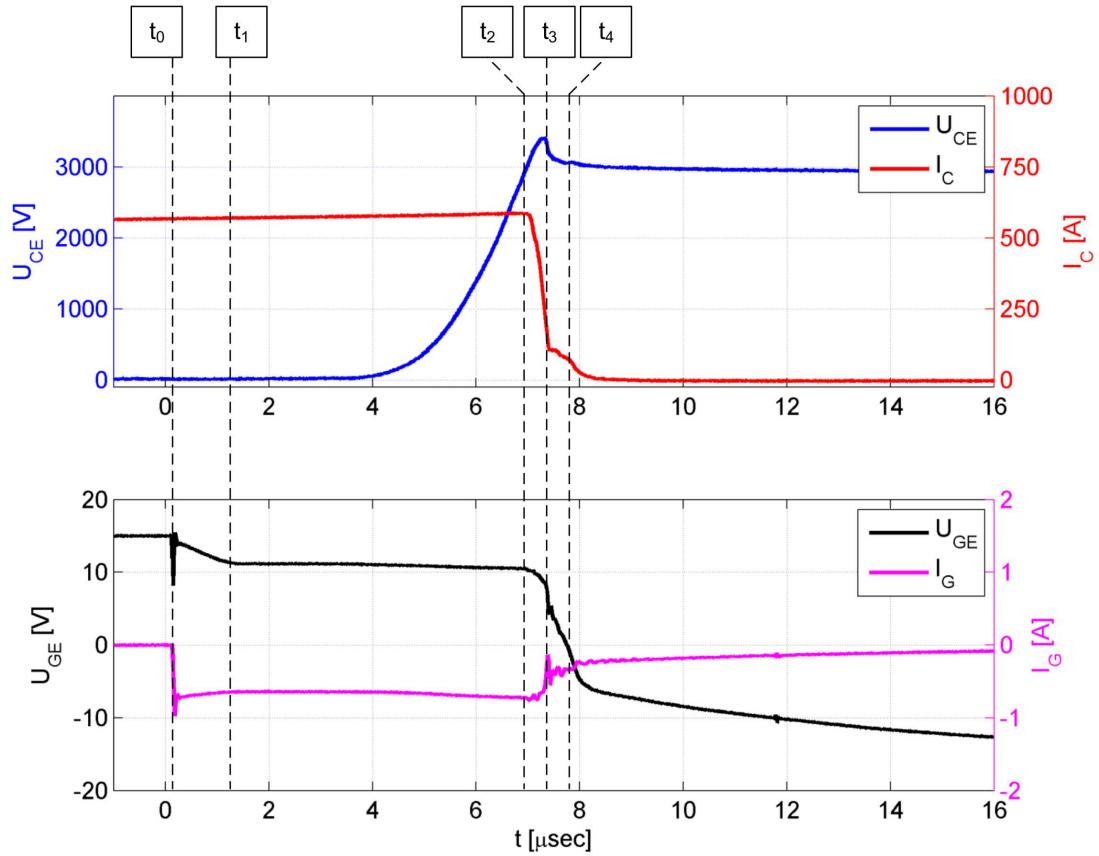

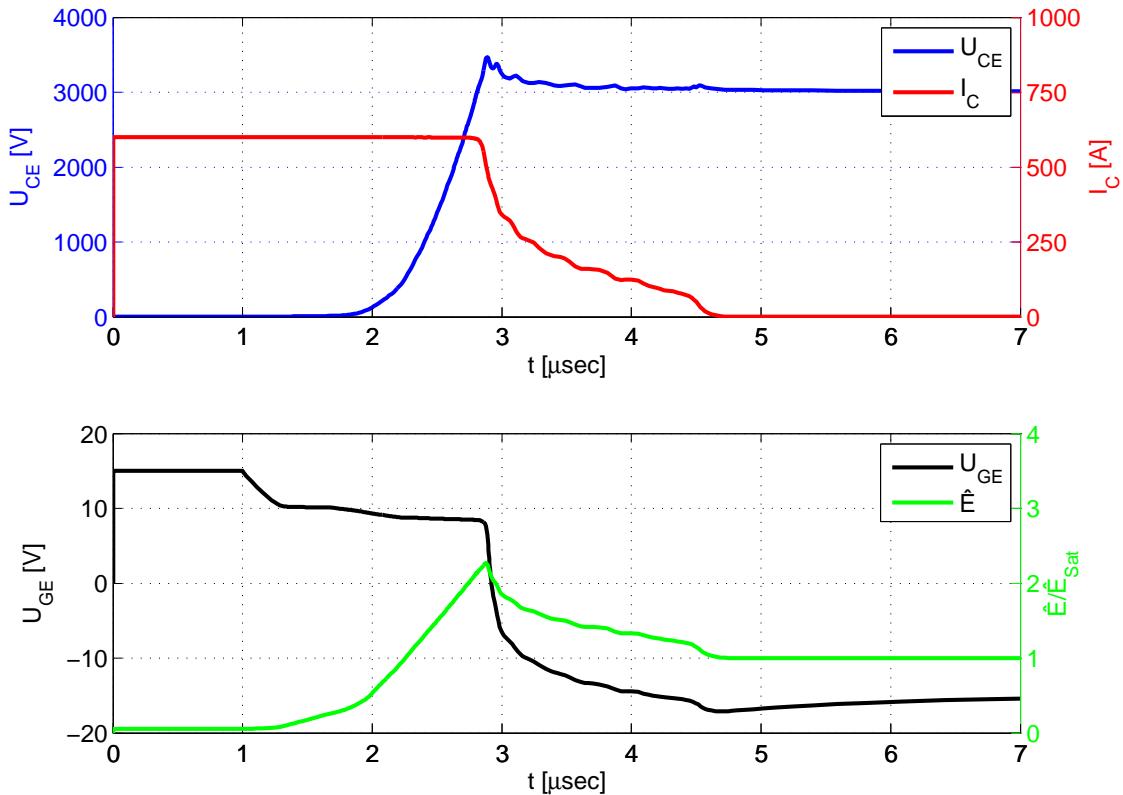

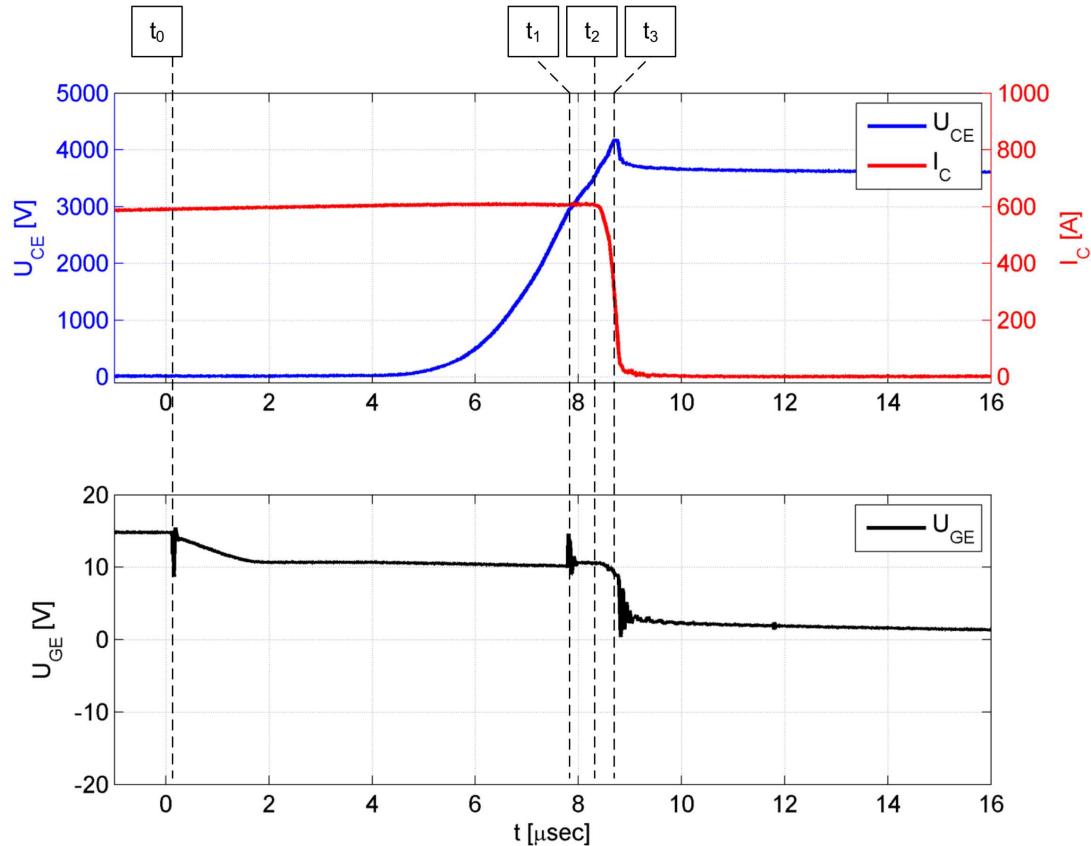

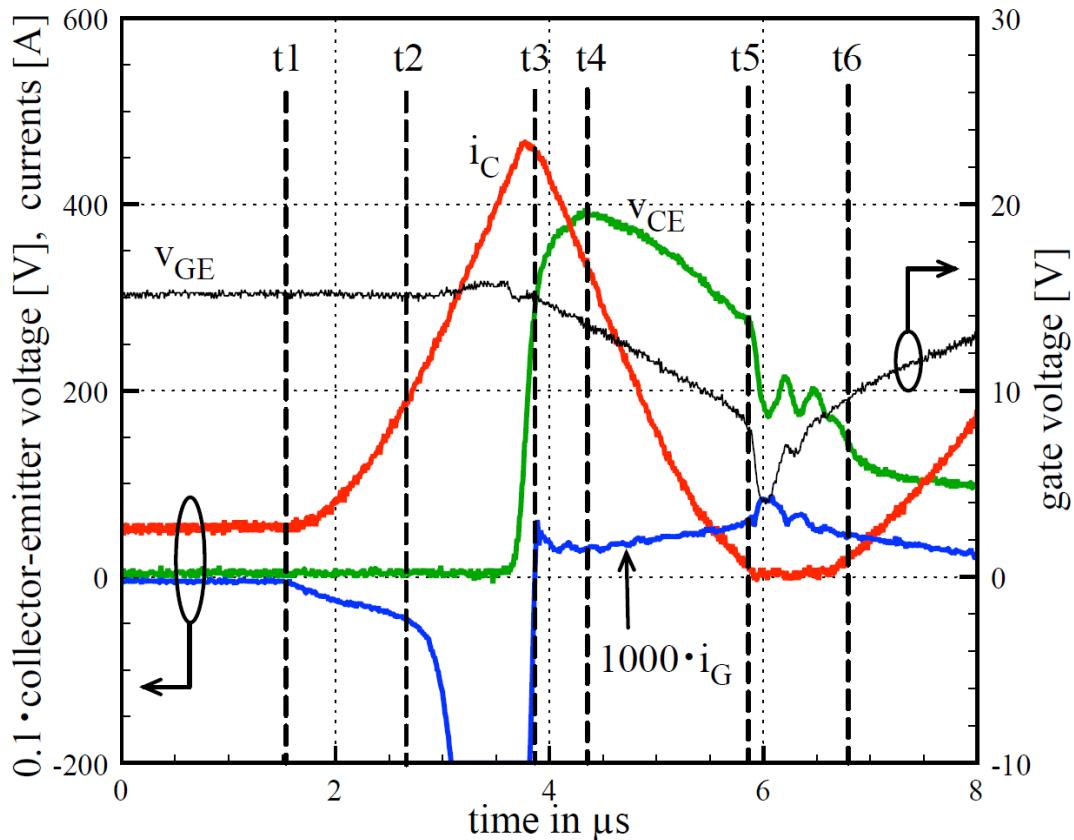

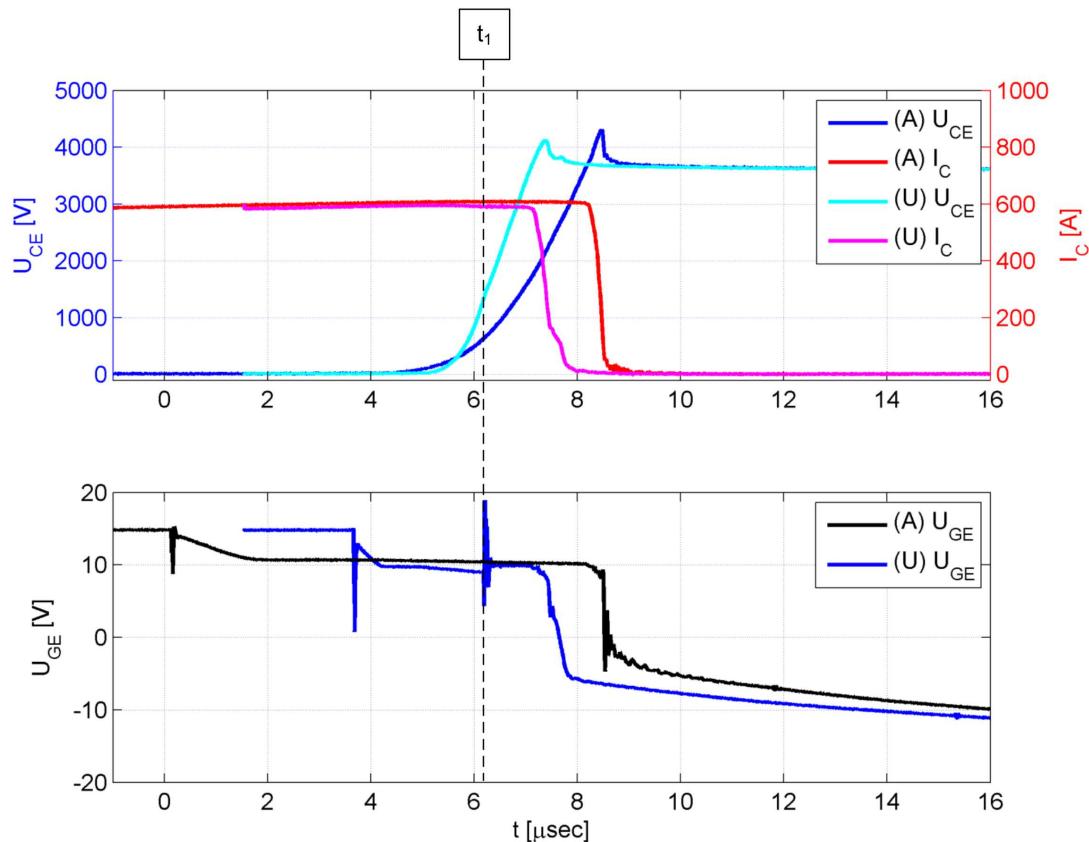

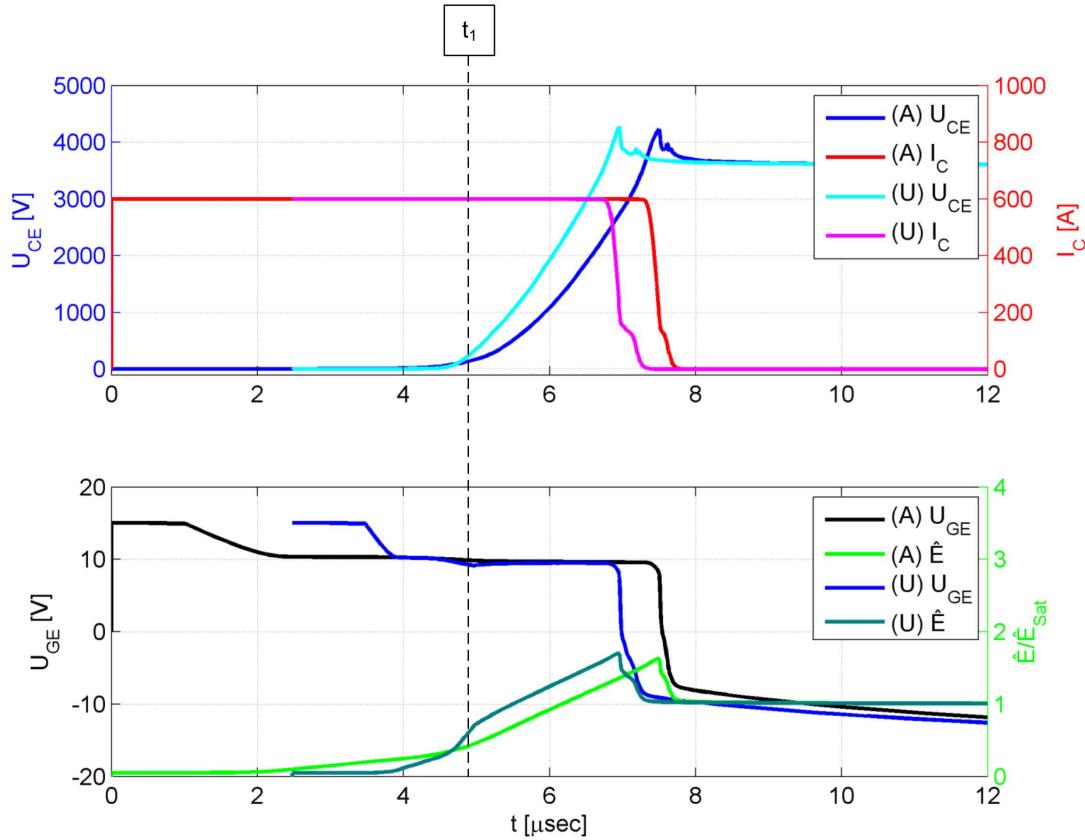

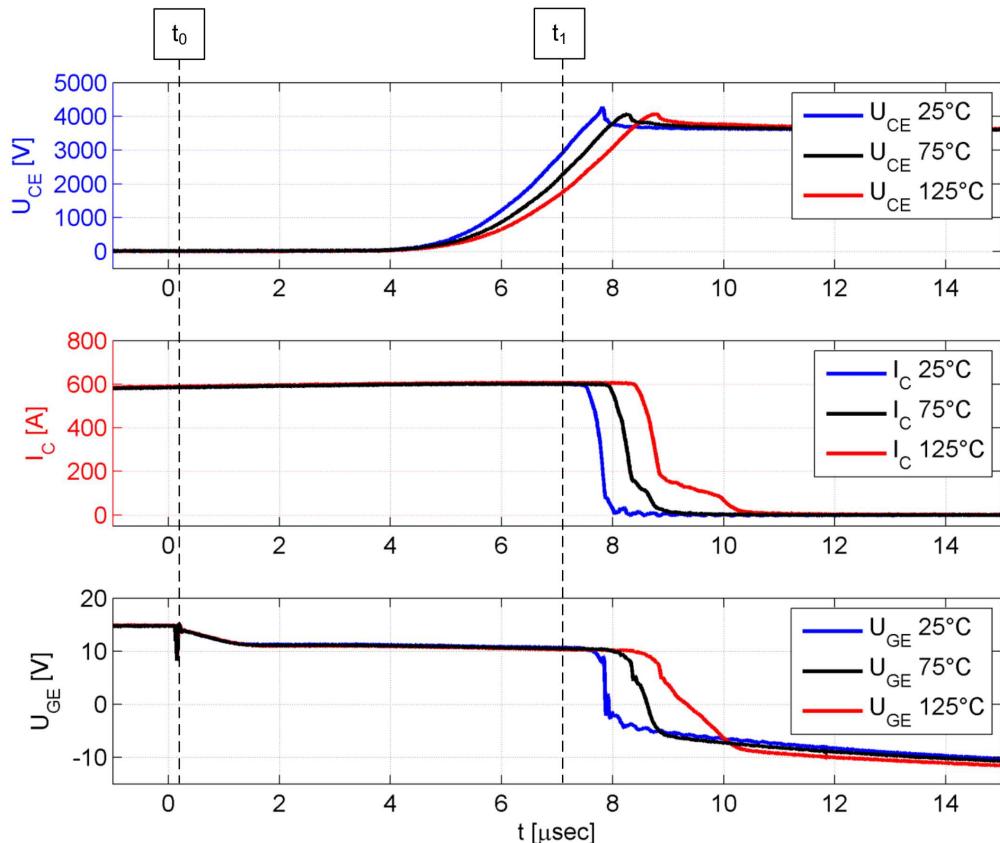

Abbildung 3.5 zeigt das Abschaltverhalten eines 6,5 kV Feldstopp-IGBT. Zum Zeitpunkt  $t_0$  beginnt der Abschaltvorgang. Auf Grund der parasitären Elemente, wie in Abbildung 3.3 gezeigt, ergibt sich zu diesem Zeitpunkt ein induktiver Spannungsabfall am Ausgang der Ansteuerungsschaltung. Analog zum Einschaltvorgang wird der Verlauf der Gatespannung durch die Eingangskapazitäten bestimmt. In diesem Fall spielt die Millerkapazität jedoch keine vernachlässigbare Rolle. Der resultierende Verlauf der Gatespannung kann durch folgende Zeitkonstante beschrieben werden. Analog zum Einschaltverhalten gilt:

$$\tau = (C_{GE} + C_{GC}) \cdot (R_{G,Off} + R_{G,int}) \quad (3.5)$$

Auch bei diesem Schaltvorgang kann der Gatestrom wie beim Einschalten aus der Treiberspannung und den Gatewiderstand ermittelt werden. Dabei sind die parasitären Elemente des Gatekreises aus Abbildung 3.3 vernachlässigt.

$$i_G = \frac{U_{TR,Off} - u_{GE}}{R_{G,Off}} \quad (3.6)$$

Durch die Rückwirkung der Millerkapazität  $C_{CG}$  auf das Gate erreicht die Gatespannung bei  $t_1$  den Wert des Millerplateaus. Hier kann der Laststrom gerade noch

Abbildung 3.5.: Ausschaltverhalten eines 6,5 kV - 600 A IGBTs (FZ600R65KF1) mit induktiver Last – Kommutierung von IGBT auf Freilaufdiode – Messung mit einfacherem Nennstrom bei 3000 V Zwischenkreisspannung – Oben: Kollektor-Emitter Spannung und Kollektorstrom; Unten: Gatespannung am Ausgang der Ansteuerungsschaltung und Gatestrom

aufrecht gehalten werden. Der Wert des Millerplateaus lässt sich ebenfalls analog zum Einschaltvorgang bestimmen (Gleichung 3.4) [52]. Später wird allerdings gezeigt, dass das Millerplateau sowohl vom eingestellten Gateentladestrom als auch vom Anstieg der Kollektor-Emitter Spannung abhängig ist. Auf Grund der Stromquellencharakteristik der Lastinduktivität fließt der Strom unverändert weiter. Während des Millerplateaus lädt der Gatestrom die Millerkapazität ( $C_{CG}$ ) um und der IGBT nimmt Spannung auf. Da die Millerkapazität bei geringer Spannung  $u_{CG}$  einen hohen Wert aufweist, steigt die Kollektor-Emitter Spannung nur gering an. Im weiteren zeitlichen Verlauf beginnt die Millerkapazität zu fallen. Es kommt zu einem starken Anstieg der Kollektor-Emitter Spannung. Zum Zeitpunkt  $t_2$  erreicht die Kollektor-Emitter Spannung die Zwischenkreisspannung und übersteigt die Flussspannung der Diode D2 (Abbildung 3.1). Diese ist nun in Flussrichtung gepolt und der Laststrom kann in die Diode D2 kommutieren. Auf Grund der parasitären Induktivitäten ( $L_\sigma$ ) im Kommutierungskreis führt die Kommutierung des Laststromes

vom IGBT in die Diode zu einer Überspannung. Aus der Zwischenkreisspannung ( $U_d$ ), der *Forward Recovery* Spannung der Diode und dem Spannungsabfall an den parasitären Induktivitäten lässt sich diese wie folgt berechnen:

$$U_{CE,max} = U_d + U_{FR} + L_\sigma \cdot \frac{di_C}{dt} \quad (3.7)$$

Zum Zeitpunkt  $t_3$  bildet sich der für IGBTs übliche Tailstrom aus. Die Raumladungszone hat nahezu ihre statische Weite im Sperren erreicht. Die noch verbleibenden Ladungsträger in der n<sup>-</sup>-Basis werden sowohl durch den Tailstrom als auch über Rekombination abgebaut. Die Raumladungszone erreicht die Feldstopp-Schicht des IGBTs zum Zeitpunkt  $t_4$ . Hier können auf Grund der hochdotierten Feldstopp-Schicht mehr Ladungsträger pro Zeit abgebaut werden. Das elektrische Feld wird trapezförmig, der Kollektorstrom reißt ab und eine zweite kleinere Überspannungsspitze entsteht auf Grund der zeitlichen Änderung des Stromes. Nach  $t_4$  ist der Abschaltvorgang des IGBTs beendet und der Laststrom vollständig in die Diode kommutiert. Die Gatekapazität wird auf den stationären Wert von -15 V nachgeladen.

### 3.3. Kurzschlussverhalten

Der IGBT ist auf Grund seiner Struktur kurzschlussfest, da über die Gate-Emitter Spannung der maximal mögliche Kollektorstrom begrenzt wird [3, 34]. Bei einem Kurzschluss treten kurzzeitig hohe Spannungen und hohe Ströme gleichzeitig auf, dies ist eine hohe thermische Belastung für den IGBT. Der stationäre Kurzschlussstrom ist abhängig von der Gate-Emitter Spannung, welcher in den Datenblättern für eine Gate-Emitter Spannung von 15 V angegeben ist. Bevor es zu einem Ausfall des IGBTs kommt, muss der Kurzschluss von der Ansteuerungsschaltung erkannt und der IGBT innerhalb von typischerweise 10  $\mu$ s abgeschaltet werden. Neben der thermischen Belastung des IGBTs im Kurzschlussfall besteht auch die Gefahr, dass der IGBT auf Grund des hohen Kollektorstromes einrastet [34]. Der Kurzschluss kann dann nicht mehr abgeschaltet werden, was ebenfalls zum Ausfall führt. Weiterhin besteht eine hohe Belastung des IGBTs im Kurzschlussfall durch die auftretende Feldstärke. Hierbei entstehen an der Vorderseite und an der Rückseite des Bauelementes zwei Feldstärkespitzen [28]. Darüber hinaus entsteht beim Abschalten des Kurzschlusses eine hohe Überspannung, welche den IGBT ebenfalls zerstören kann. Aus diesem Grund muss die Abschaltgeschwindigkeit und somit das  $di_C/dt$  begrenzt werden. Am einfachsten wird dies über einen größeren Gatewiderstand erreicht. Man spricht hier von einem *Soft Turn Off* [59]. Durch die thermische Belastung des Bau-

elementes kann auch nach erfolgreicher Abschaltung des Kurzschlussstromes der IGBT thermisch weglauen. In diesem Fall ist der Sättigungssperrstrom, durch die im Kurzschluss entstandene Erwärmung, im ausgeschalteten Zustand erhöht. Dies führt zu einer weiteren Erwärmung des Bauelementes durch die auftretende Verlustleistung und kann damit zu einer thermischen Zerstörung des IGBTs führen.

Abbildung 3.6.: Erweiterung des einphasigen Spannungszwischenkreisumrichters aus Abbildung 3.1 mit induktiver Last als Tiefsetzsteller für Kurzschlussmessungen;  $T_1, T_2 = \text{IGBT}$ ;  $D_1, D_2 = \text{Diode}$ ;  $T_{KS} = \text{Parallelschaltung aus IGBTs}$

Abbildung 3.6 zeigt den Messaufbau für die Kurzschlussmessungen. Der Kommutierungskreis aus Abbildung 3.1 wird hierbei um eine Kurzschlussinduktivität  $L_{KS}$  und einen Kurzschlusschalter  $T_{KS}$  erweitert. Der Kurzschlusschalter besteht aus bis zu drei parallelgeschalteten IGBTs, welche mit einer erhöhten Gate-Emitter Spannung eingeschaltet werden und somit den Kurzschluss einleiten können. Dabei werden zwei Kurzschlussfälle unterschieden [34, 45, 54].

### 3.3.1. Kurzschlussfall I

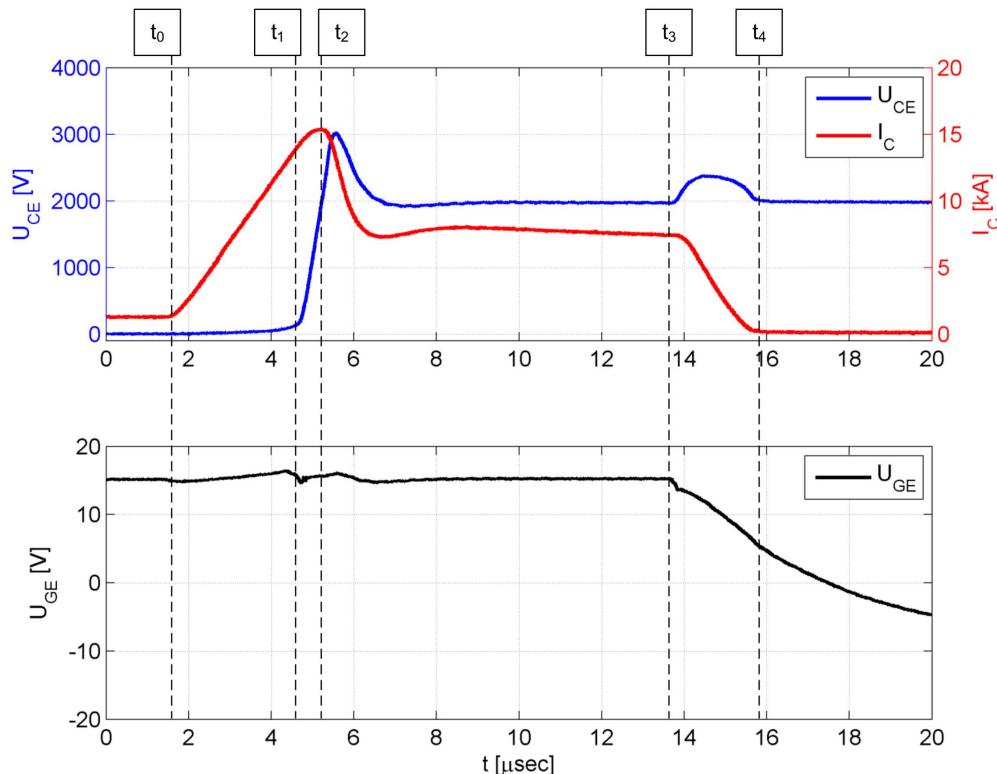

Beim Kurzschlussfall I wird der IGBT auf einen bestehenden ausgangsseitigen Kurzschluss eingeschaltet. Dazu wird der Schalter  $T_{KS}$  aus Abbildung 3.6 geschlossen, bevor der IGBT  $T_1$  eingeschaltet wird.

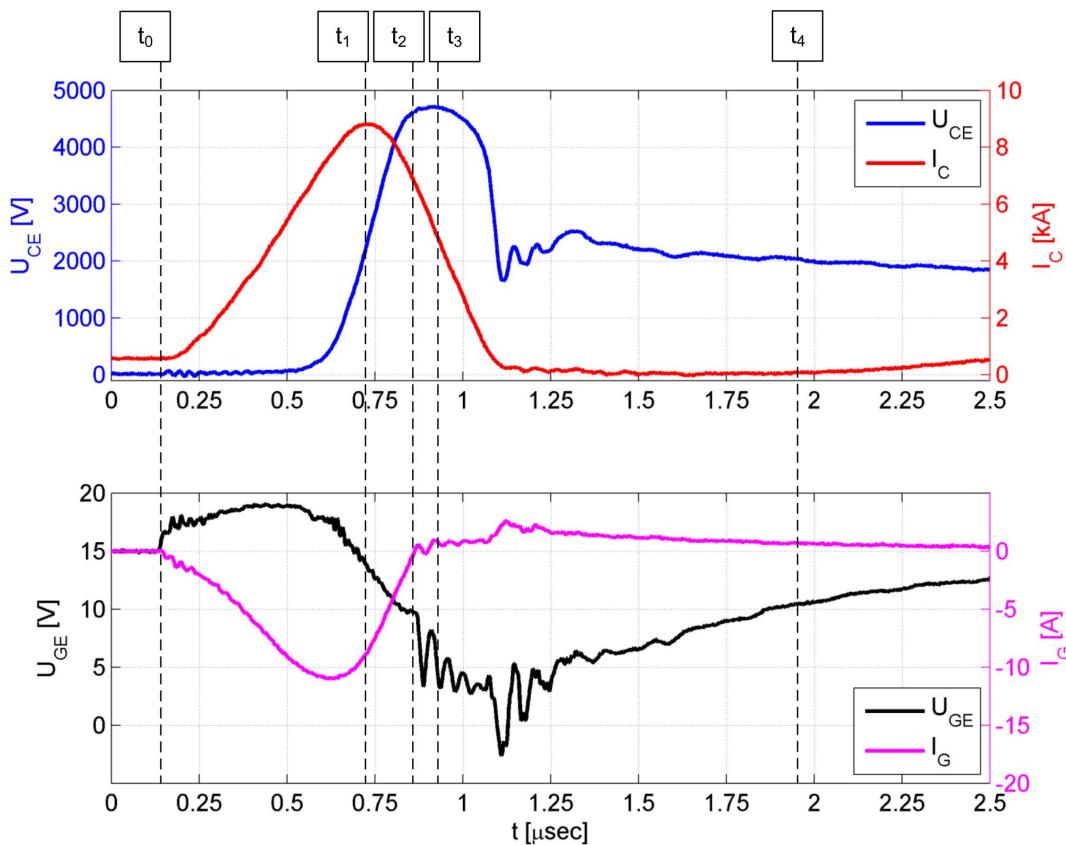

Abbildung 3.7 zeigt ein Messergebnis des Kurzschlussfalls I. Der Kurzschließer  $T_{KS}$  ist geschlossen, bevor zum Zeitpunkt  $t_0$  der IGBT  $T_1$  eingeschaltet wird. Zum Zeitpunkt  $t_1$  erreicht die Gate-Emitter Spannung die Schwellspannung und der Kollektorstrom steigt bis  $t_2$  auf die Überstromspitze von 10,5 kA an. Zwischen  $t_1$  und  $t_2$  kommt es auf Grund der Kollektorstromänderung zu einem Spannungsabfall an der Kurzschlussinduktivität  $L_{KS}$  und der Streuinduktivität  $L_\sigma$ . Dies lässt die Kollektor-Emitter Spannung zunächst sinken, bis sie zum Zeitpunkt  $t_2$  wieder die Zwischenkreisspannung erreicht. Durch das positive  $dU_{CE}/dt$  fließt über die Millerkapazität des IGBTs ein Verschiebestrom, welcher die Gate-Emitter Kapazität auf etwas über 15 V auflädt. Somit kann der Kollektorstrom auf den Wert der Überstromspitze an-

Abbildung 3.7.: Kurzschlussfall I eines 4,5 kV - 1200 A IGBTs (CM1200HC90RA) – Messung mit 2200 V Zwischenkreisspannung – Oben: Kollektor-Emitter Spannung und Kollektorstrom; Unten: Gatespannung am Ausgang der Ansteuerungsschaltung

steigen. Die Ansteuerungsschaltung versucht diesem Effekt entgegenzuwirken und die Gate-Emitter Spannung sinkt nach  $t_2$  auf 15 V. Dies führt zu einem negativen  $di_C/dt$ , bis der Kollektorstrom den statischen Kurzschlussstrom erreicht. Das negative  $di_C/dt$  verursacht auf Grund der Induktivitäten eine erste Überspannung. Auf Grund der Erwärmung des Bauteils sinkt der stationäre Kurzschlussstrom bis zum Zeitpunkt  $t_3$  leicht. Zum Zeitpunkt  $t_3$  wird der IGBT abgeschaltet. Der Gatewiderstand ist hierbei erheblich größer als beim betriebsmäßigen Ausschaltvorgang. Der Kurzschlussstrom fällt ab und es entsteht eine zweite Überspannungsspitze. Zum Zeitpunkt  $t_4$  ist der Kollektorstrom auf den Wert Null abgesunken und die volle Zwischenkreisspannung liegt am IGBT an. Der Kurzschluss wurde erfolgreich abgeschaltet.

### 3.3.2. Kurzschlussfall II

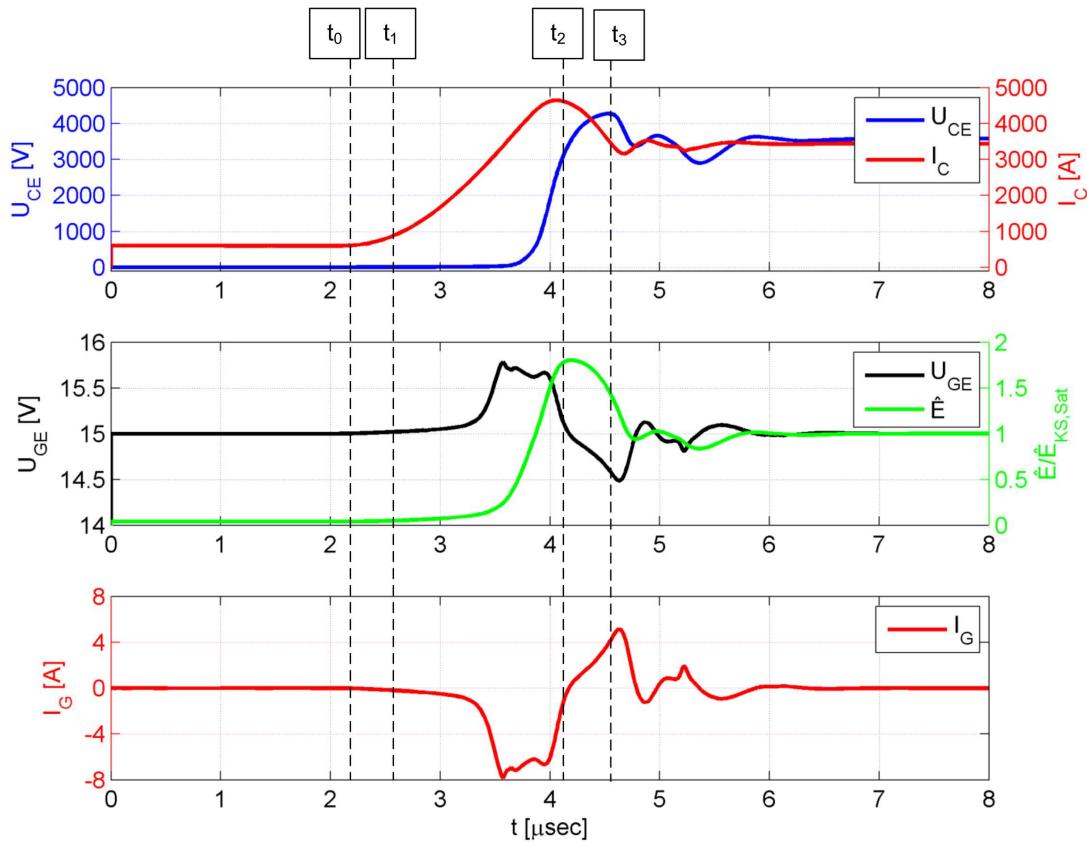

Beim Kurzschlussfall II hingegen wird, während der IGBT T1 eingeschaltet ist und seinen Laststrom führt, der Schalter T<sub>KS</sub> aus Abbildung 3.6 eingeschaltet und damit der Kurzschluss eingeleitet.

Abbildung 3.8.: Kurzschlussfall II eines 4,5 kV - 1200 A IGBTs (CM1200HC90RA) – Messung mit 2000 V Zwischenkreisspannung – Oben: Kollektor-Emitter Spannung und Kollektorstrom; Unten: Gatespannung am Ausgang der Ansteuerungsschaltung

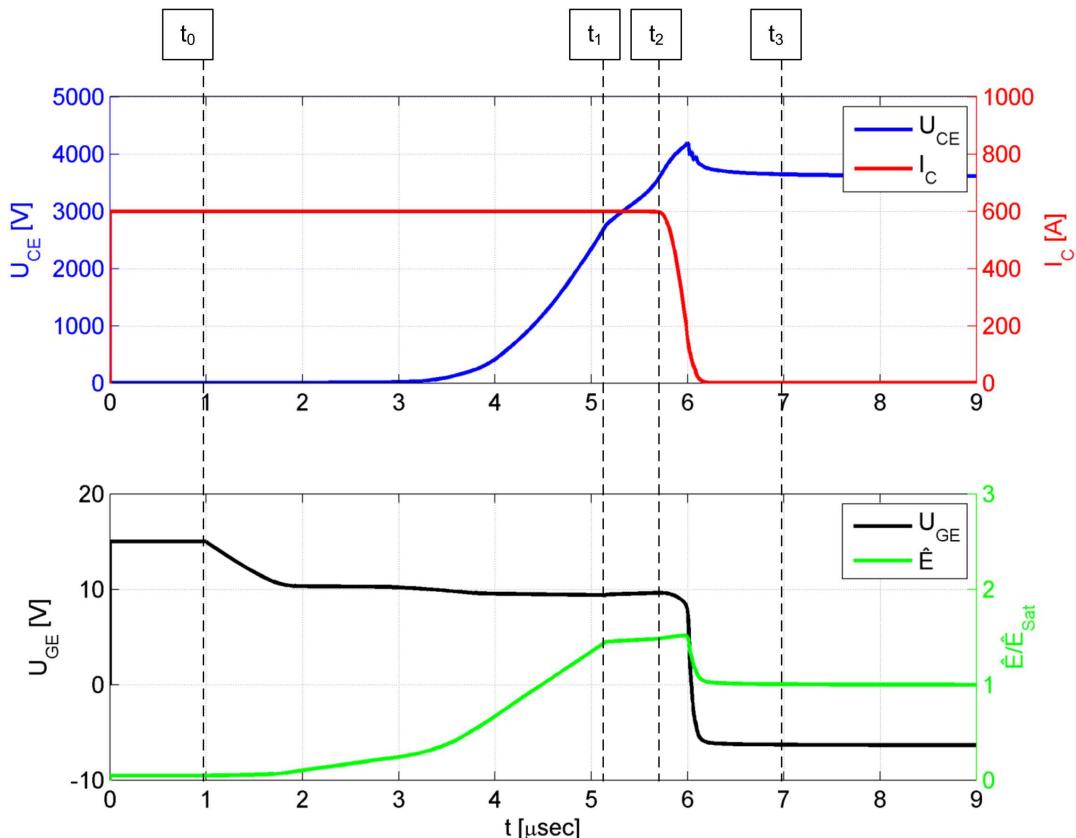

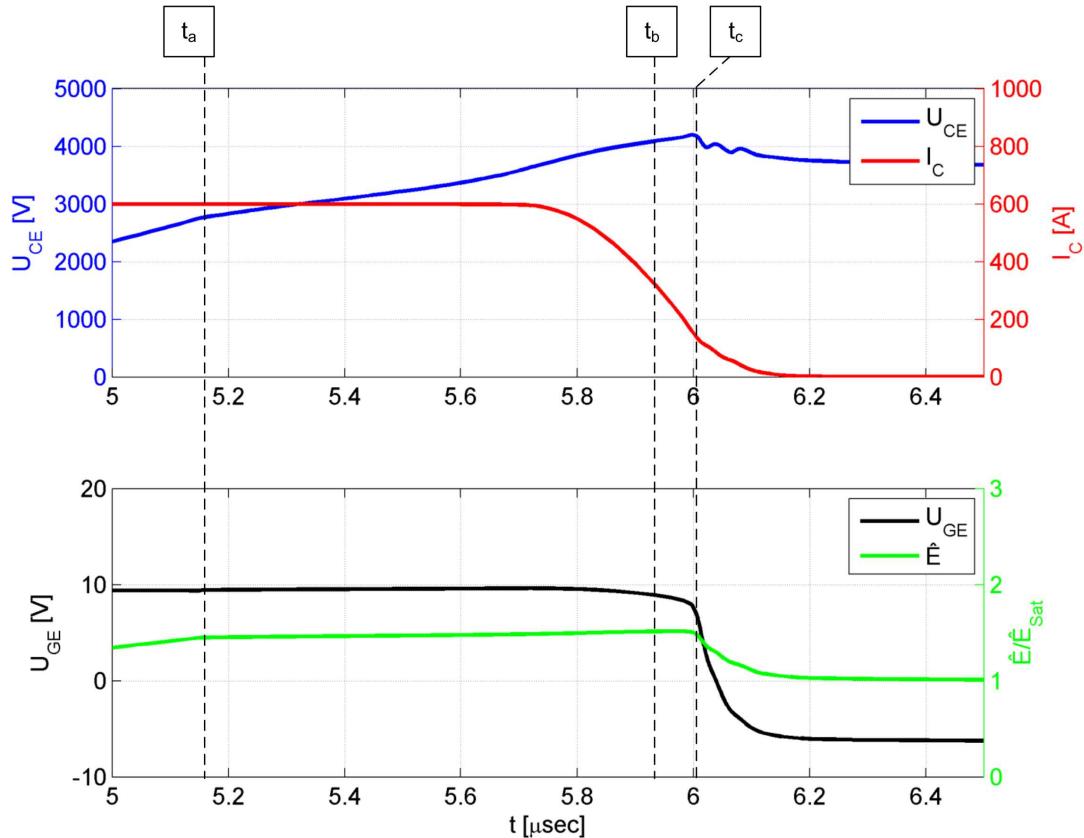

Ein Messergebnis des Kurzschlussfalls II ist in Abbildung 3.8 zu sehen. Der IGBT ist eingeschaltet und führt seinen Laststrom in Höhe des Nennstromes, als zum Zeitpunkt  $t_0$  der Kurzschließer T<sub>KS</sub> aktiviert wird. Es kommt zum Anstieg des Kollektorstroms. Der Gradient der Kollektor-Emitter Spannung ist leicht positiv und die Gatespannung wird angehoben. Zum Zeitpunkt  $t_1$  beginnt der IGBT zu entsättigen, was zu einem sehr steilen  $dU_{CE}/dt$  führt. Hierbei wird die Gatespannung erneut angehoben und von der Ansteuerungsschaltung auf ungefähr 17 V begrenzt. Zum Zeitpunkt  $t_2$  erreicht die Kollektor-Emitter Spannung die Zwischenkreisspannung und die dynamische Überstromspitze von ca. 15 kA wird erreicht. Die Gate-Emitter Spannung fällt daraufhin auf 15 V ab und der Kollektorstrom sinkt auf den stati-

schen Kurzschlussstrom. Dieses negative  $di_C/dt$  führt auf Grund der Induktivitäten wie beim Kurzschlussfall I zu einer ersten Überspannungsspitze. Der stationäre Kurzschlussstrom sinkt auch hier auf Grund der hohen Verlustleistung, welche im Bauteil in Wärme umgesetzt wird. Ab  $t_3$  wird der IGBT mit einem höheren Gatewiderstand als im Normalbetrieb abgeschaltet. Das sinkende  $di_C/dt$  führt zu einer zweiten Überspannungsspitze, bis zum Zeitpunkt  $t_4$  der Kurzschlussfall II erfolgreich abgeschaltet wurde.

## 4. IGBT Ansteuerungen

In diesem Kapitel wird eine Übersicht über IGBT-Ansteuerungsschaltungen gegeben. Dabei liegt der Fokus bei Widerstandsansteuerungen, welche auch die üblichen industriellen Realisierungen sind. In [61] werden zusätzlich Ansteuerungstopologien vorgestellt, bei welchem das Gate mit Hilfe von Stromquellen und Spannungsquellen ohne Gatewiderstand umgeladen wird. Allerdings finden sich kaum Literaturstellen zu dieser Vorgehensweise. Meist werden Stromquellen in Verbindung mit einer Widerstandsansteuerung angewendet. In den folgenden Unterkapiteln werden verschiedene Ansteuerungsschaltungen zur Verbesserung der Schalteigenschaften vorgestellt. Dabei wird hauptsächlich auf eine Begrenzung der Überstromspitze beim Einschalten und auf die Überspannung beim Abschalten des Leistungshalbleiters eingegangen. Abschließend werden Schutzschaltungen für IGBTs vorgestellt.

### 4.1. Ansteuerungsschaltungen nach dem Prinzip der Widerstandsansteuerung

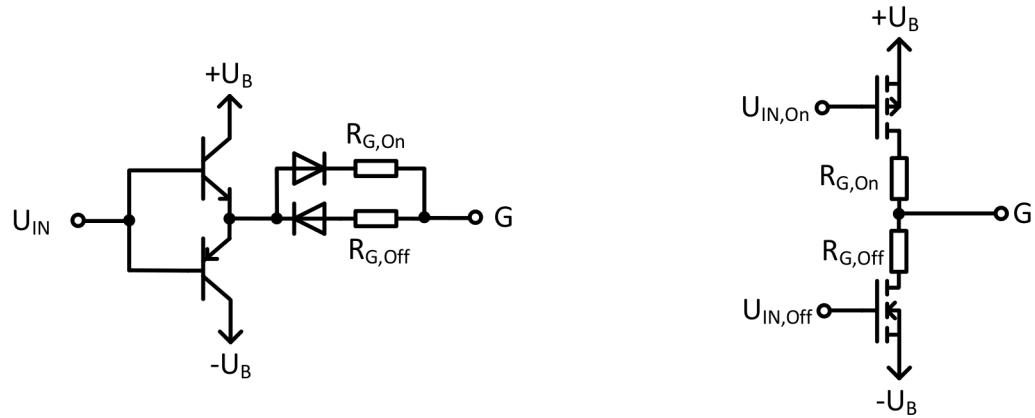

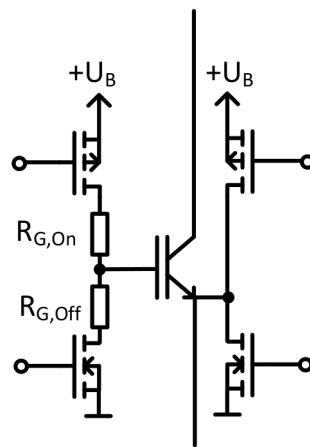

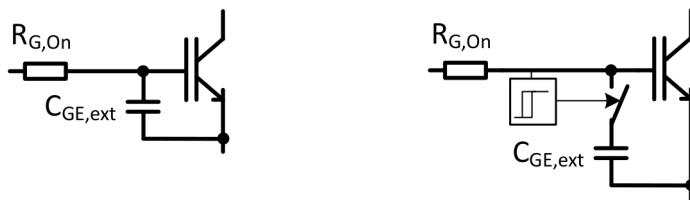

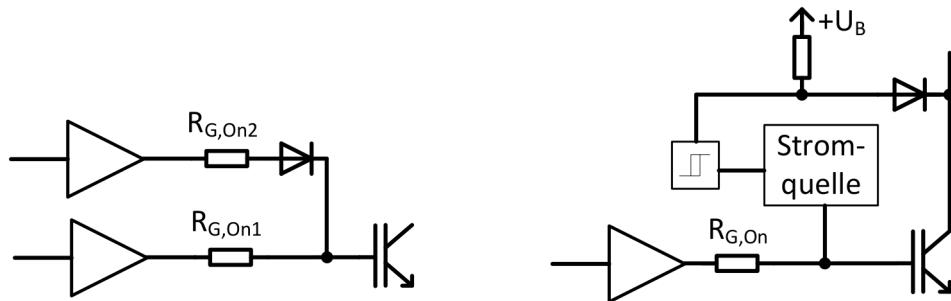

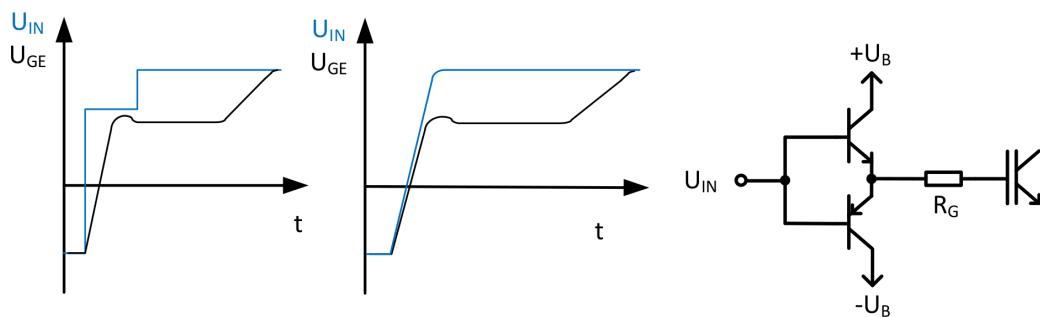

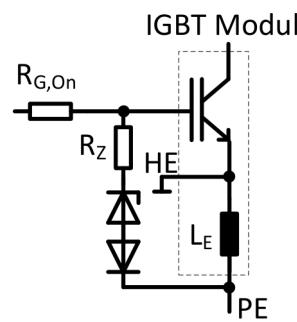

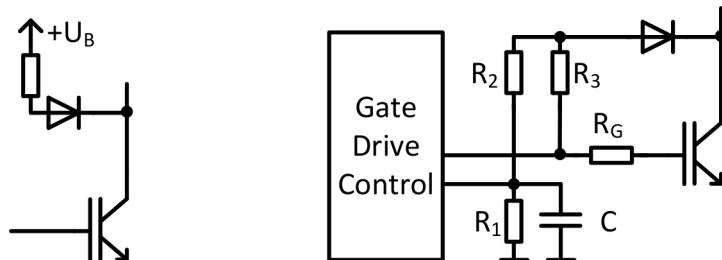

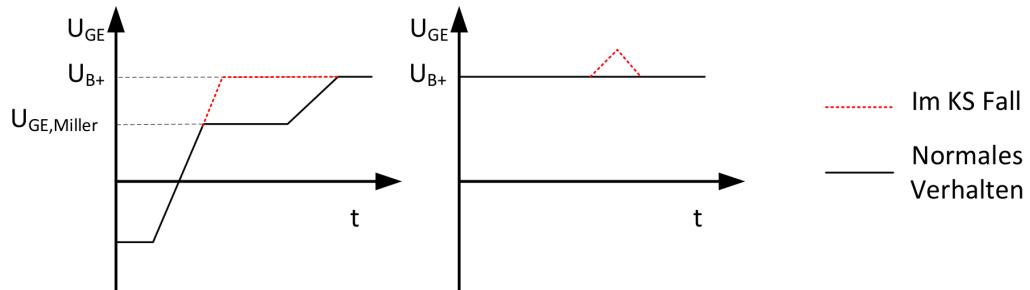

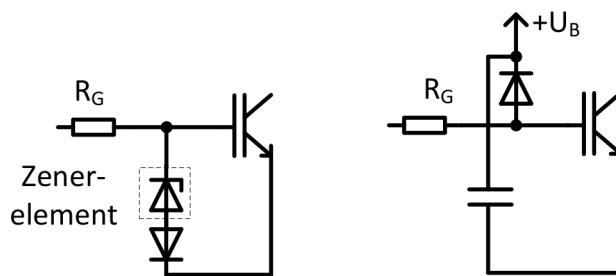

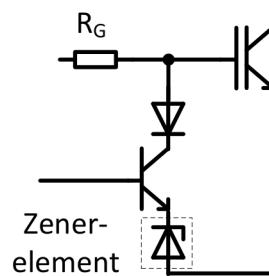

Bei der am häufigsten verwendeten Ansteuerungstopologie wird mit Hilfe eines Gatewiderstandes und mit einer Spannungsquelle das Gate des IGBTs umgeladen. Hierbei stehen zur Beeinflussung des Schaltverhaltens grundsätzlich zwei Einstellungsmöglichkeiten zur Verfügung. Zum einen können mit dem Wert des Gatewiderstandes und zum anderen mit dem Wert der treibenden Spannung ( $U_{TR,On}$  üblicherweise +15 V und  $U_{TR,Off}$  üblicherweise eine negative Spannung [36, 59, 61]) die Schalteigenschaften beeinflusst werden. In [1] und [61] werden je ein Gatewiderstand zum Ein- und zum Ausschalten des IGBTs vorgeschlagen, um diese Schaltvorgänge unabhängig voneinander einzustellen. Zwei einfache Realisierungen zeigt Abbildung 4.1.