# Modellierung und Steuerung der Temperaturverteilung Network-on-Chip-basierter Systeme

Dissertation

zur

Erlangung des akademischen Grades

Doktor-Ingenieur (Dr.-Ing.)

der Fakultät für Informatik und Elektrotechnik

der Universität Rostock

vorgelegt von

Wegner, Tim, geb. am 24.06.1984 in Leisnig

aus Rostock

Rostock, den 02. Januar 2014

Gutachter:

- Prof. Dr.-Ing. Dirk Timmermann, Universität Rostock

- Prof. Dr. rer. nat. habil. Adelinde M. Uhrmacher, Universität Rostock

- Prof. Dr.-Ing. Rainer Kokozinski, Universität Duisburg-Essen

Tag der Einreichung: 02. Januar 2014

Tag der Verteidigung: 07. Juli 2014

# Danksagung

Die vorliegende Arbeit entstand während meiner wissenschaftlichen Tätigkeit am Institut für Angewandte Mikroelektronik und Datentechnik an der Universität Rostock.

An erster Stelle möchte ich meinem Doktorvater Prof. Dirk Timmermann danken, der diese Promotion überhaupt erst ermöglicht hat. Er sorgte neben der Anstellung am Institut für den Freiraum, der für die Fertigstellung dieser Dissertation essentiell war. Darüber hinaus sorgte er auch in schwierigen Phasen für die nötige Motivation und gab entscheidende Denkanstöße. In diesem Zusammenhang möchte ich auch meiner Betreuerin Prof. Adelinde Uhrmacher danken, welche meine Arbeit durch konstruktive Kritik bereicherte und mir stets mit Rat und Tat zur Seite stand.

Weiterhin möchte ich meiner Familie danken, die mich über die Jahre in allen Lebenslagen unterstützt und mir stets Kraft gegeben hat. Ohne sie und ihre Beständigkeit wäre diese Arbeit nie zustande gekommen.

Dank geht ebenfalls an meinen Kollegen und Bürogenossen Martin Gag, der mich tatkräftig unterstützt hat und durch die vielen wertvollen Diskussionen und Ratschläge für einen interessanten Arbeitsalltag gesorgt hat. Ein großes Dankeschön für fleißiges Korrekturlesen geht außerdem an die Kollegen Martin Gag, Peter Danielis und Philipp Gorski. Darüber hinaus danke ich dem gesamten Team des Instituts für die angenehme und harmonische Arbeitsatmosphäre und die schöne Zeit während meines Studiums.

# Inhaltsverzeichnis

|                                                                           |            |

|---------------------------------------------------------------------------|------------|

| <b>Abbildungsverzeichnis</b>                                              | <b>VII</b> |

| <b>Tabellenverzeichnis</b>                                                | <b>IX</b>  |

| <b>Abkürzungsverzeichnis</b>                                              | <b>XI</b>  |

| <b>1 Einleitung</b>                                                       | <b>1</b>   |

| <b>2 Ausgewählte Schwerpunkte hochintegrierter Systeme</b>                | <b>5</b>   |

| 2.1 Technologische Aspekte . . . . .                                      | 5          |

| 2.1.1 Entwicklung der Fertigungstechnologie . . . . .                     | 5          |

| 2.1.2 Kritische Faktoren . . . . .                                        | 6          |

| 2.2 Zuverlässigkeit . . . . .                                             | 10         |

| 2.2.1 Grundlagen und Definitionen . . . . .                               | 10         |

| 2.2.2 Ausfallursachen . . . . .                                           | 12         |

| 2.2.3 Einfluss der Temperatur . . . . .                                   | 15         |

| 2.2.4 Existierende Techniken zur Steigerung der Zuverlässigkeit . . . . . | 20         |

| 2.3 Kommunikationsstrukturen nanoelektronischer Systeme . . . . .         | 25         |

| 2.3.1 Überblick und analytischer Vergleich . . . . .                      | 26         |

| 2.3.2 Grundlagen NoC-basierter Systeme . . . . .                          | 31         |

| 2.3.3 NoC-Topologien . . . . .                                            | 38         |

| 2.3.4 Zuverlässigkeit NoC-basierter Systeme . . . . .                     | 42         |

| 2.4 Ermittlung der Temperatur hochintegrierter Schaltungen . . . . .      | 47         |

| 2.4.1 Messung mithilfe von Ringoszillatoren . . . . .                     | 48         |

| 2.5 Folgerung und Problemformulierung . . . . .                           | 53         |

| <b>3 Temperaturmodell</b>                                                 | <b>57</b>  |

| 3.1 Realisierung . . . . .                                                | 57         |

| 3.1.1 Dualismus elektrischer und thermischer Energie . . . . .            | 57         |

| 3.1.2 Stand der Technik . . . . .                                         | 59         |

| 3.1.3 Implementierung und Simulationsablauf . . . . .                     | 60         |

| 3.2 Bewertung des Modells . . . . .                                       | 70         |

| 3.2.1 Zeitverhalten . . . . .                                             | 72         |

| 3.2.2 Korrektheit des Modells . . . . .                                   | 78         |

| 3.2.3 Qualitative Bewertung und Zusammenfassung . . . . .                 | 84         |

| <b>4 Temperaturorientiertes Management NoC-basierter Systeme</b>          | <b>89</b>  |

| 4.1 Stand der Technik . . . . .                                           | 89         |

| 4.2 Anwendungsszenario I: Proaktives Temperaturmanagement . . . . .       | 94         |

| 4.2.1 Konzept . . . . .                                                   | 95         |

|                             |                                                            |            |

|-----------------------------|------------------------------------------------------------|------------|

| 4.2.2                       | Vergleich mit reaktivem Management und Bewertung . . . . . | 108        |

| 4.2.3                       | Zusammenfassung . . . . .                                  | 121        |

| 4.3                         | Anwendungsszenario II: Proaktives Task-Mapping . . . . .   | 124        |

| 4.3.1                       | Konzept . . . . .                                          | 124        |

| 4.3.2                       | Vergleich mit gängigen Konzepten und Bewertung . . . . .   | 128        |

| 4.3.3                       | Zusammenfassung . . . . .                                  | 134        |

| <b>5</b>                    | <b>Zusammenfassung und Ausblick</b>                        | <b>137</b> |

| 5.1                         | Zusammenfassung . . . . .                                  | 137        |

| 5.2                         | Ausblick . . . . .                                         | 140        |

| <b>Literaturverzeichnis</b> |                                                            | <b>143</b> |

# Abbildungsverzeichnis

|      |                                                                                                                                  |    |

|------|----------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Struktur der Arbeit . . . . .                                                                                                    | 4  |

| 2.1  | Die in einer digitalen Schaltung auftretenden Lade- und Kurzschlussströme am Beispiel eines Inverters . . . . .                  | 8  |

| 2.2  | Einfluss der Fertigungstechnologie auf die Transistor- und Verlustleistungsdichte . . . . .                                      | 9  |

| 2.3  | Lebenszyklus hochintegrierter Schaltungen . . . . .                                                                              | 11 |

| 2.4  | Klassifikation der Ursachen für das Fehlverhalten hochintegrierter Schaltungen . . . . .                                         | 13 |

| 2.5  | Einfluss eines Temperaturanstiegs auf die Time To Failure . . . . .                                                              | 19 |

| 2.6  | Kategorisierung der Strategien zur Erhöhung der Zuverlässigkeit . . . . .                                                        | 22 |

| 2.7  | Design-Productivity Gap . . . . .                                                                                                | 25 |

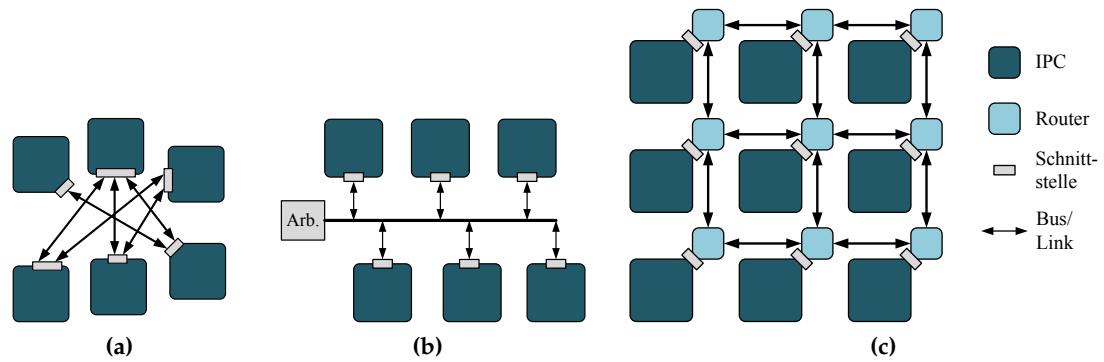

| 2.8  | Wichtige Kommunikationsarchitekturen: Punkt-zu-Punkt-Verbindung, Bus und NoC . . . . .                                           | 28 |

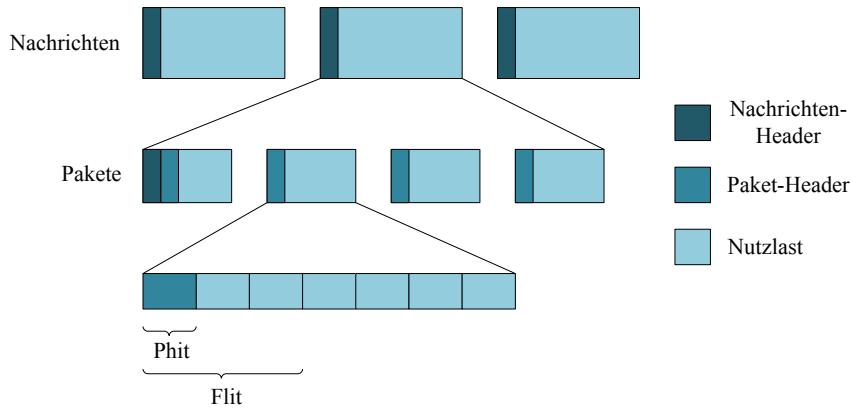

| 2.9  | Aufbau einer Nachricht . . . . .                                                                                                 | 32 |

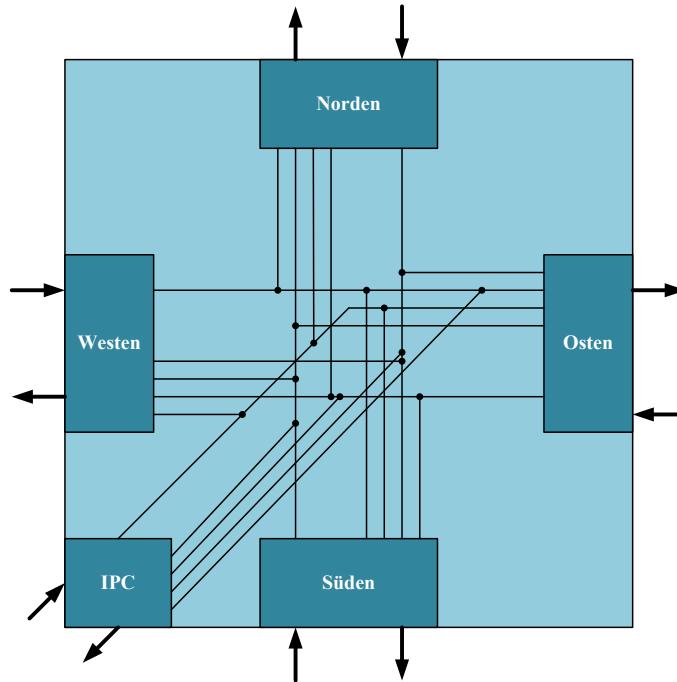

| 2.10 | Aufbau eines NoC-Routers . . . . .                                                                                               | 33 |

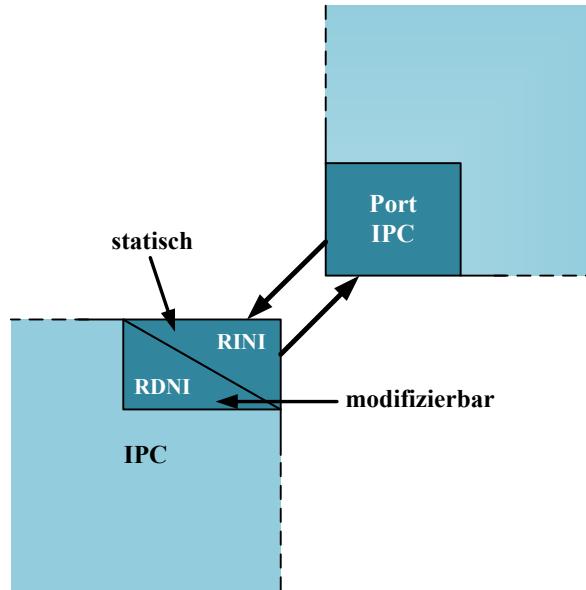

| 2.11 | NoC-Netzwerkschnittstelle . . . . .                                                                                              | 34 |

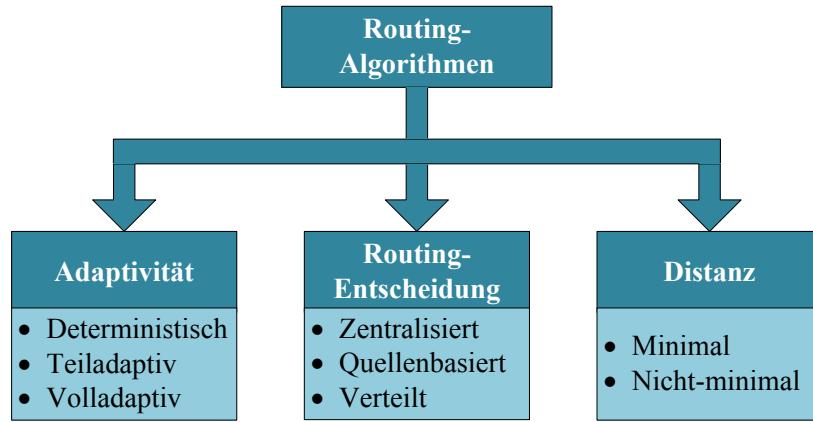

| 2.12 | Klassifikation der Routing-Algorithmen . . . . .                                                                                 | 36 |

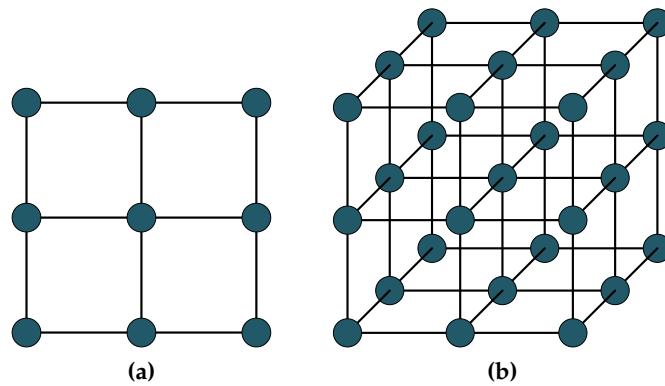

| 2.13 | Gitternetz: 2D-Gitter und 3D-Gitter . . . . .                                                                                    | 39 |

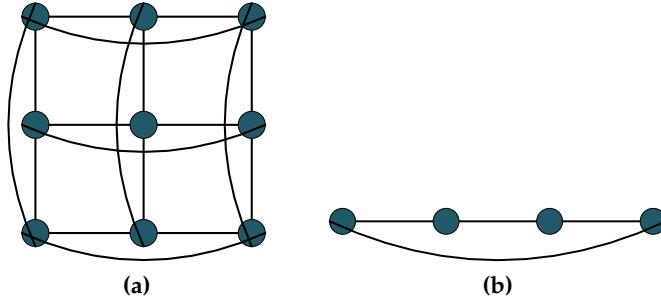

| 2.14 | Torus: 3-facher 2-Würfel und Ring . . . . .                                                                                      | 40 |

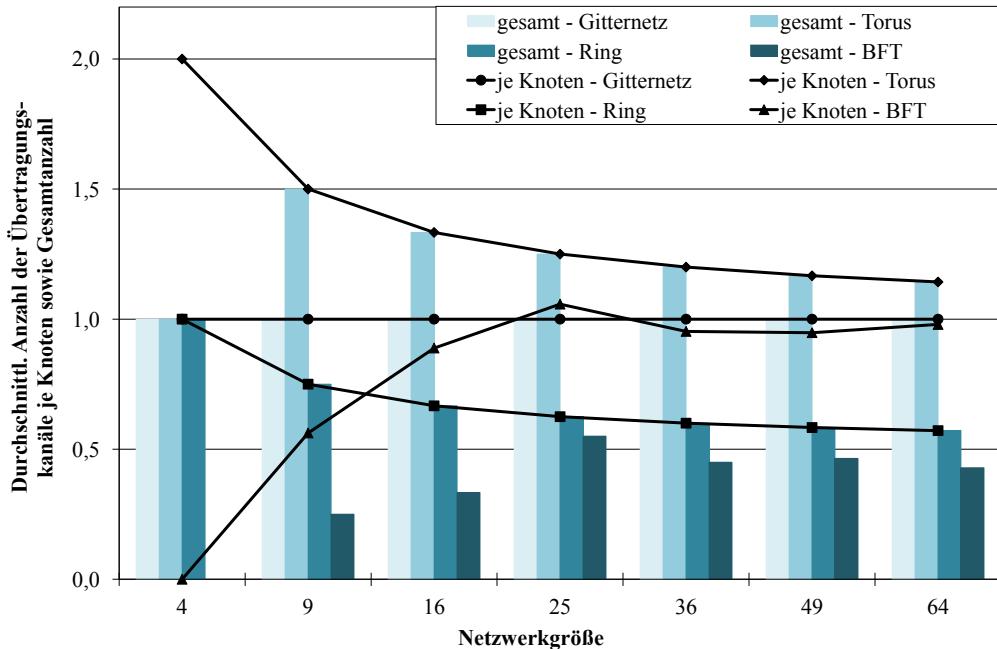

| 2.15 | Grad der Vernetzung: durchschnittliche Anzahl der Übertragungskanäle je Knoten und Gesamtanzahl der Übertragungskanäle . . . . . | 41 |

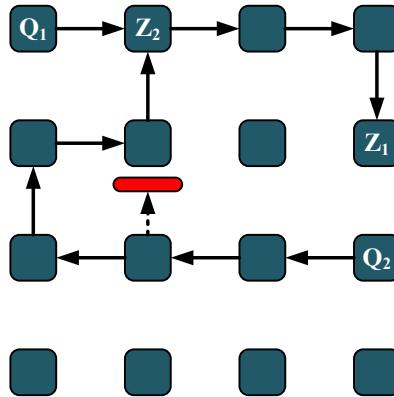

| 2.16 | Beispiel für XY-Routing und West-First-Routing . . . . .                                                                         | 44 |

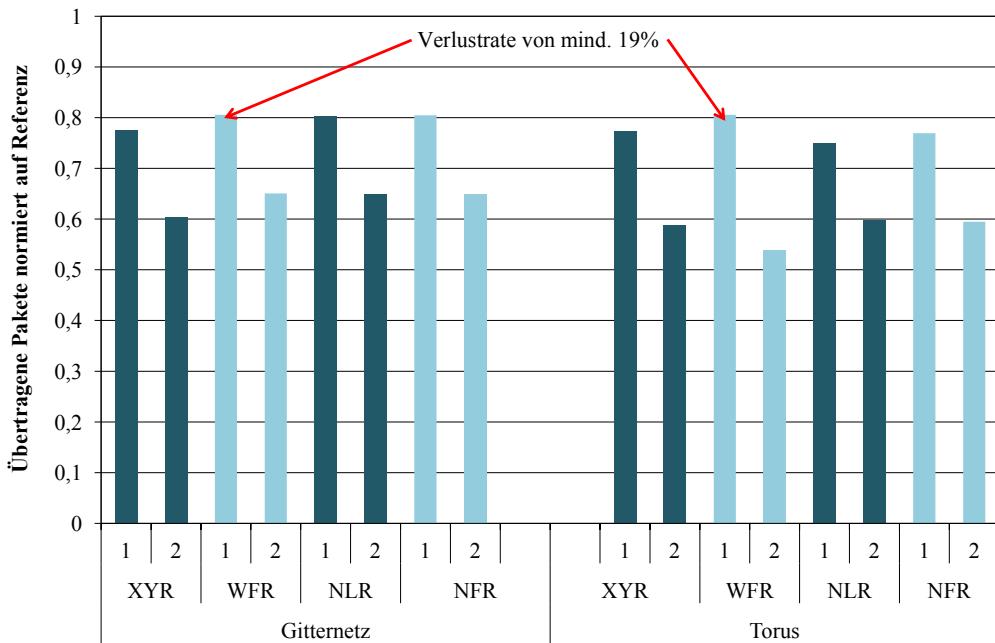

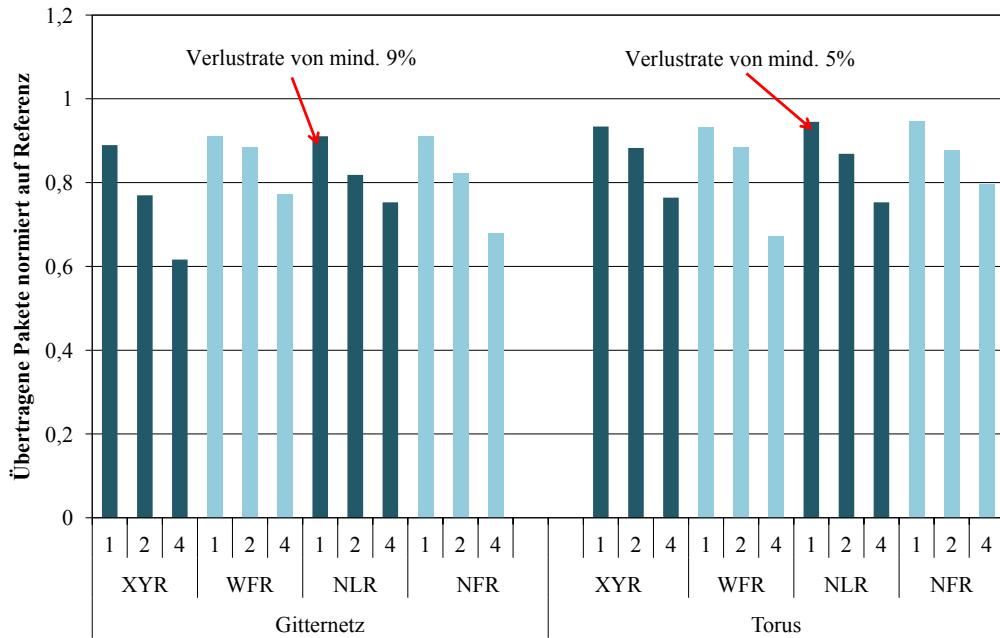

| 2.17 | Auswirkung von Router-Ausfällen auf die Zuverlässigkeit und Leistungsfähigkeit . . . . .                                         | 45 |

| 2.18 | Auswirkung des Ausfalls von Übertragungskanälen auf die Zuverlässigkeit und Leistungsfähigkeit . . . . .                         | 47 |

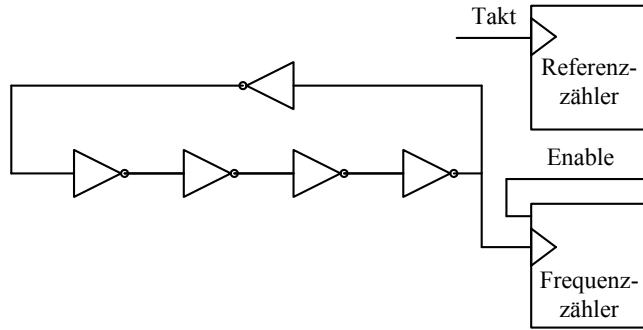

| 2.19 | Schematischer Aufbau eines Ringoszillators . . . . .                                                                             | 49 |

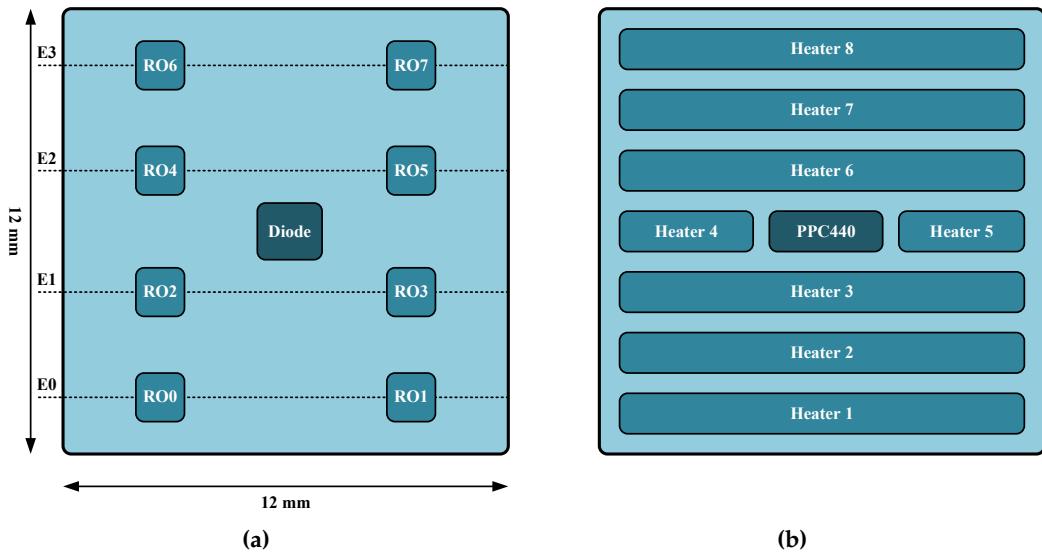

| 2.20 | Platzierung der Temperatursensoren und Test-Heater auf dem FPGA . . .                                                            | 50 |

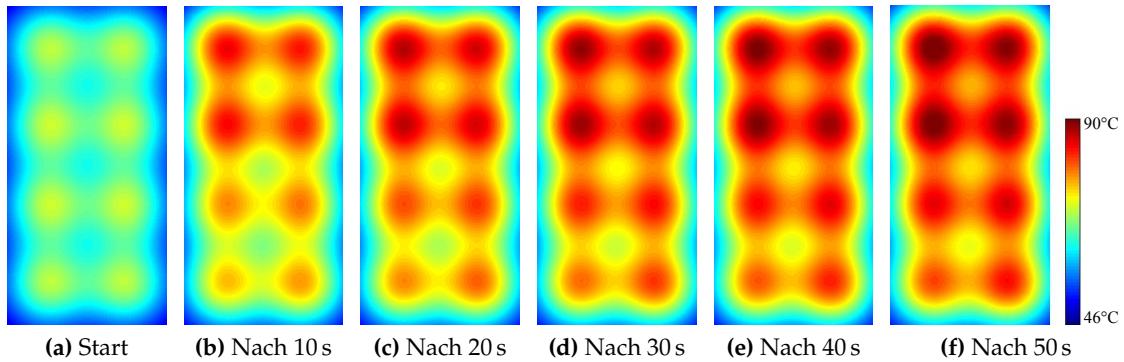

| 2.21 | Temperaturausbreitung auf dem FPGA . . . . .                                                                                     | 52 |

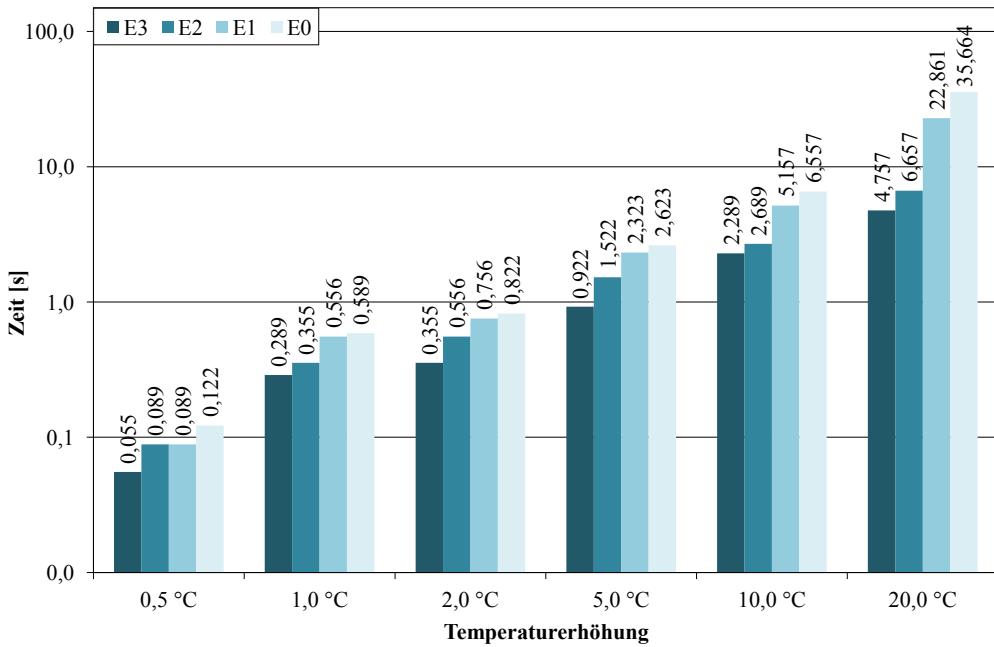

| 2.22 | Dauer der Temperaturausbreitung für verschiedene Zonen des FPGA . . .                                                            | 53 |

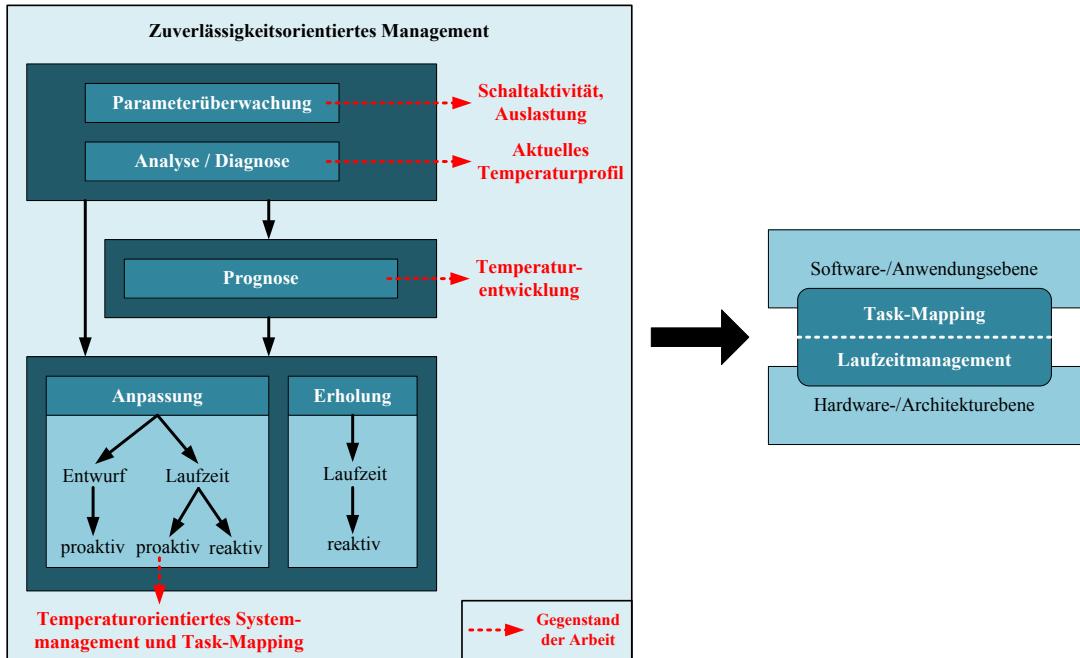

| 2.23 | Allgemeiner Aufbau und Einordnung eines mehrschichtigen, zuverlässigkeitssorientierten Systemmanagements . . . . .               | 55 |

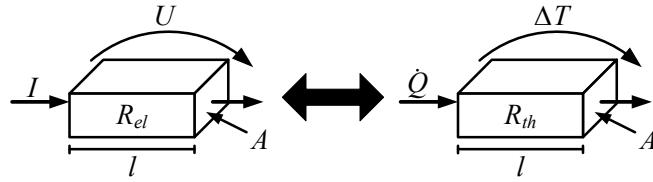

| 3.1  | Äquivalenz zwischen elektrischem und thermischem Widerstand . . . . .                                                            | 59 |

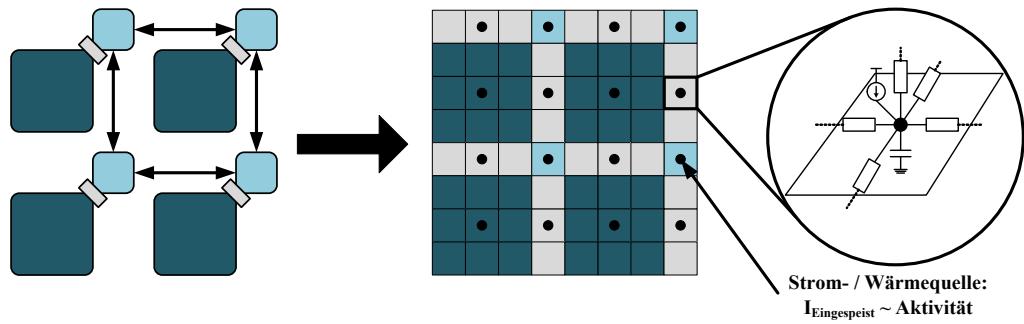

| 3.2  | Abbildung eines $2 \times 2$ NoC auf ein äquivalentes RC-Netz . . . . .                                                          | 62 |

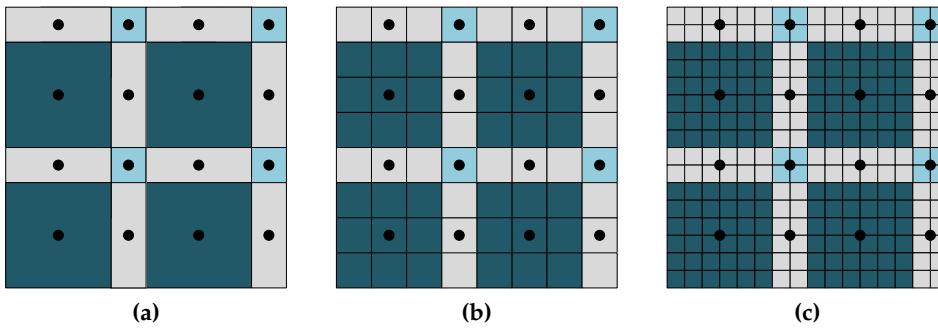

| 3.3  | Genauigkeitsstufen der Abbildung eines $2 \times 2$ NoC auf ein äquivalentes RC-Netz . . . . .                                   | 65 |

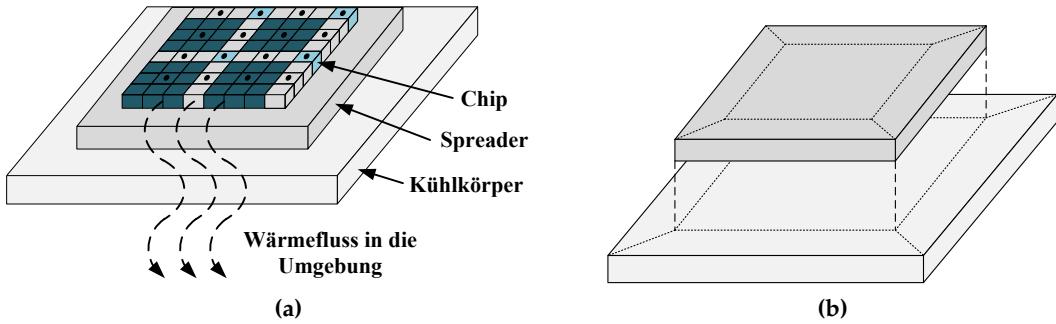

| 3.4  | Vollständig modellierter Chip . . . . .                                                                                          | 66 |

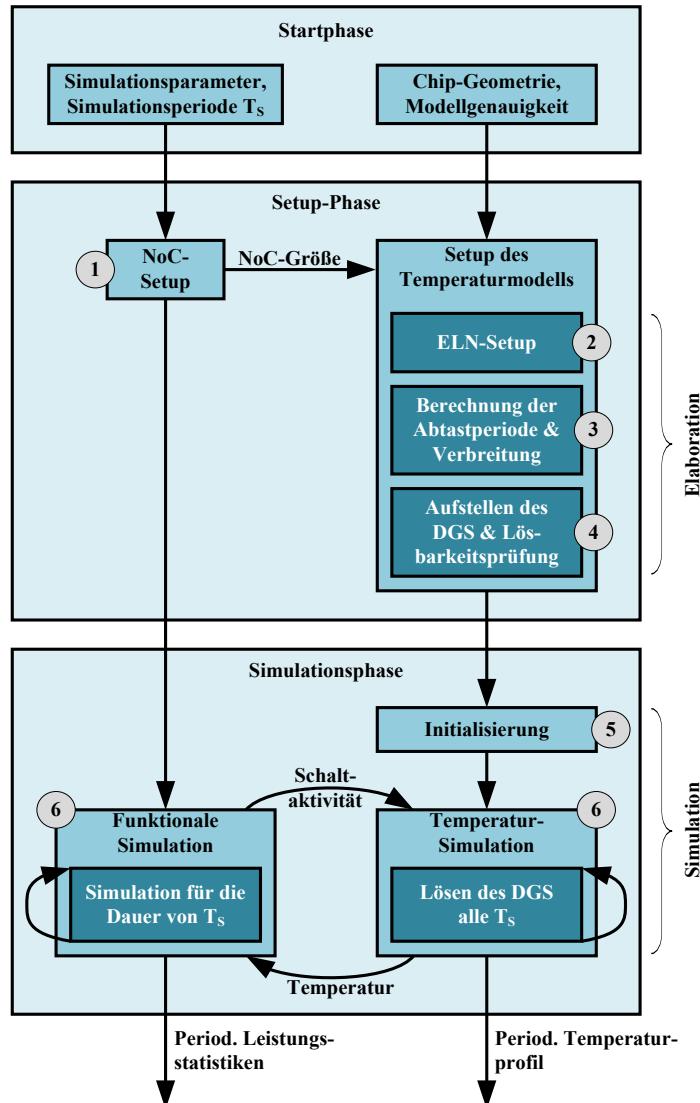

| 3.5  | Ablauf der Simulation des Temperaturverlaufs . . . . .                                                                           | 68 |

|      |                                                                                                                                                                                                                          |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

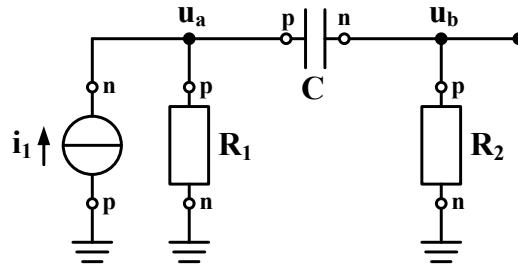

| 3.6  | Beispiel für ein mithilfe von ELN-Primitiven modellierbares elektrisches Netzwerk . . . . .                                                                                                                              | 69  |

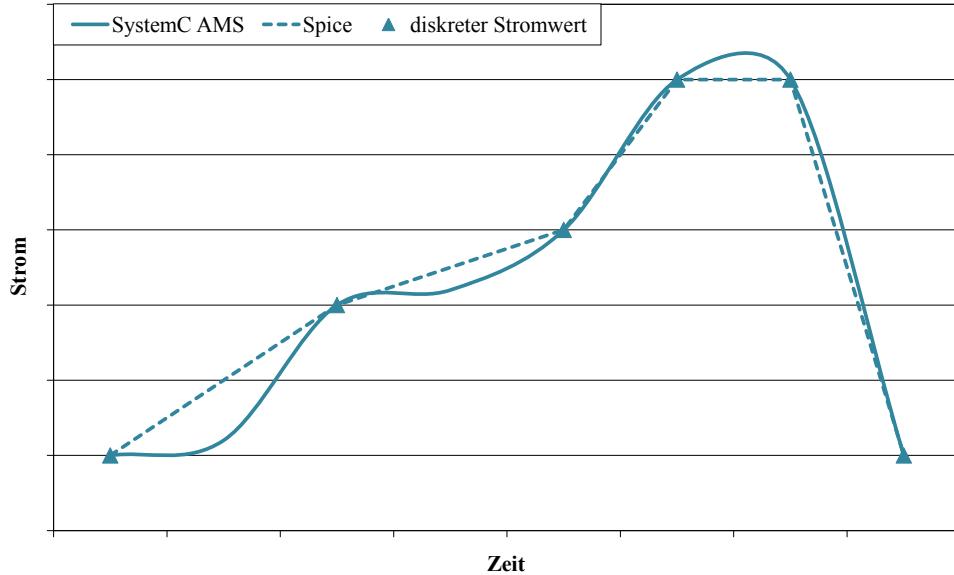

| 3.7  | Modellierung einer Stromquelle mit SPICE und SystemC AMS . . . . .                                                                                                                                                       | 72  |

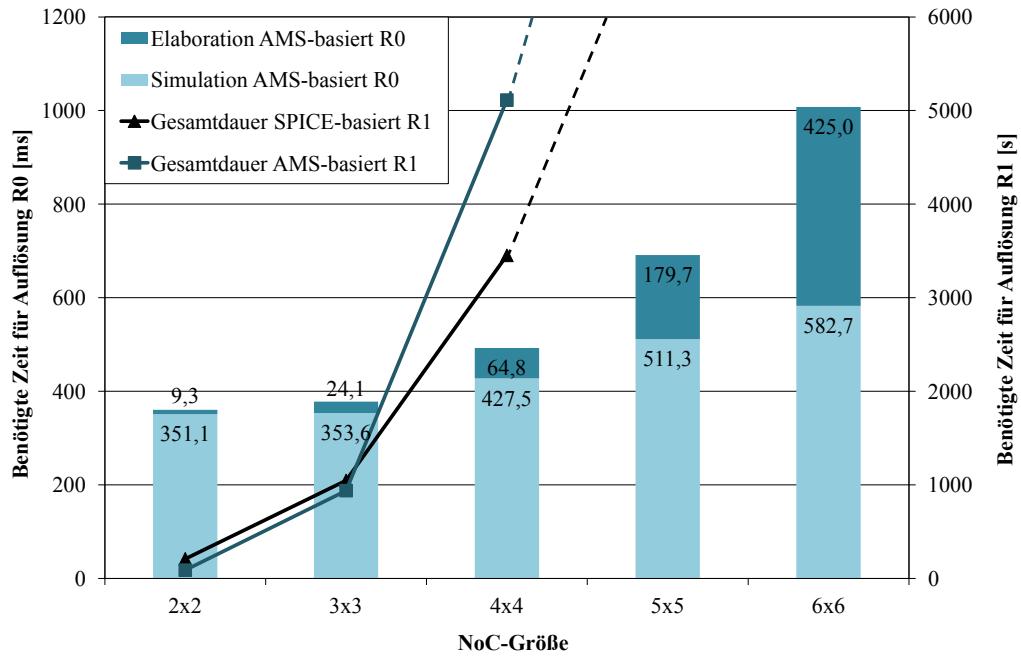

| 3.8  | Zeitaufwand der Temperatursimulation in Abhängigkeit von der NoC-Größe . . . . .                                                                                                                                         | 76  |

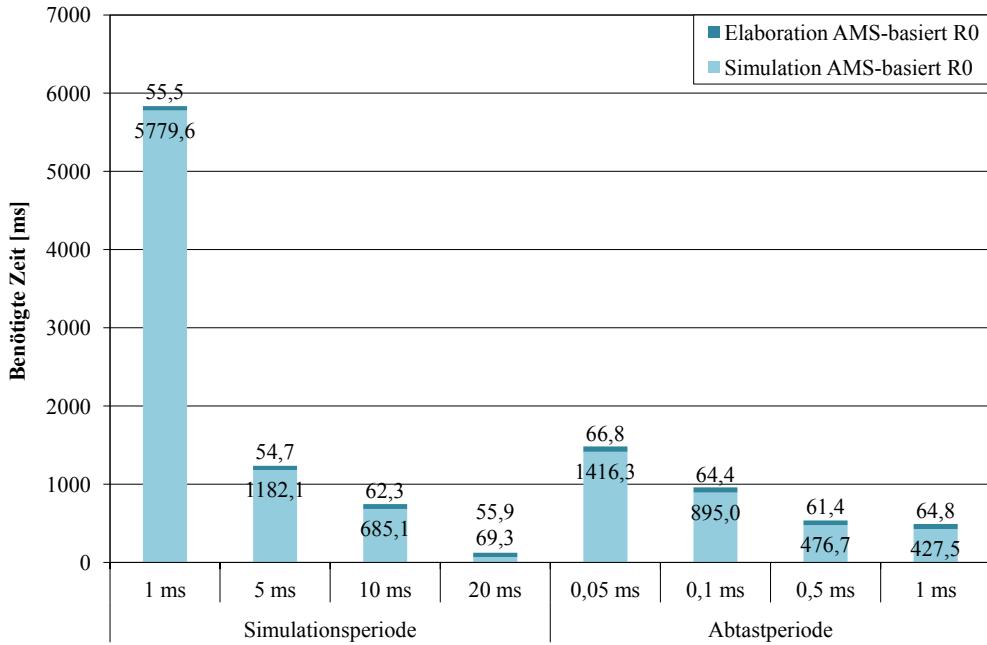

| 3.9  | Zeitaufwand der Temperatursimulation in Abhängigkeit von $T_S$ und $T_A$ . . . . .                                                                                                                                       | 77  |

| 3.10 | Ermittelte durchschnittliche Temperatur im System . . . . .                                                                                                                                                              | 79  |

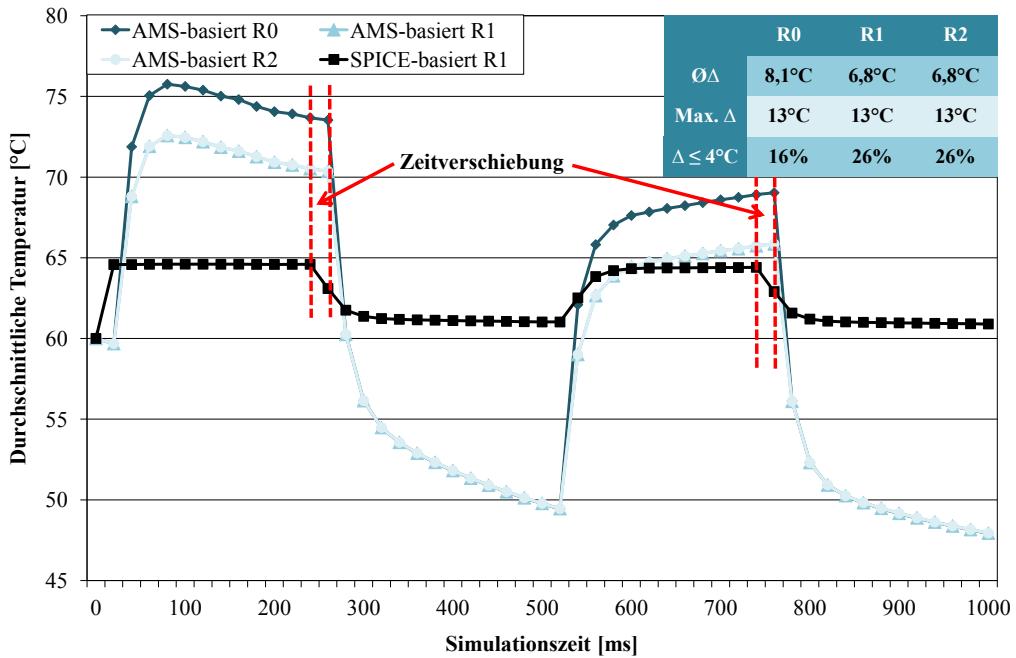

| 3.11 | Modellierung des Temperaturprofils eines $2 \times 2$ NoC . . . . .                                                                                                                                                      | 80  |

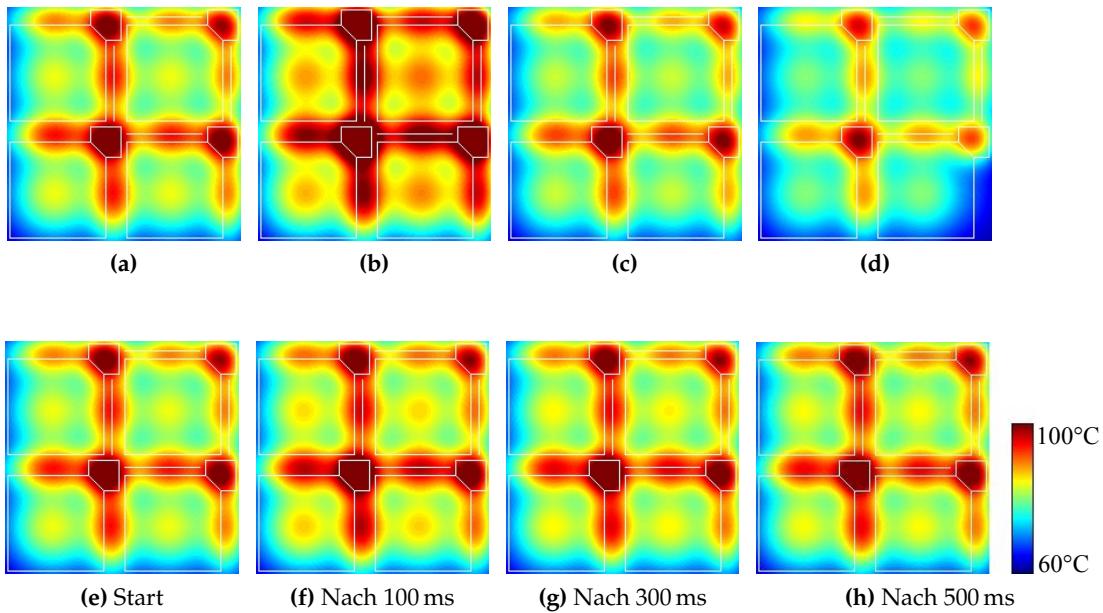

| 3.12 | Ermittelte Temperatur eines einzelnen Routers unter Verwendung verschiedener Auflösungen . . . . .                                                                                                                       | 81  |

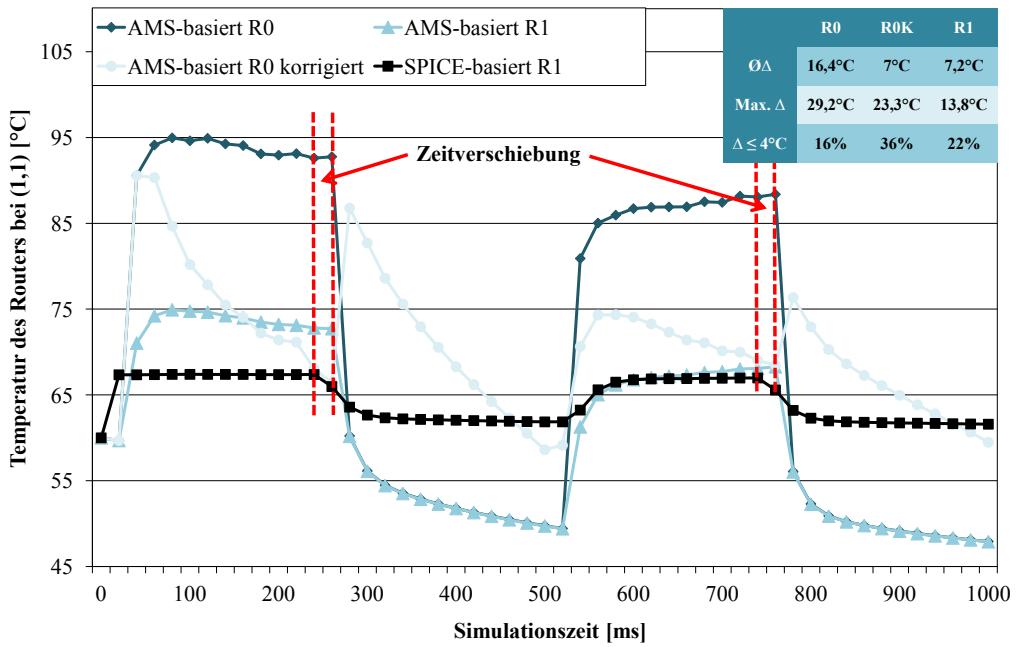

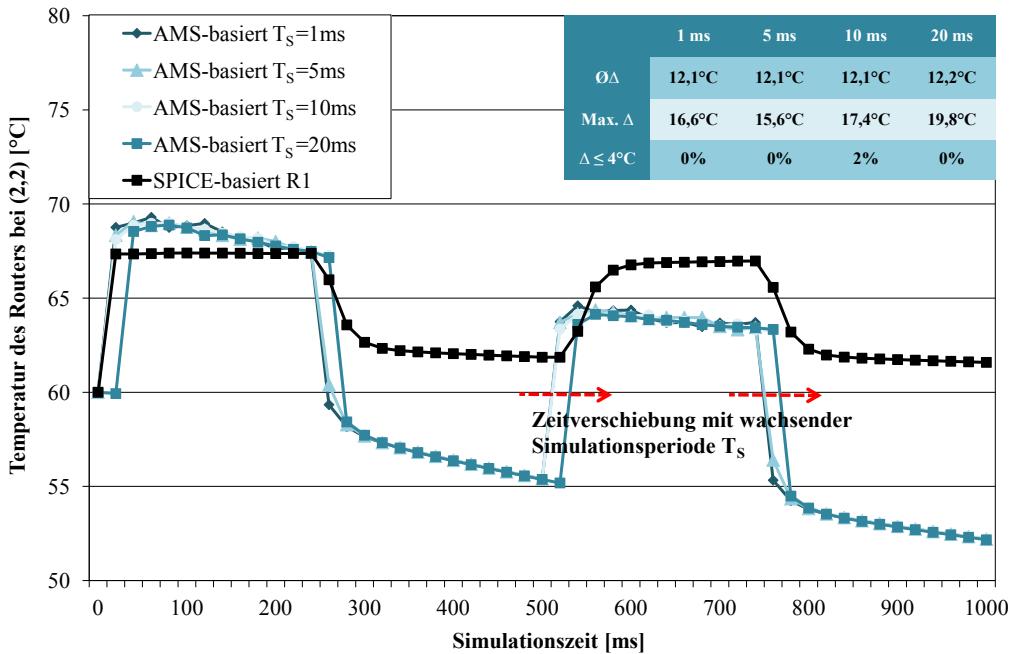

| 3.13 | Ermittelte Temperatur eines einzelnen Routers unter Verwendung verschiedener Simulationsperioden . . . . .                                                                                                               | 83  |

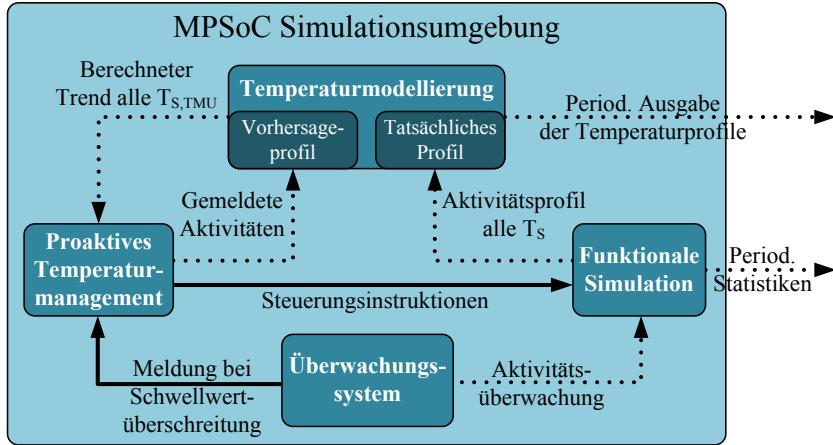

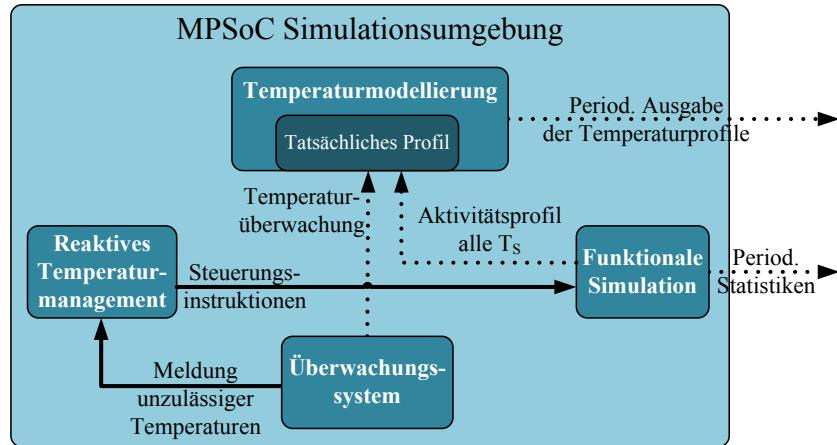

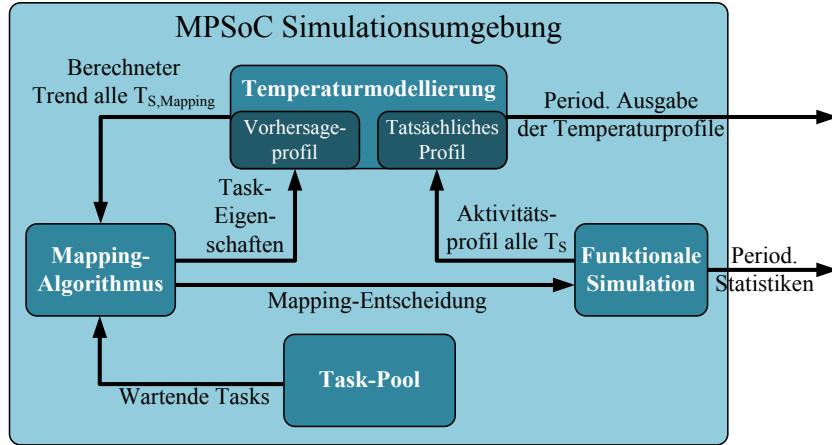

| 4.1  | Schema der Umgebung zur Simulation des proaktiven Temperaturmanagements NoC-basierter Mehrkernprozessoren . . . . .                                                                                                      | 97  |

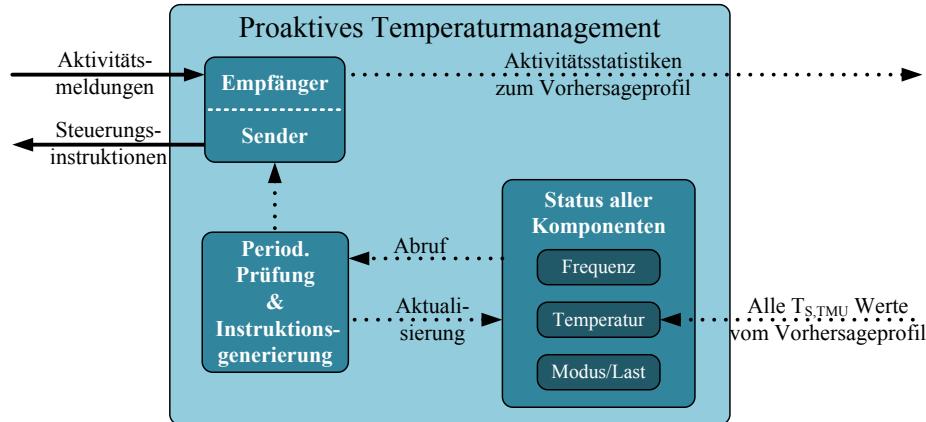

| 4.2  | Interne Funktionsweise des proaktiven Temperaturmanagements . . . . .                                                                                                                                                    | 98  |

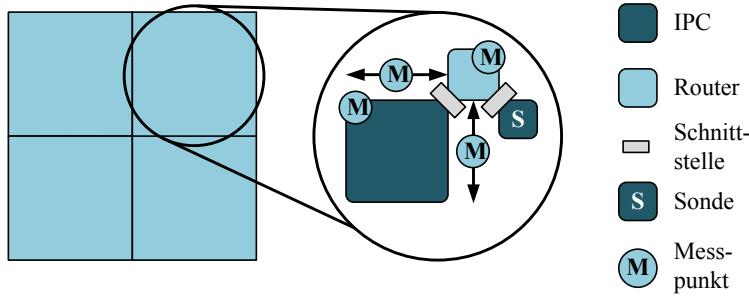

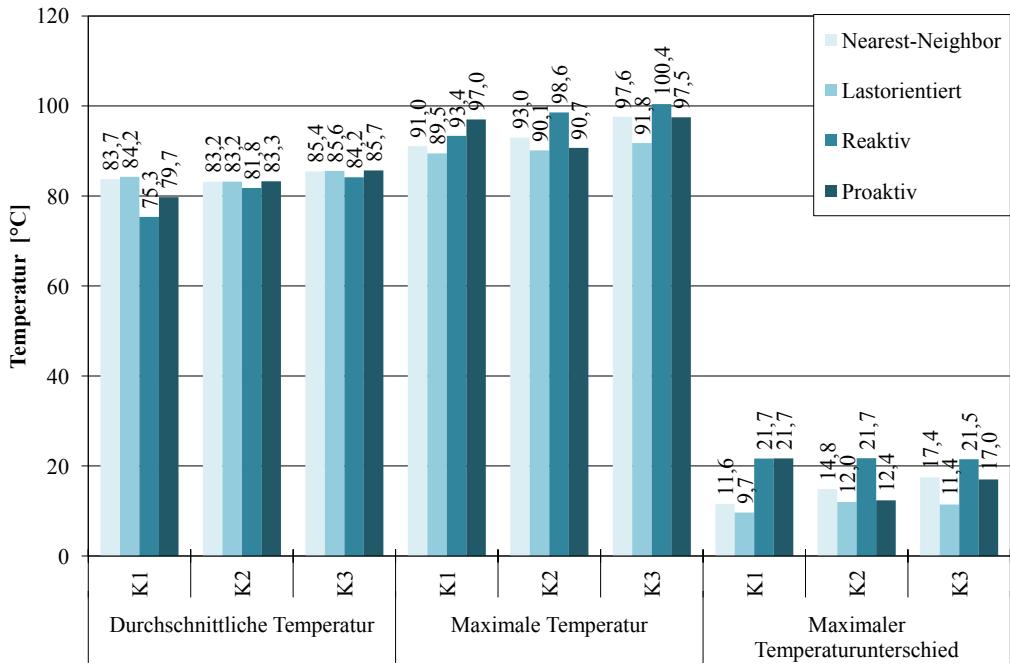

| 4.3  | Einteilung eines $2 \times 2$ NoC in Zuständigkeitsbereiche einzelner Sonden . .                                                                                                                                         | 100 |

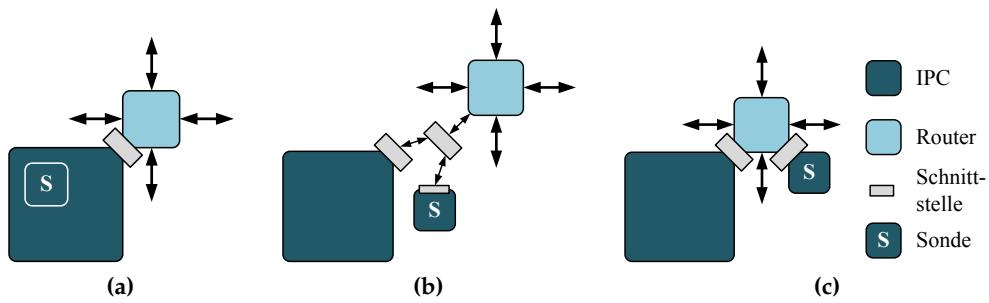

| 4.4  | Alternativen eine Sonde an das NoC anzuschließen . . . . .                                                                                                                                                               | 102 |

| 4.5  | Schema der Umgebung zur Simulation des reaktiven Temperaturmanagements NoC-basierter Mehrkernprozessoren . . . . .                                                                                                       | 104 |

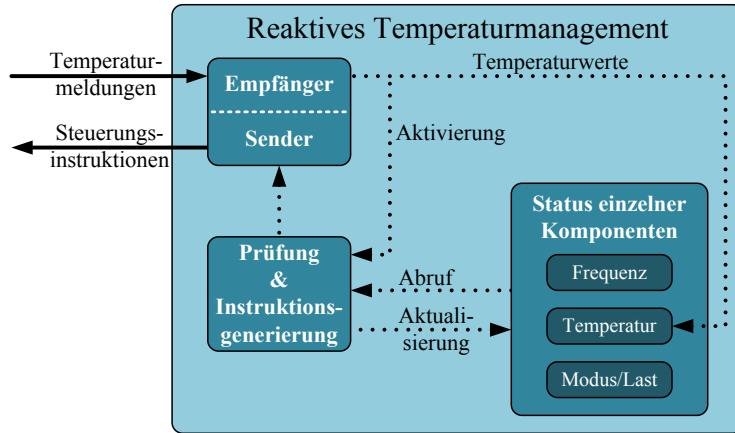

| 4.6  | Interne Funktionsweise des reaktiven Temperaturmanagements . . . . .                                                                                                                                                     | 105 |

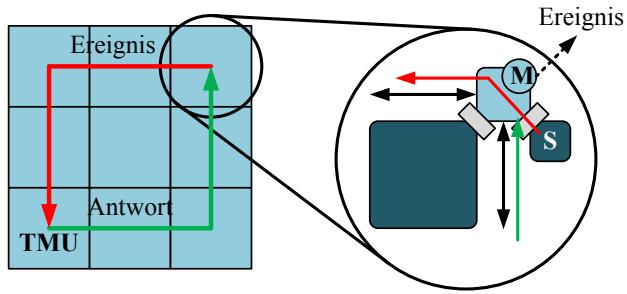

| 4.7  | Exemplarische Kommunikation zwischen Sonde und TMU . . . . .                                                                                                                                                             | 106 |

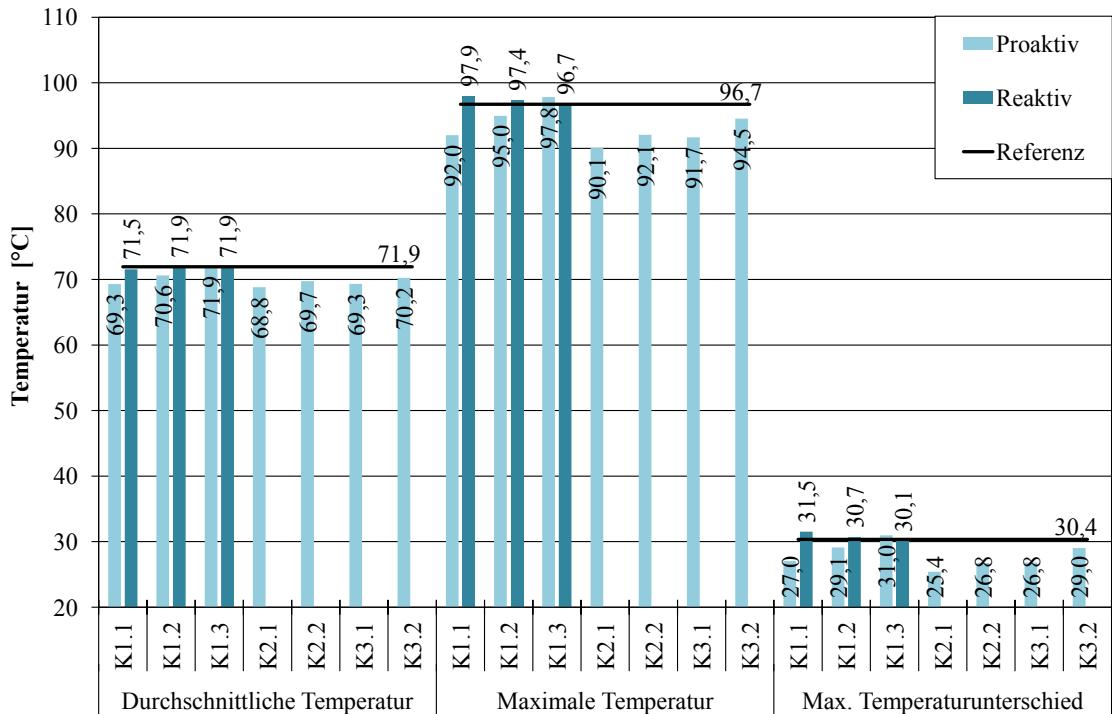

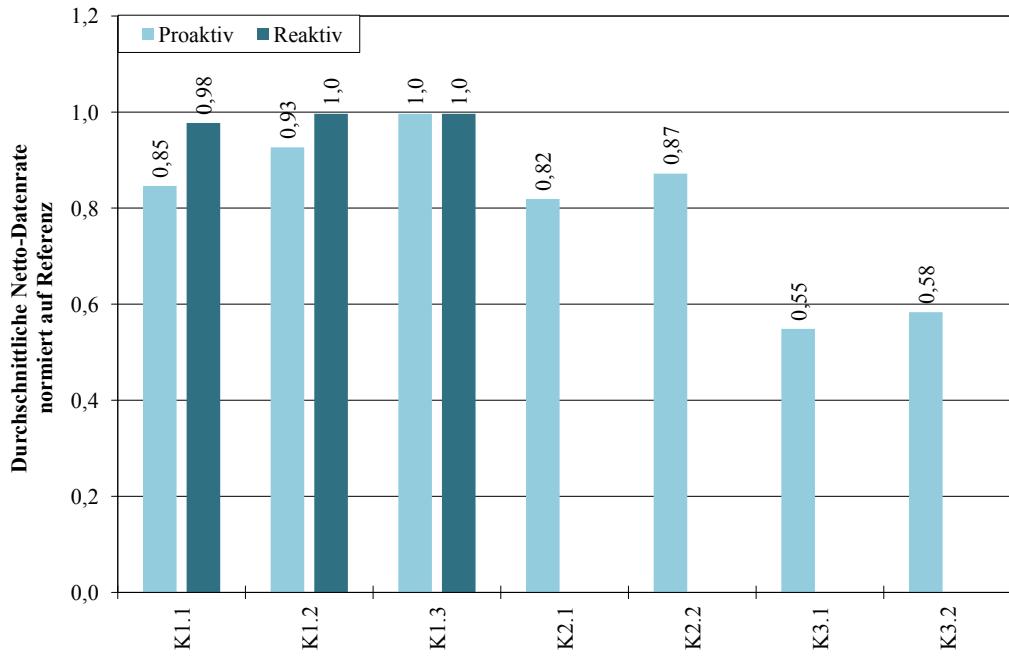

| 4.8  | Ergebnisse für das proaktive sowie das reaktive Temperaturmanagement bezüglich der Durchschnittstemperatur, der Maximaltemperatur und der maximalen Temperaturunterschiede in einem $4 \times 4$ NoC . . . . .           | 111 |

| 4.9  | Verlauf der Maximaltemperatur in einem $4 \times 4$ NoC über die Dauer einer Sekunde . . . . .                                                                                                                           | 112 |

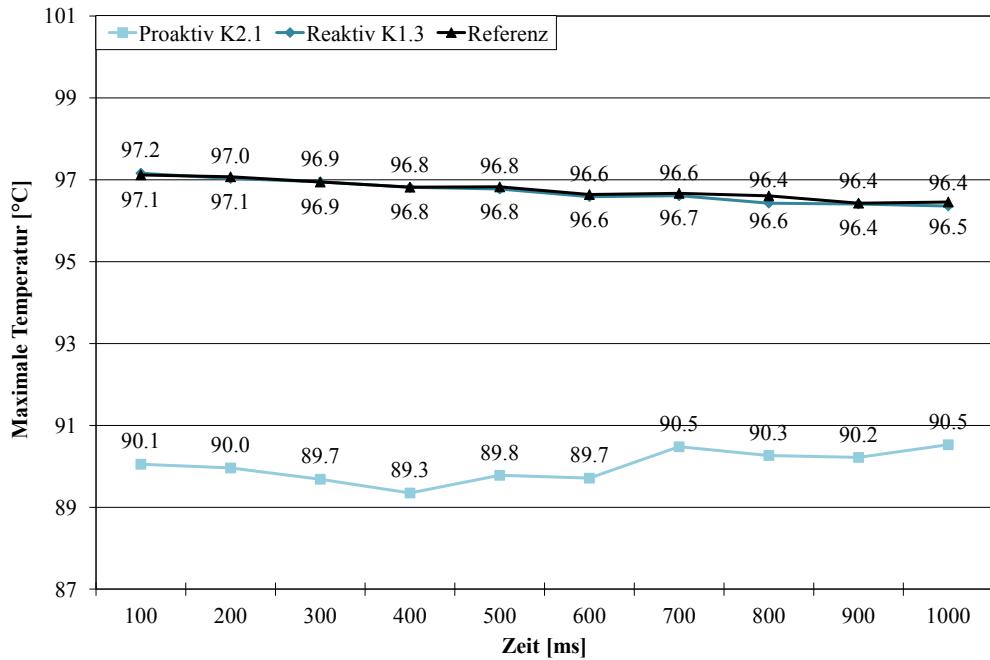

| 4.10 | Durchschnittswerte für die Dauer einer Paketübertragung und die Verzögerung der Weiterleitung eines Flits durch einen Router in einem $4 \times 4$ NoC für das proaktive und das reaktive Temperaturmanagement . . . . . | 114 |

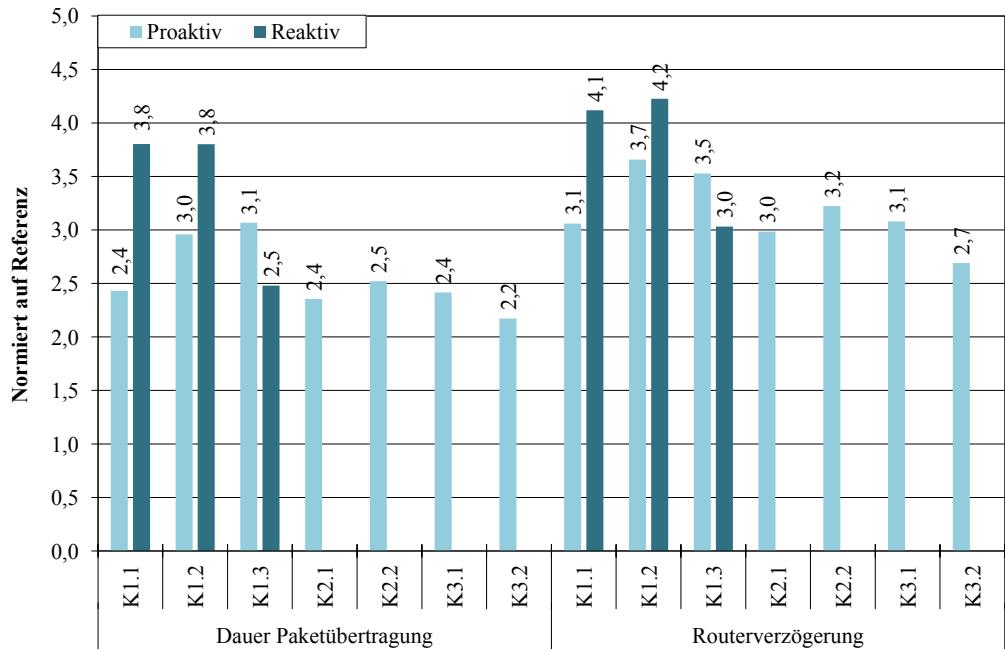

| 4.11 | Durchschnittliche Dauer der durch DFS reduzierten Taktfrequenz der IPCs und Router in einem $4 \times 4$ NoC für das proaktive und das reaktive Temperaturmanagement . . . . .                                           | 116 |

| 4.12 | Durchschnittliche Netto-Datenrate in einem $4 \times 4$ NoC für das proaktive und das reaktive Temperaturmanagement . . . . .                                                                                            | 118 |

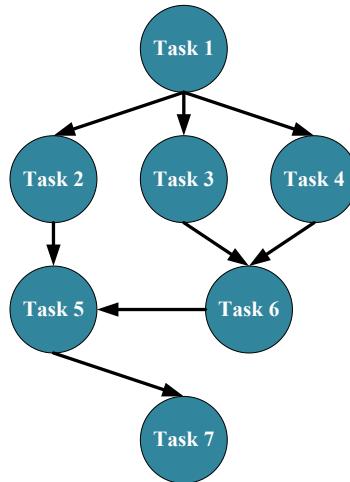

| 4.13 | Anwendungsmodellierung durch einen Task-Graphen . . . . .                                                                                                                                                                | 125 |

| 4.14 | Umgebung zur Simulation des proaktiven Task-Mappings NoC-basierter Mehrkernprozessoren . . . . .                                                                                                                         | 127 |

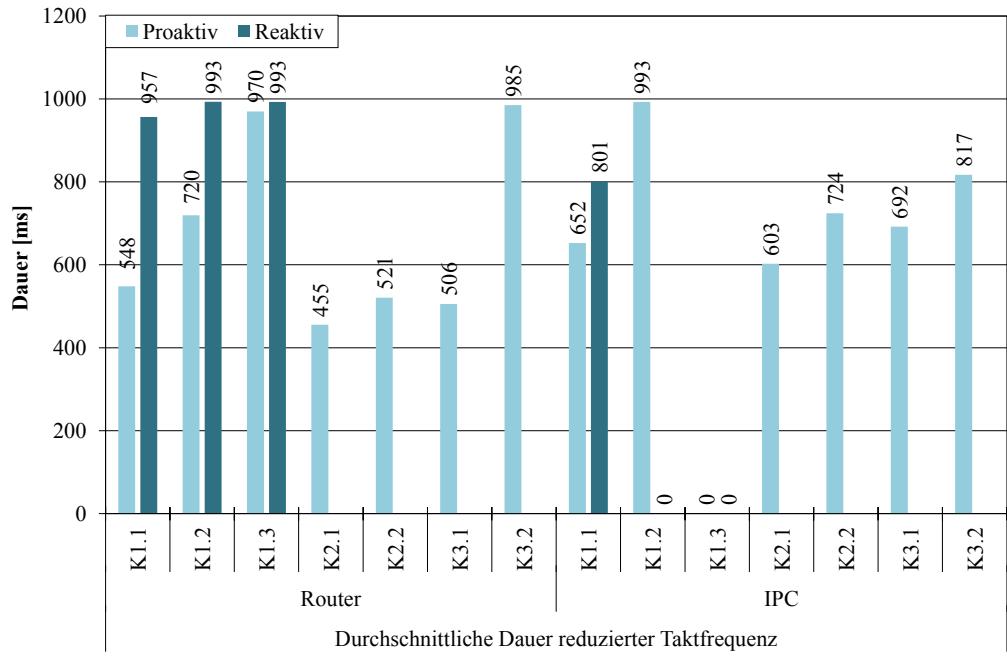

| 4.15 | Ergebnisse bezüglich der Durchschnittstemperatur, der Maximaltemperatur und der maximalen Temperaturunterschiede in einem $4 \times 4$ NoC . . . . .                                                                     | 131 |

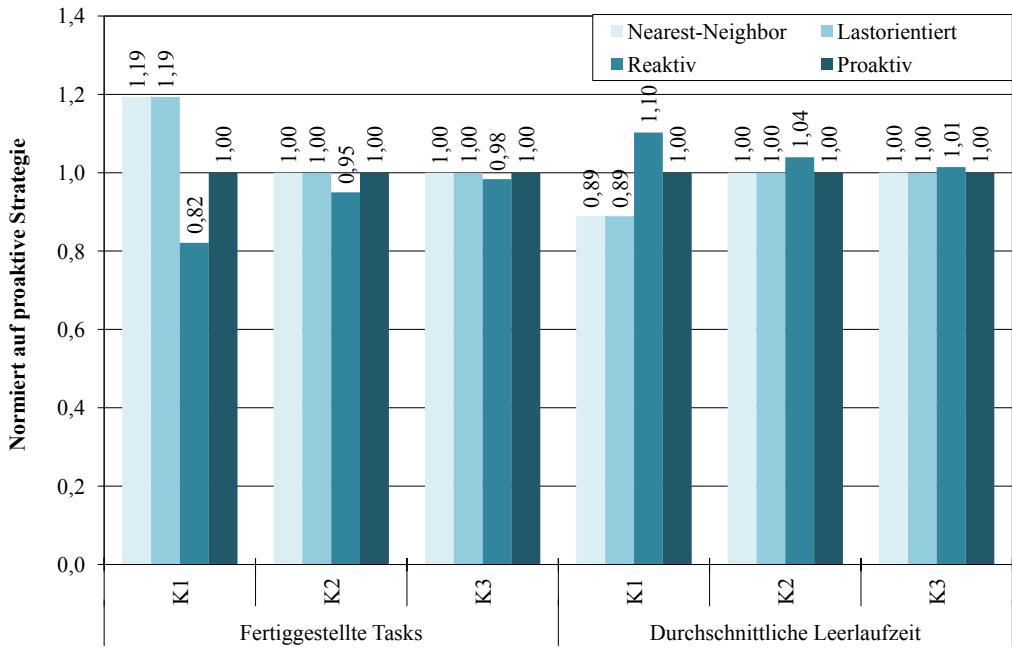

| 4.16 | Anzahl fertiggestellter Tasks und durchschnittliche Leerlaufdauer der Systemkomponenten in einem $4 \times 4$ NoC . . . . .                                                                                              | 133 |

# Tabellenverzeichnis

|     |                                                                                                                                                                                     |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Qualitative Bewertung und Vergleich Punkt-zu-Punkt-basierter, busbasierter und NoC-basierter Kommunikationsarchitekturen . . . . .                                                  | 30  |

| 2.2 | Parameter für die Simulation der Auswirkung von Ausfällen auf gitternetz- und torusbasierte NoCs . . . . .                                                                          | 43  |

| 2.3 | Genauigkeit der ringoszillatortbasierten Temperatursensoren . . . . .                                                                                                               | 51  |

| 3.1 | Dualismus zwischen dem Fluss elektrischer und thermischer Energie . . .                                                                                                             | 58  |

| 3.2 | Energieaufnahme je Bitübergang sowie statische Leistungsaufnahme für einzelne Router-Komponenten, den IPC und den Übertragungskanal . . .                                           | 64  |

| 3.3 | Simulationsparameter für die Verifikation des Temperaturmodells NoC-basierter Systeme . . . . .                                                                                     | 71  |

| 3.4 | Zeitaufwand für die Temperatursimulation eines $2 \times 2$ NoC . . . . .                                                                                                           | 75  |

| 3.5 | Abweichung der durchschnittlichen Temperatur des Systems vom SPICE-Referenzmodell für verschiedene Simulationsperioden . . . . .                                                    | 82  |

| 3.6 | Qualitative Bewertung des implementierten Temperaturmodells . . . . .                                                                                                               | 86  |

| 4.1 | Qualitative Bewertung der Anbindungsalternativen einer Sonde . . . . .                                                                                                              | 103 |

| 4.2 | Parameterkonfigurationen des proaktiven und reaktiven Temperaturmanagements . . . . .                                                                                               | 109 |

| 4.3 | Ergebnisse für die Anzahl der Überwachungsnachrichten sowie der Steuerungsinstruktionen für das proaktive und das reaktive Temperaturmanagement in einem $4 \times 4$ NoC . . . . . | 121 |

| 4.4 | Durchschnittliche Temperatur in NoCs verschiedener Größe unter Verwendung der Standardkonfiguration K1.1 . . . . .                                                                  | 122 |

| 4.5 | Qualitative Bewertung des proaktiven Temperaturmanagements . . . . .                                                                                                                | 123 |

| 4.6 | Qualitative Bewertung des proaktiven Task-Mappings . . . . .                                                                                                                        | 135 |

| 5.1 | Abschätzung der Auswirkung einer Kombination der proaktiven Konzepte für Temperaturmanagement und Task-Mapping . . . . .                                                            | 142 |

# Abkürzungsverzeichnis

|        |                                                     |

|--------|-----------------------------------------------------|

| AMS    | Analog Mixed Signal                                 |

| AP     | Application Processor                               |

| ARQ    | Automatic Repeat Request                            |

| BE     | Best Effort                                         |

| BFT    | Butterfly Fat Tree                                  |

| BIST   | Built In Self Test                                  |

| CAD    | Computer-Aided Design                               |

| CLB    | Configurable Logic Block                            |

| CMOS   | Complementary Metal Oxide Semiconductor             |

| CRC    | Cyclic Redundancy Check                             |

| DFS    | Dynamic Frequency Scaling                           |

| DGS    | Differentialgleichungssystem                        |

| DPG    | Design-Productivity-Gap                             |

| DVS    | Dynamic Voltage Scaling                             |

| E/A    | Ein-/Ausgabe                                        |

| EDP    | Energy-Delay-Product                                |

| ELN    | Electrical Linear Network                           |

| EM     | Elektromigration                                    |

| FET    | Field Effect Transistor                             |

| FIFO   | First In First Out                                  |

| Flit   | Flow Control Unit                                   |

| FPGA   | Field Programmable Gate Array                       |

| GPP    | General Purpose Processor                           |

| GPU    | Graphics Processing Unit                            |

| GS     | Guaranteed Service                                  |

| HCI    | Hot Carrier Injection                               |

| IPC    | Intellectual Property Core                          |

| ITRS   | International Technology Roadmap for Semiconductors |

| LUT    | Lookup Table                                        |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor   |

|        |                                                     |

|--------|-----------------------------------------------------|

| MPSoC  | Multi-Processor-System-on-Chip                      |

| MTTF   | Mean Time To Failure                                |

| MuGFET | Multiple Gate Field Effect Transistor               |

| NBTI   | Negative Bias Temperature Instability               |

| NFR    | Negative-First-Routing                              |

| NLR    | North-Last-Routing                                  |

| NoC    | Network-on-Chip                                     |

| PDP    | Power-Delay-Product                                 |

| Phit   | Physical Transfer Unit                              |

| PWL    | Piecewise Linear Source                             |

| QoS    | Quality-of-Service                                  |

| RA     | Routing-Algorithmus                                 |

| RDNI   | Resource Dependent Network Interface                |

| RINI   | Resource Independent Network Interface              |

| RO     | Ringoszillator                                      |

| RTL    | Register Transfer Level                             |

| SAFS   | Store-And-Forward Switching                         |

| SNR    | Signal-to-Noise Ratio                               |

| SoC    | System-on-Chip                                      |

| SoI    | Silicon-on-Insulator                                |

| SPICE  | Simulation Program with Integrated Circuit Emphasis |

| TDDB   | Time Dependent Dielectric Breakdown                 |

| TDP    | Thermal Design Power                                |

| TG     | Task-Graph                                          |

| TGFF   | Task Graphs For Free                                |

| TLM    | Transaction Level Modeling                          |

| TMR    | Triple Modular Redundancy                           |

| TMU    | Thermal Management Unit                             |

| TTF    | Time To Failure                                     |

| VCTS   | Virtual-Cut-Through Switching                       |

| WFR    | West-First-Routing                                  |

| WHS    | Wormhole Switching                                  |

| XYR    | XY-Routing                                          |

---

# 1 Einleitung

Die fortschreitende Miniaturisierung hochintegrierter Schaltkreise und die Einführung von Fertigungstechnologien mit Strukturgrößen weit im Submikrometerbereich haben neben einer Erhöhung der Anzahl integrierbarer Transistoren bei gleichbleibender Fläche, und damit einer Erhöhung der Leistungsfähigkeit moderner Mikrochips, auch negative Effekte. So stößt man zunehmend an die Grenzen des technisch Machbaren und wird mit wachsenden Problemen wie stark zunehmenden Leckströmen und steigenden Leistungsdichten konfrontiert.

**Zielstellung** Die Entwicklung moderner Fertigungstechnologien in der Halbleitertechnik bis in den Bereich weniger Nanometer korrespondiert mit dem hinlänglich bekannten Moore'schen Gesetz, welches von Gordon E. Moore 1965 postuliert wurde [Moo65]. Auch für die nähere Zukunft prognostiziert die International Technology Roadmap for Semiconductors (ITRS) in ihrem Bericht für 2012 in den nächsten 10 bis 12 Jahren eine weitere Verkleinerung der Strukturgrößen bis unterhalb der Grenze von 10 nm [ITR12]. Dies soll, trotz der sich immer schwieriger gestaltenden physikalischen Bedingungen, durch den Einsatz neuer Materialien und Strukturen erreicht werden. In den kommenden Jahren werden vorwiegend Modifikationen klassischer CMOS-Strukturen genutzt, welche sich beispielsweise der Effekte von Materialien mit erhöhter Durchlässigkeit für elektrische Felder (sogenannte „high-k“-Materialien) bedienen [Rob06]. Längerfristig werden die in herkömmlicher Planartechnik gefertigten CMOS-Technologien allerdings durch stark modifizierte oder vollständig neue Technologien ergänzt und letztendlich ersetzt. Beispielhaft seien hier spezielle Silicon-on-Insulator-Techniken (SoI) [SIC10] sowie Multiple Gate Field Effect Transistors (MuGFETs) [Ris05] (z. B. Tri-Gate-FETs oder FinFETs) angeführt. Trotz des Einsatzes solch neuartiger Verfahrens- und Herstellungstechniken, und der damit verbundenen Reduzierung von Verlustleistung und Leckströmen, ist eine zunehmende Anfälligkeit hochintegrierter Schaltungen gegenüber Umwelteinflüssen sowie Alterungs- und Verschleißerscheinungen zu erwarten.

Des Weiteren führt die nur begrenzt steigerbare Leistungsfähigkeit einzelner Prozessoren dazu (siehe auch Pollack's Law [Bor07]), dass der benötigte Leistungszuwachs durch ein wachsendes Maß an Parallelität kompensiert werden muss. Das Resultat sind vorwiegend heterogene Multi-Processor-Systems-on-Chip (MPSoCs) sowie Manycore-Prozessoren [Til12a, Ada12a, Int12], welche derzeit bis zu 256 [Kal12] in der Regel ho-

mogene Rechenkerne auf einem einzelnen Chip vereinen und damit in der Lage sind, parallel mehrere Aufgaben abzuarbeiten. Die Kommunikation zwischen den Rechenkernen wird aufgrund verschiedener Vorzüge derartiger Konzepte durch netzwerkorientierte Architekturen wie Networks-on-Chip (NoCs) realisiert [Til12b, Ada12b, Art12, Son12]. Durch die wachsende Parallelität und steigende Komplexität wird dabei der Verwaltungs- und Koordinationsaufwand für ein System-on-Chip (SoC) stark erhöht. Dieser Effekt wird durch sogenannte „Multi-Everything“-Ansätze zusätzlich verstärkt. Diese ermöglichen zwar erst eine leistungs- oder energieoptimierte Steuerung und setzen hierfür beispielsweise multiple Versorgungsspannungen oder Betriebsfrequenzen ein. Jedoch erhöht sich durch diese Diversifizierung auch der erforderliche Aufwand.

Zusätzlich haben die mit neuen Fertigungstechnologien schrumpfenden Strukturgrößen immer filigranere und somit generell empfindlichere Strukturen zur Folge. Dies führt zudem zu einer erhöhten Packungsdichte der integrierten Transistoren und damit zu einer steigenden Dichte der thermischen Verlustleistung, da auf gleichem Raum eine zunehmende Anzahl von Komponenten Leistung verbraucht. Zwar stagniert der Wert der Verlustleistungsdichte seit Einführung der 130 nm-Fertigung, hält aber ein vergleichsweise hohes Niveau. Dies ist insofern als kritisch zu bewerten, dass somit temperaturbezogene Probleme stärker denn je an Bedeutung gewinnen. Neben thermischem Stress durch Temperaturspitzen und -gefälle existieren einige temperaturabhängige physikalische Effekte, welche durch hohe Temperaturen begünstigt werden. Zu diesen Effekten zählen beispielsweise Time Dependent Dielectric Breakdown (TDDB), Negative Bias Temperature Instability (NBTI) oder Elektromigration (EM), welche maßgeblich zu einer beschleunigten Alterung hochintegrierter Schaltkreise beitragen.

Aus den vorangegangenen Überlegungen ergeben sich Motivation und Zielstellung der vorliegenden Arbeit. Deren Hauptaugenmerk liegt auf der Abschwächung beziehungsweise der Verzögerung von Alterungs- und Verschleißerscheinungen. Aufgrund des zunehmenden Einflusses thermischer Effekte wird insbesondere untersucht, inwiefern das frühzeitige Erkennen von Temperaturveränderungen und Temperaturtrends zu einer Vorbeugung von Temperaturspitzen und zu einer langfristigen Reduzierung thermischen Stresses beitragen kann. Diese Arbeit konzentriert sich aufgrund der Komplexität des Feldes der On-Chip-Kommunikationsarchitekturen dabei ausschließlich auf NoC-basierte Architekturen, zumal sich diese durch eine hohe Flexibilität und eine hervorragende Skalierbarkeit als besonders vielversprechend hervorheben. Die entstehenden proaktiven Konzepte sollen neben einer Verbesserung des Temperaturprofils durch vorausschauendes Anpassen von Lastverteilung und abrufbarer Leistung möglichst auch eine Verringerung der unumgänglichen Reduzierung der Leistungsfähigkeit bewirken.

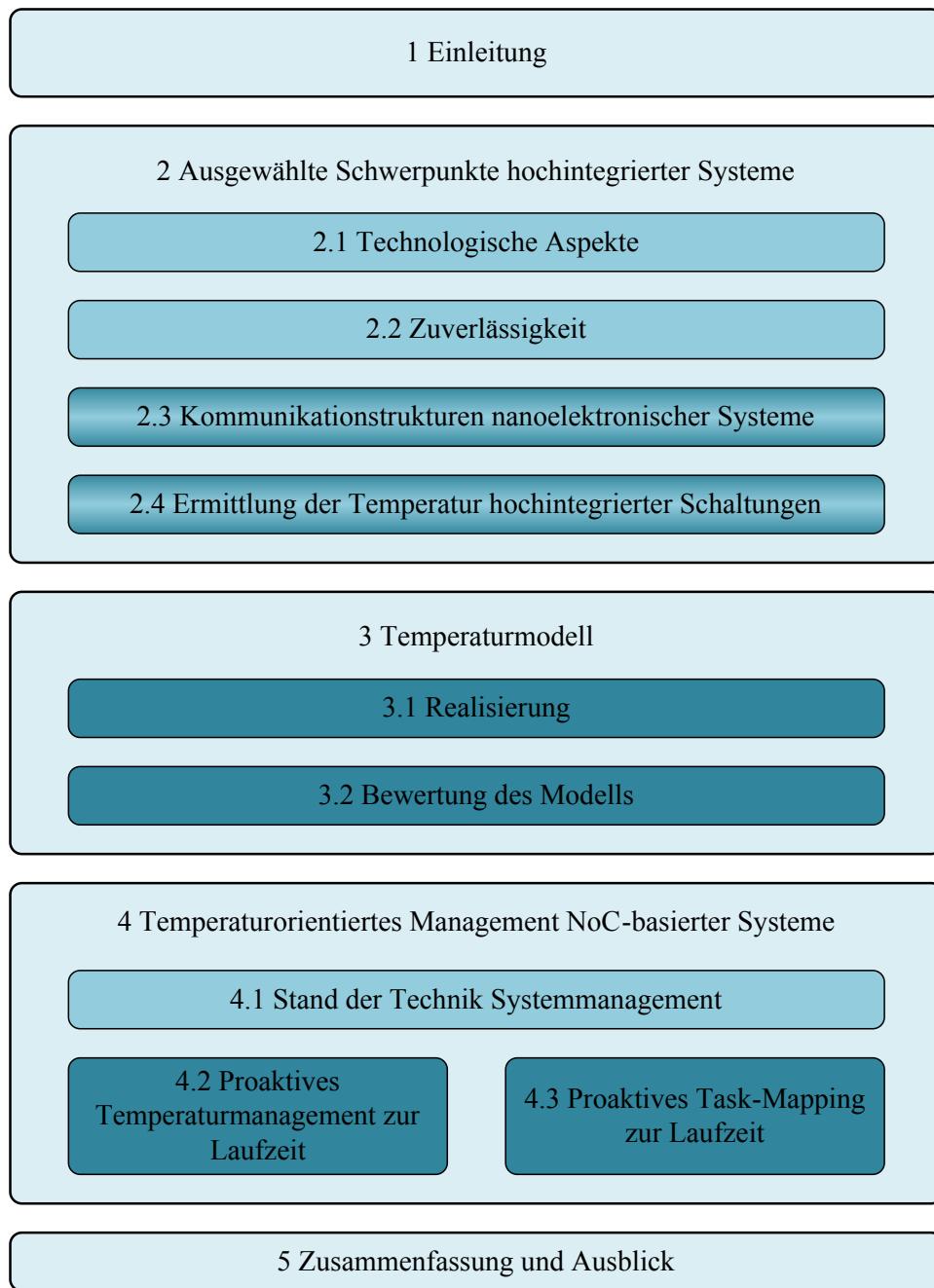

---

**Struktur der Arbeit** Die vorliegende Arbeit unterteilt sich in fünf Kapitel. Diese Struktur ist in Abbildung 1.1 dargestellt. Die dunkel hervorgehobenen Abschnitte enthalten die wesentlichen eigenen wissenschaftlichen Beiträge.

Kapitel 1 gibt eine kurze Einführung in die Thematik der Arbeit. Dabei werden aktuelle technologische Entwicklungen und Problemstellungen umrissen, welche maßgeblich zur Motivation und Zielstellung dieser Arbeit beitragen. Zusätzlich wird ein Überblick über die Struktur der Arbeit sowie darin enthaltene eigene Beiträge gegeben.

In Kapitel 2 wird eine Reihe thematischer Schwerpunkte behandelt, welche für diese Arbeit relevant sind. Dazu werden eingehende Betrachtungen zu den Bereichen technologischer Aspekte und der Architektur moderner nanoelektronischer Systeme sowie Probleme und Maßnahmen deren Zuverlässigkeit betreffend angestellt. Weiterhin werden Ansätze zur Ermittlung der Temperatur hochintegrierter Schaltungen vorgestellt, wobei eine für diese Arbeit bedeutsame Methode näher untersucht wird.

In Kapitel 3 wird ein Modell vorgestellt, mit dessen Hilfe eine akkurate und schnelle Prognose kurzfristiger Temperaturänderungen NoC-basierter Systeme zur Laufzeit getroffen werden kann. Dieses Modell wird im Hinblick auf Genauigkeit und Leistungsfähigkeit untersucht und bezüglich seiner Tauglichkeit für ein proaktives Systemmanagement bewertet.

Kapitel 4 befasst sich mit der Steuerung und Überwachung NoC-basierter Systeme. Zunächst wird ein Überblick über den Stand der Technik bezüglich gängiger Methoden für das Management nanoelektronischer Systeme gegeben. Im Anschluss wird das in Kapitel 3 vorgestellte Temperaturmodell für zwei verschiedene Ansätze einer proaktiven temperaturorientierten Systemsteuerung genutzt. Ein Vergleich mit etablierten Mechanismen ermöglicht Aussagen bezüglich des Mehrwertes und der Einsatzmöglichkeiten der vorgestellten Ansätze. Die gewonnenen Erkenntnisse und daraus resultierende Schlussfolgerungen werden abschließend zusammengefasst.

Kapitel 5 fasst die in dieser Arbeit gewonnenen Erkenntnisse nochmals zusammen, diskutiert bestehende Probleme und gibt einen Ausblick auf weitere Forschungsschwerpunkte.

Teilweise eigene

Beiträge

Eigene Beiträge

**Abbildung 1.1:** Struktur der Arbeit: Abschnitte, die eigene wissenschaftliche Beiträge enthalten, sind dunkel gekennzeichnet

---

## **2 Ausgewählte Schwerpunkte hochintegrierter Systeme**

Diese Arbeit setzt sich mit der Zuverlässigkeit nanoelektronischer Systeme auseinander und konzentriert sich dabei auf ein temperaturoptimiertes Management NoC-basierter Mehrkernprozessoren. Um die Nachvollziehbarkeit und Verständlichkeit der Arbeit zu gewährleisten, wird im Folgenden auf die notwendigen theoretischen Grundlagen eingegangen. Zu diesen zählen neben der Betrachtung allgemeiner technologischer Aspekte sowie der Hervorhebung damit verbundener kritischer Faktoren vor allem eine Einführung in die Architektur nanoelektronischer Systeme, ein Überblick über den Einfluss physikalischer Effekte auf deren Zuverlässigkeit sowie ein Abriss bezüglich der Möglichkeiten zur Ermittlung der Temperatur hochintegrierter Schaltungen.

### **2.1 Technologische Aspekte**

Aktuelle Mikroprozessoren werden mit Halbleitern gefertigt, deren kleinste fotolithografisch herstellbare Strukturgröße 22 nm beträgt. Auch zukünftig ist durch neue Fertigungstechnologien mit weiteren Reduzierungen der geometrischen Dimensionen sowie der Spannungsspegel hochintegrierter Schaltungen zu rechnen [ITR13b]. Dies führt neben einem verringerten Platzbedarf und somit der Möglichkeit, mehr Komponenten auf einem einzelnen Chip zu integrieren, sowie einer Reduzierung der Leistungsaufnahme auch zu unerwünschten Effekten.

#### **2.1.1 Entwicklung der Fertigungstechnologie**

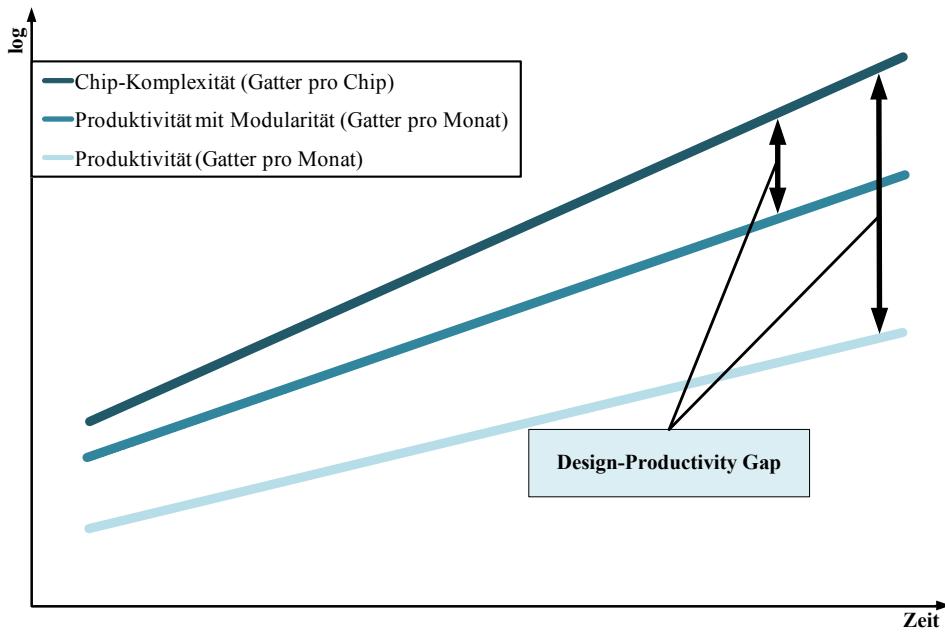

Im Bereich der mikro- und nanoelektronischen Systeme ist ein stetig steigender Bedarf an Flexibilität und Leistungsfähigkeit zu verzeichnen. Dies manifestiert sich in einer steigenden Anzahl der auf einem einzelnen Chip integrierten Systemkomponenten sowie einer zunehmenden Heterogenität dieser Komponenten [KTJR05, CLP<sup>+</sup>09]. Dieser Trend wird besonders im Sektor der mobilen Geräte deutlich, zu denen beispielsweise Smartphones, Tablets und PDAs zählen. Demgegenüber stehen steigende Anforderungen bezüglich der Zuverlässigkeit und der Energieeffizienz sowie der Time-to-Market, der Produktqualität und der Kostenminimierung [ITR12]. Nicht zuletzt durch diese gegensätz-

liche Entwicklung ist ein Paradigmenwechsel im Bereich der On-Chip-Kommunikation zu beobachten. Dieser führt dazu, dass herkömmliche, busbasierte Kommunikationsarchitekturen durch leistungsfähigere, modulare und besser skalierbare Konzepte ersetzt werden.

Die steigende Systemkomplexität erfordert einen erhöhten Planungs- und Koordinationsaufwand, um die zusätzlich verfügbare Leistung effizient nutzen und einen reibungslosen Ablauf gewährleisten zu können. Die Ursache hierfür liegt in einer höheren Anzahl parallel arbeitender und untereinander kommunizierender Komponenten. Diese weisen neben unterschiedlichen Aufgabenprofilen unter Umständen auch verschiedene Priorisierungen, zeitliche Vorgaben und weitere Rahmenbedingungen auf. Solche Komponenten (auch Rechenkern oder Ressource) lassen sich in die fünf Kategorien der Mehrzweckprozessoren (General Purpose Processors (GPP)), der anwendungsspezifischen Prozessoren (Application Processors (AP)), der Beschleunigungslogik (Acceleration Logic), der Speicherkomponenten sowie der Ein- und Ausgabe (E/A) einteilen.

Ein weiterer kritischer Faktor ist der erhöhte Regulierungsaufwand für die On-Chip-Kommunikation zwischen der wachsenden Anzahl von Komponenten. Die Heterogenität der On-Chip-Komponenten hat zudem zur Folge, dass auch der Datenverkehr selbst heterogen ist (z. B. Echtzeit- oder Streaming-Daten, CPU-Instruktionen, Steuerungsinformationen) und dementsprechend komplexere Abarbeitungsmechanismen erforderlich sind. Zusätzlich sorgen die aufgeführten Effekte dafür, dass sich eine etwaige Systemüberwachung und -steuerung aufwändiger und komplexer gestaltet. Zur Überwachung gehört beispielsweise das Erstellen von Verkehrsstatistiken oder die Analyse einzelner Pakete. Die Steuerung hingegen beinhaltet Wartung, Selbstheilung, Fehlerdetektion und -korrektur sowie die Anpassung des Systems an vorgegebene Last-, Temperatur- oder Energieprofile.

Neben diesen eher auf System- beziehungsweise Entwurfsebene gelegenen Problemfeldern existiert auch eine Reihe viel grundlegenderer teils physikalischer Faktoren. Diese gehen mit der Weiterentwicklung der Fertigungstechnologien einher und gewinnen gerade im Bereich der MPSoCs und Mehrkernprozessoren zunehmend an Bedeutung. Hierzu zählen unter anderem Aspekte wie Energieminimierung und Leistungsdichte sowie temperaturbezogene Probleme wie Temperaturspitzen und thermischer Stress.

### 2.1.2 Kritische Faktoren

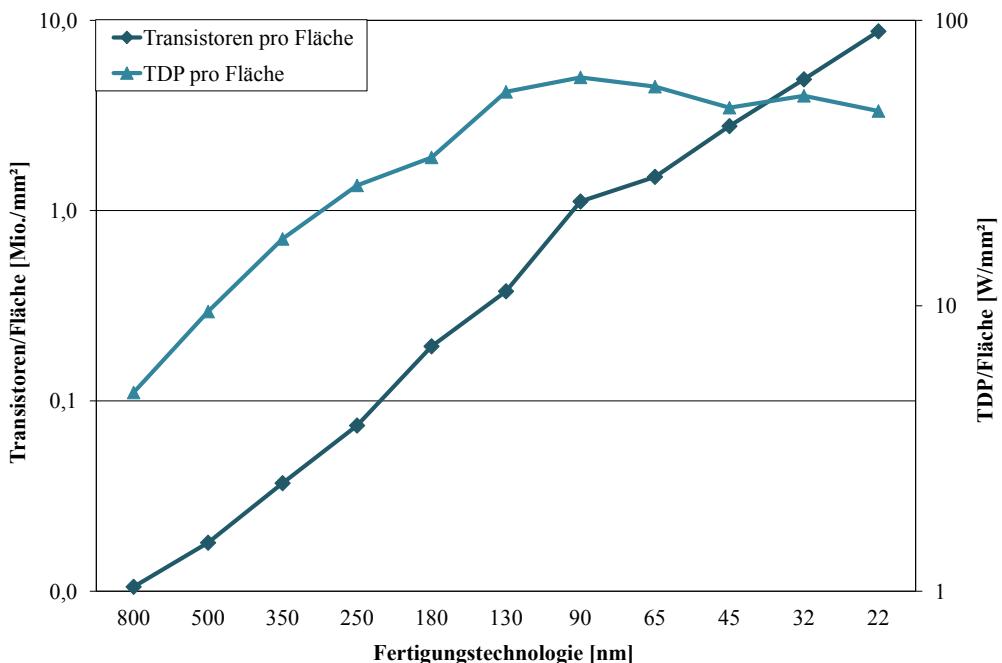

Aufgrund der immer filigraneren Halbleiterstrukturen steigt sowohl die absolute Anzahl leistungsverbrauchender Komponenten als auch deren Dichte je Flächeneinheit (siehe Abbildung 2.2), da einzelne Elemente kompakter ausgelegt werden können. Dies hat einerseits zur Folge, dass die Anfälligkeit der nanoelektronischen Bauteile gegenüber Umwelteinflüssen und Alterungserscheinungen steigt, wodurch sich die effektive Le-

bensdauer einer Schaltung potentiell verringert. Zudem erhöht sich durch die steigende Anzahl von Transistoren die Wahrscheinlichkeit eines Defekts und eines entsprechenden Ausfalls. Andererseits ermöglichen kleinere Fertigungsstrukturen eine Reduzierung der Gesamtleistungsaufnahme hochintegrierter Schaltungen. Diese Reduzierung ist angesichts einer steigenden Anzahl zu versorgender Elemente erforderlich, um den Energiebedarf digitaler Schaltungen zu begrenzen. Dabei wird ausgenutzt, dass sich im Zuge der Strukturverkleinerungen ebenfalls die Gate-Oxid-Dicke der Transistoren verringern lässt. Damit wird ein Absenken der Versorgungsspannung  $V_{DD}$  ermöglicht [ITR13b], was sich positiv auf alle Komponenten der Leistungsaufnahme auswirkt.

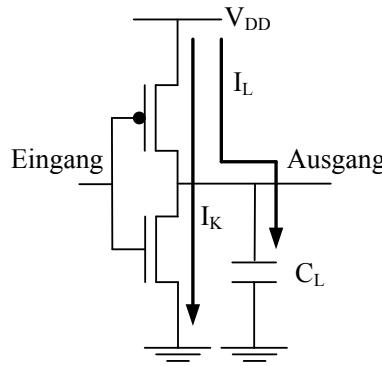

Diese setzt sich aus der dynamischen Leistungsaufnahme  $P_{Dyn}$ , der statischen Leistungsaufnahme  $P_{Leck}$  und der durch Kurzschlüsse bedingten Leistungsaufnahme  $P_K$  zusammen (siehe Gleichung 2.1).  $P_{Dyn}$  ist der Anteil der Leistung, der aufgenommen wird, solange eine Schaltung aktiv arbeitet, also während eine Lastkapazität  $C_L$  aufgeladen wird. Am Beispiel eines Inverters (siehe Abbildung 2.1) ist dies der Fall während der Ladestrom  $I_L$  fließt.  $P_K$  ist die Leistung, welche durch einen temporären Kurzschluss zwischen  $V_{DD}$  und Masse einer Schaltung aufgenommen wird. Für das Beispiel des Inverters bedeutet dies, dass für die Dauer von  $t_K$  beide Transistoren leiten und der Kurzschlussstrom  $I_K$  fließt (siehe Abbildung 2.1). Die Wahrscheinlichkeit, dass ein Kurzschluss auftritt ist dabei doppelt so hoch wie für  $P_{Dyn}$ , da sich bei jedem Pegelwechsel des Eingangssignals ein leitender Pfad bilden kann.  $P_{Leck}$  wird im Gegensatz zu den anderen beiden Leistungskomponenten fortwährend aufgenommen, also auch während die Schaltung inaktiv ist. Der Leckstrom  $I_{Leck}$  setzt sich aus einer Reihe einzelner Ströme mit unterschiedlichen, zum Teil technologisch bedingten Ursachen zusammen. Die drei wichtigsten Ströme sind der Subthreshold-Leckstrom  $I_{Sub}$ , der Gate-Oxid-Leckstrom  $I_{Gate}$  sowie der Leckstrom am pn-Übergang eines Transistors  $I_{pn}$ .  $I_{Sub}$  fließt zwischen Drain und Source eines Transistors während dieser theoretisch sperren sollte.  $I_{Gate}$  ist auf Ladungsträger zurückzuführen, welche aufgrund von Tunneleffekten in das Gate-Oxid eines Transistors gelangen.  $I_{pn}$  wird durch Diffusionsströme am pn-Übergang eines Transistors verursacht.

$$P_{Gesamt} = \underbrace{\alpha \cdot f \cdot C_L \cdot V_{DD}^2}_{P_{Dyn}} + \underbrace{2 \cdot \alpha \cdot f \cdot t_K \cdot I_K \cdot V_{DD}}_{P_K} + \underbrace{\sum I_{Leck} \cdot V_{DD}}_{P_{Leck}} \quad (2.1)$$

Das  $\alpha$  bezeichnet die Schaltwahrscheinlichkeit,  $C_L$  die umzuladende Lastkapazität (siehe auch Abbildung 2.1),  $f$  die Taktfrequenz der betrachteten Schaltung und  $t_K$  die Dauer des Kurzschlussstroms.  $I_K$  und  $I_{Leck}$  kennzeichnen die auftretenden Kurzschlussbeziehungsweise Leckströme.

Die Reduzierung der Leistungsaufnahme durch ein Absenken von  $V_{DD}$  ist allerdings durch eine minimale Schichtdicke von wenigen Atomlagen (ca. 1 bis 2 nm) des Gate-

**Abbildung 2.1:** Die in einer digitalen Schaltung auftretenden Lade- und Kurzschlussströme  $I_L$  und  $I_K$  am Beispiel eines Inverters

Oxids beschränkt. Andernfalls kommt es zur Verstärkung der auftretenden Leckströme [LBS04]. Die auf diese Weise erzielte Einsparung hat zudem eine reduzierte Signalintegrität zur Folge, da ein Absenken des  $V_{DD}$ -Pegels einen geringeren Signal-Rausch-Abstand (SNR) verursacht. Zudem darf sich  $V_{DD}$  nicht zu sehr dem Wert der Schwellspannung  $V_{Th}$  nähern, welche den für das Umschalten eines Transistors nötigen Spannungspegel angibt. Andernfalls verringert sich die Geschwindigkeit der Umladung der Lastkapazitäten, da ein geringerer Lade- beziehungsweise Entladestrom fließt.

Daher muss im gleichen Maße auch  $V_{Th}$  herabgesetzt werden, um das Verhältnis zwischen  $V_{DD}$  und  $V_{Th}$  zu wahren und ein korrektes Schaltverhalten des Transistors zu gewährleisten. Dies hat allerdings steigende Leckströme und somit eine erhöhte Leistungsaufnahme zur Folge, sodass letztendlich ein Kompromiss zwischen der Beeinflussung des Schaltverhaltens und der Kompensation der auftretenden Leckströme angestrebt werden muss [ITR13b].

Beschleunigte Umladevorgänge führen neben einer erhöhten Leistungsfähigkeit aber auch zu einer steigenden Belastung der Transistoren, da die Anzahl der Ladevorgänge je Zeiteinheit bei geringerer Belastbarkeit der Bauteile entweder konstant bleibt oder sogar zunimmt. Des Weiteren erhöht sich durch die zusätzlichen Schalt- und Umladevorgänge die Menge der abgegebenen Wärme, was wiederum einen negativen Einfluss auf  $V_{Th}$  hat [GWWT12] und zur Erhöhung der thermischen Verlustleistung beiträgt.

Die Auswirkung technologiebedingter Strukturverkleinerungen auf die Leistungsdichte ist in Abbildung 2.2 dargestellt. Wie erkennbar ist, erhöht sich die Dichte der thermischen Verlustleistung mit jeder Strukturverkleinerung bis 130 nm und stagniert von dort an auf konstant hohem Niveau. Die Dichte bezieht sich auf die Thermal Design Power (TDP), welche die maximal von einem Prozessor abgegebene Wärmeleistung angibt. Das hohe Niveau der TDP ist dabei eher praktischen Erwägungen als physikalischen Beschränkungen geschuldet. Durch effektivere, aber ungleich aufwändiger und

**Abbildung 2.2:** Einfluss der Fertigungstechnologie auf die Transistor- und Verlustleistungsdichte (Werte beruhen auf den Daten für Intel-Prozessoren der jeweiligen Technologiegeneration)

kostspieligere, Kühlösungen kann die Menge der abführbaren Wärme jederzeit erhöht werden. Ungeachtet dessen verdeutlicht der Verlauf dieser Kurve, dass sich die Intensität der Wärmewirkung auf einzelne Bauteile und Transistoren im Zuge technologischer Weiterentwicklungen stark erhöht hat. Hochintegrierte Schaltungen sind somit stetig steigenden Temperaturen und zunehmendem thermischen Stress ausgesetzt. Eine detaillierte Betrachtung bezüglich des Einflusses der Temperatur auf verschiedene Parameter mikro- und nanoelektronischer Schaltungen und daraus resultierender Effekte findet sich in Abschnitt 2.2.3.

Die vorangegangenen Betrachtungen zeigen, dass die Halbleiterfertigung mit jeder Technologiegeneration teils neuen und teils bereits bekannten, aber verschärften Problemen und Wechselwirkungen gegenüber steht. Diese können sich teilweise kritisch auf die Ausfallrate, die Lebensdauer, die Leistungsfähigkeit und die Leistungsaufnahme hochintegrierter Schaltungen auswirken. Aufgrund der engen Verknüpfung diverser Effekte und Mechanismen ist eine getrennte Behandlung der genannten Punkte nicht möglich, da beispielsweise die Optimierung eines Systems auf Leistungsfähigkeit immer auch Aspekte der Zuverlässigkeit und Leistungsaufnahme beeinflusst. Vielmehr sind Kompromisse notwendig, um leistungsfähige und dennoch zuverlässige und energieeffiziente Systeme zu realisieren.

## 2.2 Zuverlässigkeit

Zuverlässigkeit und Robustheit sind essentielle Faktoren für den Betrieb hochintegrierter Schaltungen. Zuverlässigkeit ist die Eigenschaft einer Schaltung, die ihr zugewiesene Funktion in einem gegebenen Zeitintervall wie vorgesehen zu erfüllen. Dies bedeutet, dass auch im Fehlerfall die Funktionsfähigkeit dauerhaft gewährleistet sein muss. Der Fokus liegt hierbei auf einer langfristigen Perspektive, welche auf eine möglichst lange Lebensdauer einer Schaltung ausgerichtet ist. Robustheit beschreibt hingegen die Fähigkeit einer Schaltung vorübergehenden Veränderungen oder Störungen von innen und außen standzuhalten. Schwankungen der Betriebsparameter und Umgebungsbedingungen dürfen möglichst keinen Einfluss auf den Zustand des Systems haben. Daher liegt der Fokus hier auf einer kurzfristigen, den aktuellen Betrieb betreffenden Perspektive.

Der Schwerpunkt dieser Arbeit liegt auf zuverlässigkeitbezogenen Problemstellungen und zielt damit auf Maßnahmen mit langfristiger Wirkung sowie eine Erhöhung der Lebensdauer. Aus diesem Grund bleibt im Folgenden Robustheit weitgehend unberücksichtigt. Dabei darf allerdings nicht vergessen werden, dass auch die Beseitigung oder Eindämmung robustheitsmindernder Effekte zu einem zuverlässigeren Betrieb und einer längeren Lebensdauer hochintegrierter Schaltungen beitragen kann.

### 2.2.1 Grundlagen und Definitionen

Prinzipiell muss bei zuverlässigkeitorientierten Betrachtungen zwischen den Fehlerursachen („Faults“), den dadurch auftretenden Fehlern („Errors“) und dem daraus resultierenden Fehlverhalten beziehungsweise Ausfall einer Schaltung („Failure“) unterschieden werden [HBB<sup>+</sup>11]. Das Fehlverhalten einer Schaltung ist als ihr Unvermögen zu interpretieren, die ihr zugedachte Aufgabe beziehungsweise Funktionsweise für eine definierte Dauer und unter festgelegten Bedingungen korrekt auszuführen [Iee90]. Diese Unterscheidung erlaubt eine Klassifizierung der Ursachen für das Fehlverhalten hochintegrierter Schaltungen, wie sie in Abbildung 2.4 [C.11] dargestellt ist und in Abschnitt 2.2.2 eingehender erläutert wird.

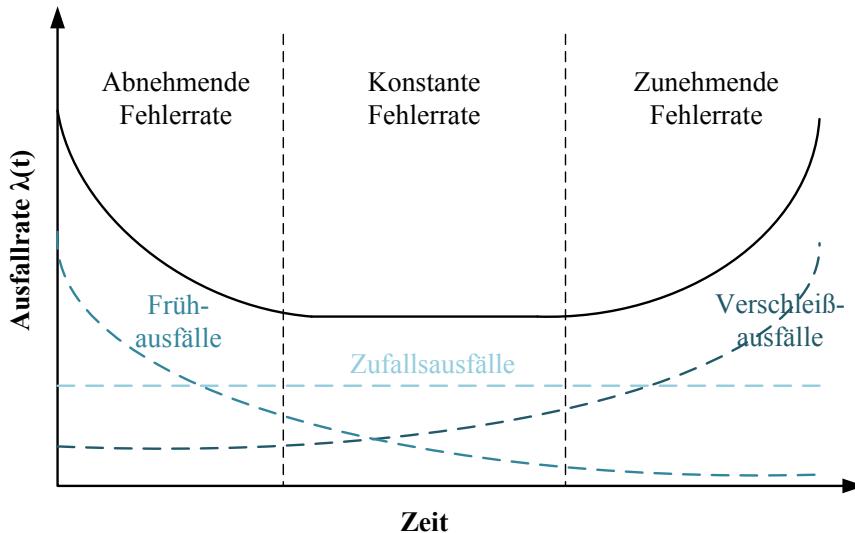

**Ausfallrate** Die Ausfallrate  $\lambda(t)$  ist ein geeigneter Parameter, um Bewertungen bezüglich der Zuverlässigkeit hochintegrierter Schaltungen durchzuführen. Sie gibt an, wie viele Komponenten einer Schaltung in einem vorgegebenen Zeitintervall durchschnittlich ein fehlerhaftes Verhalten aufweisen oder ausfallen. Beispielsweise bedeutet eine Fehlerrate von monatlich 25 %, dass ein Viertel aller Komponenten in einem Monat ausfällt oder, dass eine bestimmte Komponente im Verlauf eines Monats mit einer Wahrscheinlichkeit von 25 % ausfällt. Diese Rate hängt neben der Zeit von einer Vielzahl weiterer Parameter ab.

**Abbildung 2.3:** Lebenszyklus hochintegrierter Schaltungen: Darstellung des Zusammenhangs zwischen Lebensdauer und Ausfallrate in der Badewannenkurve

Erfahrungsgemäß folgt der Verlauf der Ausfallrate während der Lebensdauer eines Systems oder einer Schaltung der sogenannten Badewannenkurve [Iee90, KKW03]. Wie in Abbildung 2.3 zu erkennen ist, resultiert der badewannenförmige Funktionsverlauf der Ausfallrate aus den drei Einzelkomponenten der Frühausfälle, der Zufallsausfälle und der durch Verschleiß verursachten Ausfälle. Frühausfälle treten vorrangig in der ersten Phase der Lebensdauer einer Schaltung auf. Diese Phase zeichnet sich durch eine relativ hohe, aber rasch sinkende Ausfallrate aus und endet idealerweise vor der endgültigen Inbetriebnahme der Schaltung. Die Ausfallursachen in dieser Phase sind in der Regel Mängel im Entwurfs- und Produktionsprozess, sodass beispielsweise statische Fehler entstehen (siehe Abschnitt 2.2.2). In der zweiten Phase liegt die Ausfallrate auf konstant niedrigem Niveau. Da nur sporadisch auftretende Zufallsausfälle für fehlerhaftes Schaltungsverhalten sorgen, ist dies die Phase der effektiven Lebensdauer einer Schaltung. Mit dem Voranschreiten der Zeit findet der Übergang in die Phase der Spätausfälle statt. Während dieser sorgen Alterungs- und Verschleißerscheinungen für einen erneuten Anstieg der Ausfallrate, da viele Komponenten das Ende ihrer Lebensdauer erreicht haben.

**Zuverlässigkeit** Mithilfe der Ausfallrate  $\lambda(t)$  lässt sich die Zuverlässigkeit  $R(t)$  einer Schaltung nach Gleichung 2.2 berechnen.  $R(t)$  entspricht damit dem Gegenteil der Definition von Fehlverhalten und gibt die Wahrscheinlichkeit an, dass eine Komponente zum Zeitpunkt  $t$  ordnungsgemäß funktioniert [Jed11]. Der Verlauf von  $R(t)$  wird mithilfe der Weibull-Verteilung beschrieben. Durch die Anpassung des Parameters  $\beta$  können alle drei Phasen der Lebensdauer einer Schaltung repräsentiert werden [Jed11].

$$R(t) = e^{-\lambda \cdot t^\beta} \begin{cases} \beta < 1 & \text{für Frühausfälle} \\ \beta = 1 & \text{für Zufallsausfälle} \\ \beta > 1 & \text{für Verschleißausfälle} \end{cases} \quad (2.2)$$

**Mean Time To Failure** Die Mean Time To Failure (MTTF) gibt die erwartete mittlere Lebensdauer einer Schaltung an [Jed11]. Sie geht damit den zu  $R(t)$  entgegengesetzten Weg und gibt die durchschnittliche Zeit an, nach der eine Schaltung ein fehlerhaftes Verhalten aufweist oder ausfällt. Die MTTF errechnet sich nach Gleichung 2.3 aus dem Integral der Zuverlässigkeit  $R(t)$ , wobei eine konstante Fehlerrate  $\lambda$  mit  $\beta = 1$  für die Weibull-Verteilung angenommen wird. Dementsprechend ergibt sich die MTTF als Kehrwert der Ausfallrate. Dies gilt aufgrund der Annahme  $\beta = 1$  allerdings nur für die Phase der effektiven Lebensdauer.

$$MTTF = \int_0^\infty R(t) dt = \frac{1}{\lambda} \quad \text{für } \beta = 1 \quad (2.3)$$

### 2.2.2 Ausfallursachen

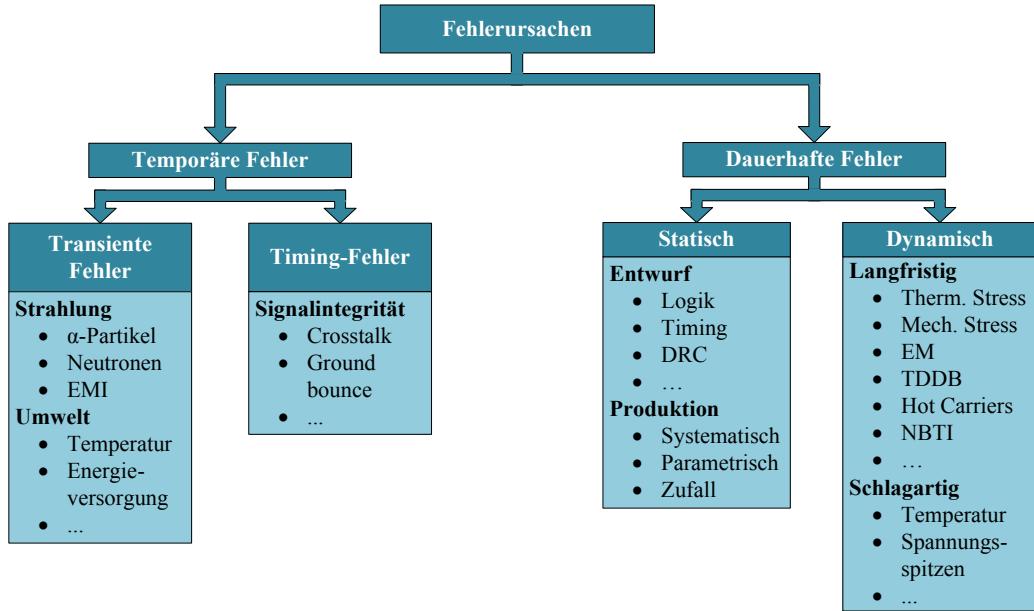

Abbildung 2.4 stellt eine Kategorisierung der Ursachen für das Fehlverhalten hochintegrierter Schaltungen dar. Das aus einem Fehler resultierende Fehlverhalten ist nicht dargestellt. Die zu diesem Fehlverhalten führenden „Errors“ und die jeweiligen Ursachen lassen sich aber nach dem abgebildeten Schema klassifizieren. So unterscheidet man zunächst zwischen Fehlern, die zu einem dauerhaften oder vorübergehenden Fehlverhalten führen. Die Kategorie der temporären Fehler wird an dieser Stelle nur kurz angerissen, da der Fokus dieser Arbeit auf der Verhinderung beziehungsweise dem Hinauszögern dauerhafter Fehler liegt.

**Temporäre Fehler** Vorübergehend bestehende Fehler treten während des Betriebs auf und betreffen nicht die physische Schaltung als solche, sondern die verarbeiteten oder gespeicherten Daten. Die Ursachen hierfür lassen sich in die zwei Gruppen der transienten und der Timing-Fehler einteilen.

Transiente Fehler werden durch Strahlung oder Umwelteinflüsse hervorgerufen. Für strahlungsbedingte Fehler sind Partikeleinschläge und Elektromagnetische Interferenzen (EMI) [RFFM03] verantwortlich. Partikeleinschläge werden beispielsweise von  $\alpha$ -Partikeln oder Neutronen [HZL<sup>+</sup>07, Nic05] verursacht. Beide Effekte rufen Veränderungen der in einzelnen Schaltungsteilen gespeicherten Ladungen hervor [MKSZ05, Bau05]. Durch Umwelteinflüsse hervorgerufene negative Effekte ergeben sich beispielsweise aus der Umgebungstemperatur oder Schwankungen der Energieversorgung [TB10].

**Abbildung 2.4:** Klassifikation der Ursachen für das Fehlverhalten hochintegrierter Schaltungen nach Dauer, Zeitpunkt des Auftretens und Ursprung [C.11]

Timing-Fehler resultieren aus die Signalintegrität betreffenden Phänomenen. Hierzu zählen Effekte wie Crosstalk [GWWT12] oder Ground Bounce [CGB97], welche zu einer gegenseitigen Beeinflussung benachbarter Leitungen oder unerlaubten Übergängen in Zustandsmaschinen führen können.

**Dauerhafte Fehler** Permanent bestehende Fehler treten während des Betriebs einer hochintegrierten Schaltung auf und bleiben für die restliche Lebensdauer bestehen. Dabei wird zwischen statischen und dynamischen Fehlern unterschieden.

Statische Fehler beruhen auf Entwurfs- oder Produktionsfehlern, sind bereits zu Beginn der Lebensdauer einer Schaltung vorhanden und treten erst bei Inbetriebnahme in Erscheinung. Auf diese Art der Fehler kann während des Betriebs kein Einfluss genommen werden. Zu der Gruppe der Entwurfsfehler zählen unter anderem Logikfehler während der Implementierung, Fehler während der Timing-Analyse oder Fehler in automatisierten Entwurfsschritten wie Design Rule Checking (DRC) oder Layout Versus Schematic (LVS). Produktionsfehler treten in Form von Zufallsfehlern auf, wie sie beispielsweise durch Werkstofffehler oder Verunreinigungen des Wafers hervorgerufen werden. Weitere Produktionsfehler sind parametrischer oder systematischer Natur. Parametrische Fehler sind das Resultat von Parameterschwankungen während der Fertigung, welche beispielsweise Fehler bei Oxidier-, Ätz- oder Dotierungsvorgängen zur Folge haben. Die korrekte Funktionalität ist dabei zwar prinzipiell gegeben, jedoch können vorgegebene Spezifikationen bezüglich der Leistungsfähigkeit oder der Leistungsaufnahme nicht ein-

gehalten werden. Systematische Fehler ergeben sich aus Unzulänglichkeiten während des Fertigungsprozesses und sind damit reproduzierbar. Hierzu gehören beispielsweise fehlerhafte Fotolithografiemasken oder generell Fehler in einzelnen Prozessschritten.

Die Gruppe der dynamischen Fehler ist für diese Arbeit von größerem Interesse, da diese Mechanismen enthält, welche während des Schaltungsbetriebs zu Alterungs- und Verschleißerscheinungen beitragen. Diese Mechanismen lassen sich weiter bezüglich der Form ihres Auftretens in schlagartige und langfristige Effekte einteilen. Phänomene schlagartigen Fehlverhaltens haben ihren Ursprung meist in unsachgemäßer Behandlung oder dem Betreiben außerhalb vorgegebener Betriebsparameter. Hierzu zählen unter anderem zu hohe Betriebs- und Umgebungstemperaturen oder auch Spannungsspitzen, wie sie beispielsweise durch elektrostatische Entladungen entstehen können. Auch mechanische Belastungen wie Stöße oder Erschütterungen können eine Schaltung beschädigen. Generell führen solche Erscheinungen zu einer sofortigen Beschädigung oder Zerstörung der Schaltung, können aber durch relativ einfache Maßnahmen vermieden werden. Von größerer Bedeutung sind dagegen langfristige Phänomene, welche aufgrund von Alterung und Verschleiß über teils sehr lange Zeiträume zu einer Verschlechterung des Schaltungsverhaltens oder zu einer Beschädigung der Schaltung führen. Da diese Fehlerkategorie von zentralem Interesse für diese Arbeit ist, wird sie im Folgenden gesondert aufgeführt.

**Langfristige Effekte** Thermischer und mechanischer Stress zählen zu den wichtigsten langfristigen Ursachen für Alterungs- und Verschleißerscheinungen. Thermischer Stress entsteht durch lokale oder globale Temperaturspitzen sowie häufige Temperaturschwankungen und starke Temperaturgefälle zwischen einzelnen Bereichen einer Schaltung. Mechanischer Stress hat seinen Ursprung beispielsweise in mechanischen Spannungen, welche auf die Komponenten einer Schaltung einwirken.

Des Weiteren trägt der Effekt der Elektromigration (EM) [Lie06] maßgeblich zu Verschleißerscheinungen bei. EM beschreibt den Materialtransport in Leiterbahnen infolge von Ionenbewegungen. Dieser Materialtransport wird durch den Stromfluss innerhalb der Leiterbahnen verursacht und führt zur Bildung von Hohlräumen (Voids) und Ablagerungen (Hillocks). Die Folge sind Leitungsunterbrechungen beziehungsweise Kurzschlüsse.

Time Dependent Dielectric Breakdown (TDDB) [Sta02, VSE<sup>+00</sup>] hingegen beeinträchtigt die Transistorfunktionsfähigkeit infolge hoher Feldstärken. TDDB definiert sich dabei als die langsam voranschreitende Zerstörung der als Isolator genutzten Oxid-Schicht zwischen Gate und Kanal eines Transistors, in welcher zunehmend Tunnelströme auftreten. Die Zerstörung dieser Schicht hat letzten Endes einen Kurzschluss zwischen Gate und Kanal zur Folge, sodass der Transistor funktionsunfähig ist.

Einen ähnlichen Effekt hat das Phänomen der heißen Ladungsträger (Hot Carriers) [CSGS85] beziehungsweise der Hot Carrier Injection (HCI). Heiße Ladungsträger sind aufgrund ihrer hohen kinetischen Energie in der Lage, in das Gate eines Transistors einzudringen und somit Leckströme zu verursachen. Oder sie verbleiben im Gate-Oxid und bilden Charge Traps, welche die Schaltgeschwindigkeit und weitere Transistorkennwerte beeinträchtigen. Ihr hohes Maß an kinetischer Energie erhalten die heißen Ladungsträger durch die Beschleunigung innerhalb eines starken elektrischen Feldes.

Der Effekt der Negative Bias Temperature Instability (NBTI) [SB03] betrifft p-Kanal-MOSFETs (Metal Oxide Semiconductor Field Effect Transistor) und wird durch negative Gate-Spannungen in Kombination mit hohen Temperaturen hervorgerufen. NBTI verursacht Charge Traps an der Grenzfläche zwischen Gate-Oxid und Transistorkanal sowie eine Verschiebung der Schwellspannung und ähnelt damit bezüglich der Auswirkungen stark dem Effekt der HCI. Weitere zu Verschleiß und Alterung führende Mechanismen sind beispielsweise Surface Inversion und Stress Migration [Jed11], welche zu Leckströmen und Materialtransport beziehungsweise -schwund führen.

Ein Großteil der für Alterung und Verschleiß einer Schaltung verantwortlichen Mechanismen ist temperaturabhängig und wird durch hohe Temperaturen beschleunigt. Deshalb konzentriert sich diese Arbeit im Folgenden auf die Eindämmung und Abschwächung dieser Effekte, da auf diese Weise Verschleiß- und Ausfallerscheinungen am effektivsten entgegen gewirkt werden kann. Eine detailliertere Betrachtung der Temperaturabhängigkeit der betreffenden Mechanismen findet im Folgenden statt.

### 2.2.3 Einfluss der Temperatur

In Abschnitt 2.2.2 wurden unter anderem verschiedene physikalische Mechanismen vorgestellt, welche langfristig die Lebensdauer hochintegrierter Schaltungen beeinträchtigen. Aufgrund des signifikanten Einflusses der Temperatur werden in diesem Abschnitt nun die wichtigsten solcher Mechanismen näher beleuchtet, um aufzuzeigen, inwiefern die Reduzierung der Temperatur zu einer Erhöhung der Zuverlässigkeit beitragen kann.

**Lebensdauer und Beschleunigung von Alterungerscheinungen** Generell gilt das Arrhenius-Modell [Jed11] als Ausgangspunkt für die Beschreibung der Temperaturabhängigkeit von Ausfallursachen. Mithilfe von Gleichung 2.4 [Jed11] ist es möglich, eine grobe Aussage über die temperaturbedingte Time To Failure (TTF), also die Dauer bis zum Eintreten von Alterungs- und Verschleißerscheinungen sowie Ausfällen, zu treffen. Dabei ist  $E_A$  die Aktivierungsenergie des betreffenden, zum Ausfall führenden Mechanismus,  $k_{Boltz}$  ist die Boltzmann-Konstante ( $8,62 \cdot 10^{-5}$  eV/K) und T ist die Temperatur. Aus diesem Zusammenhang ergibt sich eine Beschleunigung von Ausfällen, welche mit steigender Temperatur exponentiell zunimmt.

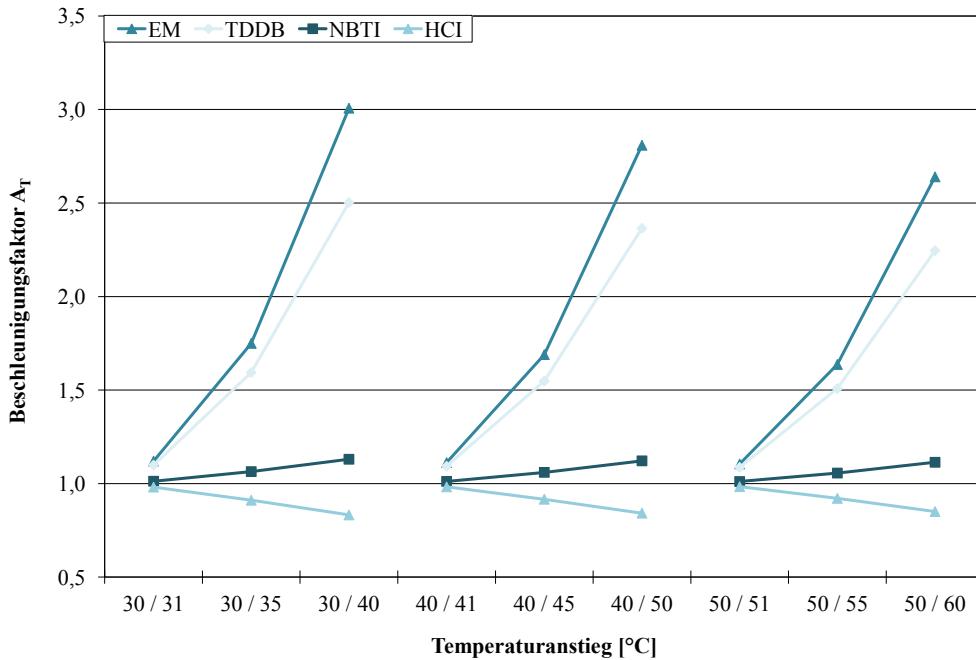

Es ist zudem möglich, einen Faktor  $A_T$  für die Beschleunigung [Jed11] eines konkreten Mechanismus bei einer Veränderung der Temperatur zu bestimmen (siehe Gleichung 2.5). Dies setzt eine konstante Ausfallrate (siehe Abschnitt 2.2.1) sowie bekannte Werte für  $E_A$  und  $T$  voraus.  $A_T$  repräsentiert damit das Verhältnis zwischen den unterschiedlichen, für verschiedene Bedingungen vorherrschenden Ausfallraten beziehungsweise TTFs.  $\lambda_1$  und  $\lambda_2$  sind die jeweiligen Ausfallraten für die Temperaturen  $T_1$  und  $T_2$ .

$$TTF \propto e^{\frac{E_A}{k_{Boltz} \cdot T}} \quad (2.4)$$

$$A_T = \frac{\lambda_{T_1}}{\lambda_{T_2}} \propto e^{\frac{-E_A}{k_{Boltz}} \cdot (1/T_1 - 1/T_2)} \quad (2.5)$$

**Elektromigration** Der bereits vorgestellte Mechanismus der EM basiert auf Materialtransport infolge von Kollisionen zwischen den Ladungsträgern eines durch einen Leiter fließenden Stromes und den Ionen des Leitermaterials. Der Effekt verstärkt sich mit steigenden Stromdichten aufgrund sinkender Leiterquerschnitte, welche im Zuge von Strukturverkleinerungen unvermeidbar sind. Dieser Sachverhalt ist vereinfacht für einen quadratischen Leiterquerschnitt in Gleichung 2.6 dargestellt.  $\vec{J}$  ist die Stromdichte,  $a$  ist die Seitenlänge des Leiterquerschnitts und  $I$  ist der Strom. Wird beispielsweise die Seitenlänge  $a$  halbiert, vervierfacht sich die Stromdichte. Dieser theoretisch quadratische Einfluss von Strukturverkleinerungen auf die Stromdichte reduziert sich in der Realität, da die Leiterhöhe in der Regel nicht in gleichem Maße verkleinert wird. Dies ändert jedoch nichts an der Relevanz dieses Effektes. Darüber hinaus steigt die Stromdichte an Stellen im Leiter an, an denen sich Hohlräume bilden, da dort der Leiterquerschnitt im Laufe der Zeit abnimmt.

Die  $TTF_{EM}$  beschreibt die Dauer bis zum Auftreten von Ausfällen durch EM und berechnet sich nach Gleichung 2.7, welche dem Black'schen Gesetz folgt [Cle97].  $J$  und  $J_{krit}$  bezeichnen die aktuelle sowie die für EM kritische Stromdichte.  $N$  ist der Stromdichteexponent,  $E_A$  ist die Aktivierungsenergie für EM und  $T$  ist die Temperatur. Für Kupferleitungen gelten zum Beispiel  $1,1 < N < 2$  und  $E_A = 0,85$  bis  $0,95$  eV [Jed11]. Neben der Stromdichte beeinflusst somit auch die Temperatur die EM. Die temperaturbedingte Beschleunigung  $A_T$  ist mithilfe der Gleichungen 2.5 und 2.7 in Abbildung 2.5 für Temperaturerhöhungen von  $1^\circ\text{C}$ ,  $5^\circ\text{C}$  und  $10^\circ\text{C}$  ausgehend von  $30^\circ\text{C}$ ,  $40^\circ\text{C}$  und  $50^\circ\text{C}$  dargestellt. Wie zu erkennen ist, wird  $A_T$  sehr schnell größer, sodass sich bei einer Temperaturerhöhung von  $10^\circ\text{C}$  bereits eine Beschleunigung um das 3-fache. Dies ist als eine Verkürzung der TTF auf ein Drittel des Ausgangswertes zu interpretieren. Eine Erhöhung der Ausgangstemperatur auf  $50^\circ\text{C}$  führt hingegen zu einer Reduzierung der Beschleunigung auf das 2,6-fache, was mit einer an diesem Punkt bereits niedrigeren TTF zu erklären ist, wodurch sich das Verhältnis zu TTFs höherer Temperaturen verkleinert.

Die Voraussetzung für solche Berechnungen ist die Annahme, dass alle Parameter außer der Temperatur konstant bleiben. Für  $E_A$  wird ein Wert von 0,9 eV angenommen [Jed11].

$$\vec{J} = \frac{\vec{I}}{\vec{A}} \propto \frac{1}{a^2} \quad (2.6)$$

$$TTF_{EM} \propto (J - J_{krit})^{-N} \cdot e^{\frac{E_A}{k\text{Boltz}\cdot T}} \quad (2.7)$$

**Time Dependent Dielectric Breakdown** Ein ähnlicher Effekt ist für TDDB zu beobachten. Die durch TDDB verursachte, langfristige Zerstörung der Oxid-Schicht zwischen Gate und Kanal eines Transistors beruht auf hohen Feldstärken. Diese verursachen minimale Tunnelströme, welche sich aufgrund des Kreislaufs aus zunehmenden Strömen und sich erhöhenden Temperaturen im Laufe der Zeit schädigend auf die Oxid-Schicht auswirken und diese zerstören.

Die Dauer bis zum Auftreten von TDDB-bedingten Ausfällen  $TTF_{TDDB}$  wird mit Hilfe von Gleichung 2.8 berechnet [Jed11]. Dabei ist  $\gamma$  ein temperaturabhängiger Feldbeschleunigungsparameter,  $E_{ox}$  ist das von außen einwirkende elektrische Feld,  $E_A$  ist die Aktivierungsenergie für TDDB und T ist die vorherrschende Temperatur. Für  $\gamma$  und  $E_A$  gelten Werte von 2,5 bis 3,5 cm/MV beziehungsweise 0,6 bis 0,9 eV [Jed11].  $E_{ox}$  ergibt sich als der Quotient aus Spannung und Oxid-Dicke in MV/cm. Neben der anliegenden Spannung, der Oxid-Dicke sowie dem elektrischen Feld hat auch die Temperatur einen Einfluss auf TDDB-bedingte Erscheinungen. In Abbildung 2.5 ist ein zu EM identisches Verhalten erkennbar. Der absolute Unterschied zwischen den einzelnen Werten für  $A_T$  lässt sich mit der niedrigeren Aktivierungsenergie von 0,75 eV [Jed11] erklären. Diese ist neben der Temperatur der einzige Faktor, der bei der Berechnung von  $A_T$  einen Einfluss hat. Alle weiteren Parameter werden als konstant angenommen und  $\gamma$  wird mit 3 cm/MV festgelegt [Jed11]. Die stark ausgeprägte Beschleunigung der zur Zerstörung der Oxid-Schicht führenden Abläufe verdeutlicht auch hier den signifikanten Einfluss der Temperatur.

$$TTF_{TDDB} \propto e^{-\gamma \cdot E_{ox}} \cdot e^{\frac{E_A}{k\text{Boltz}\cdot T}} \quad (2.8)$$

**Hot Carrier Injection** HCI beschreibt das Phänomen, durch welches heiße Ladungsträger bis in das Gate eines Transistors vordringen oder im Gate-Oxid verbleiben. Das dafür nötige hohe Maß an kinetischer Energie erhalten die heißen Ladungsträger durch die Beschleunigung innerhalb eines starken elektrischen Feldes. HCI hat sowohl Leckströme als auch eine langfristige Verschlechterung der Transistorkennwerte zur Folge. Letzteres wird auch als Device Degradation bezeichnet und umfasst unter anderem Änderungen der Schaltgeschwindigkeit sowie der Schwell- und Sperrspannung.

Die  $TTF_{HCl}$  für n-Kanal-Transistoren ist in Gleichung 2.9 beschrieben [Jed11].  $I_{sub}$  ist der Strom ins Substrat des Transistors,  $N$  ist eine konstante ganze Zahl von 2 bis 4,  $E_A$  ist die Aktivierungsenergie für HCl mit Werten von -0,2 bis +0,4 eV und  $T$  ist die Temperatur. Für p-Kanal-Transistoren existieren zwei weitere HCl-Modelle, welchen je nach Kanallänge des Transistors unterschiedliche TTF-Gleichungen zugrunde liegen. Abbildung 2.5 zeigt den Temperatureinfluss auf HCl für n-Kanal-Transistoren, welcher mit steigenden Temperaturen abnimmt. Die Ursache hierfür ist einerseits die für das Beispiel mit -0,15 eV negativ festgelegte Aktivierungsenergie ( $N$  wurde mit 3 angenommen). Des Weiteren sorgen eine reduzierte Ladungsträgermobilität, eine reduzierte Anzahl heißer Ladungsträger sowie die Temperaturabhängigkeit einzelner Transistorparameter (z. B. Schwellspannung (siehe Gleichung 2.11) oder Fermi-Potential) für eine reduzierte Empfindlichkeit gegenüber HCl [BGR<sup>+</sup>97]. HCl ist somit ein Mechanismus, dessen Auswirkungen durch steigende Temperaturen abgeschwächt werden. Dies geschieht allerdings auf Kosten der temperaturbedingten Drift einzelner Transistorkennwerte und sorgt somit lediglich für eine andere Form der Device Degradation.

$$TTF_{HCl,n-Kanal} \propto (I_{sub})^{-N} \cdot e^{\frac{E_A}{k_B T}} \quad (2.9)$$

**Negative Bias Temperature Instability** NBTI ähnelt in seinen Auswirkungen stark HCl, da es hier in ähnlicher Art und Weise zu Device Degradation sowie einer dauerhaften Verringerung der Ladungsträgermobilität kommt. Im Gegensatz zu HCl betrifft NBTI allerdings nur p-Kanal-Transistoren und entsteht durch negative Gate-Spannungen und vergleichsweise hohe Temperaturen von über 100 °C, wie sie üblicherweise während der Burn-In-Phase oder dem Betrieb von Hochleistungs-ICs auftreten [SB03].

Gleichung 2.10 beschreibt die TTF für NBTI-induzierte Effekte [Jed11].  $E_A$  ist die Aktivierungsenergie für NBTI,  $T$  ist die Temperatur,  $V_G$  ist die Gate-Spannung,  $\alpha$  ist der Exponent für die Gate-Spannung und  $n$  ist der Zeit-Exponent. Abbildung 2.5 zeigt, dass NBTI mit steigender Temperatur beschleunigt wird. Diese Beschleunigung ist aber zumindest in Bereichen unter 100 °C mit einem Faktor von 1,1 relativ niedrig. Für das Beispiel wurden  $E_A$  mit 0,1 eV [CLKK06],  $\alpha$  mit 3,5 und  $n$  mit 0,25 festgelegt [Jed11]. Trotz des scheinbar geringen Einflusses gewinnt NBTI mit jeder neuen Technologiegeneration an Bedeutung, da jeder Skalierungsschritt die Anfälligkeit gegenüber NBTI erhöht und somit beispielsweise eine Verschiebung der Schwellspannung begünstigt. Der Grund hierfür liegt in der Dichte der Charge Traps, welche mit der durch Skalierungsprozesse dünner werdenden Dicke des Gate-Oxids zunimmt [SB03].

$$TTF_{NBTI} \propto \left( e^{\frac{E_A}{k_B T}} \cdot V_G^\alpha \right)^{\frac{1}{n}} \quad (2.10)$$

**Abbildung 2.5:** Einfluss eines Temperaturanstiegs um verschiedene Werte auf den Beschleunigungsfaktor  $A_T$  für EM, TDDB, HCI und NBTI

Prinzipiell lässt sich aus den gezeigten Mechanismen die Tendenz ableiten, dass eine Temperaturerhöhung signifikant zur Beschleunigung von Alterungs- und Verschleißerscheinungen beiträgt. Dies röhrt zumeist von beschleunigten elektrochemischen Reaktionen her. Das zugrunde liegende Arrhenius-Modell basiert dabei auf der Van't Hoffschen Regel, welche auch als Reaktionsgeschwindigkeit-Temperatur-Regel (RGT-Regel) bekannt ist. Diese besagt, dass sich für eine Temperaturerhöhung um 10 K die Geschwindigkeit chemischer Reaktionen verdoppelt. Übertragen auf hochintegrierte Schaltungen und Bezug nehmend auf die in Abbildung 2.5 gezeigten Ergebnisse, lässt sich damit die grobe Faustregel aufstellen, dass eine dauerhafte Temperaturerhöhung um 10 K eine Halbierung der Lebensdauer integrierter Schaltungen zur Folge hat.

**Transistorkennwerte** Die Drift der Schwellspannung  $V_{Th}$  ist ein Effekt, den TDDB, HCI und NBTI gemeinsam haben. Neben der Beeinflussung der Schwellspannung durch die genannten Mechanismen weist  $V_{Th}$  selbst ebenfalls eine Temperaturabhängigkeit auf. Diese Abhängigkeit wird mithilfe von Gleichung 2.11 beschrieben [GWWT12]. Die mit steigender Temperatur sinkende Schwellspannung führt einerseits zu höheren Drain-Strömen und damit zu einer höheren Schaltgeschwindigkeit. Andererseits nehmen auf diese Weise auch die Leckströme zu, welche durch Tunneleffekte und vor allem durch sogenannte Sub-Threshold-Ströme zwischen Drain und Source eines Transistors verursacht werden. Das temperaturabhängige Verhalten dieser Leckströme ist in Gleichung 2.12 be-

schrieben [DN07].  $I_S$  ist der Sättigungsstrom, also der im Sperrbereich des Transistors zwischen Drain und Source maximal fließende Strom.  $V_{DS}$  ist die im Sperrbereich zwischen Drain und Source anliegende Spannung, welche zwischen 0 und  $V_{Th}$  liegt.  $q$  ist die Elementarladung und  $T$  die Temperatur. Wie zu erkennen ist, wächst mit steigender Temperatur der im Sperrzustand fließende Strom. Dabei bestimmt in der Praxis allerdings nicht  $I_S$  den maximalen Leckstrom, sondern die temperaturabhängige Generierung von Ladungsträgern.

$$V_{Th} = V_{Th0} + \alpha_{V_{Th}} \cdot (T - T_0) \quad \text{mit } \alpha_{V_{Th}} = -2 \dots -4 \left[ \frac{mV}{K} \right] \quad (2.11)$$

$$I_L = I_S \left( 1 - e^{-\left( \frac{q \cdot V_{DS}}{k_{Boltz} \cdot T} \right)} \right) \quad (2.12)$$

Darüber hinaus hat die Temperatur aber auch Einfluss auf die Leistungsfähigkeit einer Schaltung. Besonders temperaturabhängige Mechanismen, welche die Transistor-kennwerte beeinflussen und über längere Zeiträume eine Parameterdrift bewirken, haben signifikanten Einfluss auf die Leistungsfähigkeit einer hochintegrierten Schaltung. Hierzu zählen beispielsweise HCI und NBTI, welche die Schaltgeschwindigkeit der Transistoren negativ beeinflussen. Zudem ist die Mobilität der Ladungsträger temperatur-abhängig (siehe Gleichung 2.13). Diese Beziehung zwischen Temperatur und Mobilität führt zu einem mit steigender Temperatur sinkenden Drain-Strom. Die Folge ist, dass die Schaltung durch verlängerte Umladevorgänge langsamer wird.

$$\mu = \mu_0 \cdot \left( \frac{T}{T_0} \right)^{\alpha_\mu} \quad \text{mit } \alpha_\mu = -1,5 \dots -2,5 \quad (2.13)$$

## 2.2.4 Existierende Techniken zur Steigerung der Zuverlässigkeit

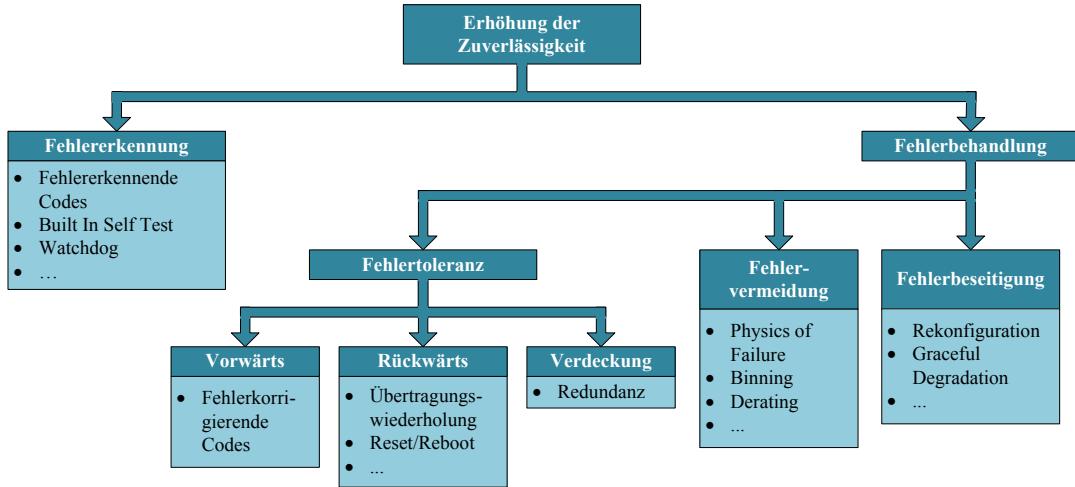

In diesem Abschnitt soll ein kurzer Abriss über existierende Ansätze und Methoden zur Erhöhung der Zuverlässigkeit hochintegrierter Schaltungen gegeben werden. Im Folgenden wird dazu eine grobe Kategorisierung des Reliability Engineering vorgenommen.

**Redundanz** Der Ansatz der Redundanz [Iee90] sieht eine Mehrfachauslegung einzelner Komponenten eines Systems vor. Dies kann sowohl echte Komponenten als auch Daten, Informationen und Operationen betreffen. Damit lassen sich je nach gewählter Methode räumliche, informationsbezogene und zeitliche Redundanzen erzeugen. Diese werden genutzt, um vorhandene Fehler zu unterdrücken oder deren Entstehung zu verhindern. Ein populärer Vertreter der räumlichen Redundanz ist die Triple Modular Redundancy (TMR) [Sie91]. TMR basiert auf einer dreifachen Auslegung identischer Hardware-Komponenten, welche parallel die ihr zugewiesene Funktion ausführen. Mithilfe eines Mehrheitsvotums wird ein Ergebnis erzeugt. Damit wird das möglicherweise

fehlerhafte Ergebnis einer defekten Komponente unterdrückt. Eine weitere Möglichkeit TMR zu nutzen, ist die zusätzlichen Komponenten als Reserve bereit zu halten und erst dann zu aktivieren, wenn die Primärkomponente fehlerhaft ist.

**Derating** Derating verfolgt eine andere Strategie und verzichtet auf Redundanz. Stattdessen wird eine Komponente gewollt unterhalb ihrer maximalen Leistungsfähigkeit betrieben, um die Verlustleistung und damit die erzeugte Abwärme zu reduzieren. Ob und in welchem Umfang eine solche Drosselung stattfindet, wird durch die Auswertung verschiedener Parameter wie beispielsweise der Betriebstemperatur oder der Leistungsaufnahme entschieden. Das Ziel dabei ist, einer Beschädigung oder der Zerstörung einer Komponente vorzubeugen. Bekannte Vertreter sind das Dynamic Voltage Scaling (DVS) sowie das Dynamic Frequency Scaling (DFS) zur dynamischen Anpassung von Versorgungsspannung und Taktfrequenz. Derating wird häufig in der Luft- und Raumfahrt [ESA06] sowie im militärischen Bereich [Mil92] eingesetzt, um die Lebensdauer elektronischer Komponenten zu erhöhen.

**Physics of Failure** Die Strategie der Physics of Failure [GPW02] basiert auf der Identifizierung und dem Verstehen der physikalischen Prozesse und Mechanismen, welche sich hinter einem Defekt verbergen. Auf diese Weise können Fehler bereits während der Entwurfsphase durch entsprechende Maßnahmen verhindert werden. Solche Maßnahmen basieren meist auf physikalischen oder chemischen Gesetzmäßigkeiten sowie theoretischen Analysen, Simulationen und Berechnungen. Beispielsweise werden zur Verringerung des TDDB-Effekts (siehe Abschnitt 2.2.2) „high-k“-Materialien wie Hafnium für das Gate-Oxid verwendet, um Leckströme zu reduzieren.

Diese Kategorisierung ist angesichts der Vielzahl möglicher Fehlerursachen (siehe Abschnitt 2.2.2), deren Wechselwirkungen und der Komplexität hochintegrierter Systeme allerdings nicht ausreichend. In Abbildung 2.6 ist eine erweiterte Kategorisierung dargestellt, welche die bereits vorgestellten Strategien in konkreter Form umsetzt sowie um weitere Ansätze ergänzt. Diese Kategorisierung ist teilweise [C.11] entlehnt und wird im Folgenden eingehender erläutert. Die aufgeführten Maßnahmen und Strategien zur Erhöhung der Zuverlässigkeit erheben keinen Anspruch auf Vollständigkeit und stellen lediglich einen Auszug dar. Detailliertere Ausführungen zu diesem Thema sind beispielsweise [Bor05, RK09] zu entnehmen.

## Fehlererkennung

Um die Zuverlässigkeit hochintegrierter Systeme durch eine gezielte Fehlerbehandlung steigern zu können, ist zunächst eine Fehlererkennung notwendig. Je nachdem in wel-

Abbildung 2.6: Kategorisierung der Strategien zur Erhöhung der Zuverlässigkeit

cher Phase (Entwurf oder Betrieb) oder auf welcher Ebene (z. B. System- oder Modulebene) auf mögliche Fehler geprüft werden soll, eignen sich verschiedene Ansätze. Fehlererkennende Datencodierungen [FKCC06, DT07] werden bei der Datenübertragung und -speicherung eingesetzt, um beispielsweise transiente Fehler (siehe Abschnitt 2.2.2) zu erkennen. Damit eignen sich solche Verfahren nur für den Betrieb. Bekannte Vertreter sind die zyklische Redundanzprüfung (Cyclic Redundancy Check (CRC)), Hash-Funktionen sowie die Verwendung von Paritätsbits und XOR-Prüfsummen.

Auf Modul- und Systemebene eignen sich Built In Self Tests (BIST) [McC85] für eine Fehlererkennung sowohl während des Entwurfs als auch während des Betriebs. Zu diesem Zweck besitzt eine Schaltung zusätzliche Logik, welche Testmuster erzeugt und mit den vorgegebenen korrekten Resultaten vergleicht. Damit lassen sich vor allem statische Fehler lokalisieren. BIST-Varianten sind Analog-, Mixed-Signal- und Logik-BIST sowie der Boundary Scan Test [RTZ98].

Eine weitere Möglichkeit der Fehlererkennung ist der Einsatz sogenannter Watchdogs [Lam12]. Dies sind Systemkomponenten, welche den Betrieb anderer Komponenten überwachen und die Erkennung eines möglichen Fehlers oder Problems melden, so dass eine Fehlerbehandlung stattfinden kann. Watchdogs können als Software und Hardware ausgelegt sein und dementsprechend entweder die Funktion anderer Hardware-Komponenten beziehungsweise Software-Module überwachen. Generell lässt sich auch die Überwachung verschiedener Systemparameter (z. B. Übertragungsdauer oder Daten- und Bitfehlerrate) zur Erkennung von Fehlern nutzen, da drastische Schwankungen solcher Parameter auf ein Problem hindeuten können.

## Fehlerbehandlung

Grundlegend existieren drei verschiedene Ansätze auf erkannte Fehler zu reagieren. Diese unterscheiden sich in ihren konkreten Realisierungen teils stark und beziehen sich oftmals auf die eingangs vorgestellte Einteilung in Redundanz, Derating und Physics of Failure.

**Fehlertoleranz** Die Strategie der Fehlertoleranz hat das Ziel, auch im Falle eines Fehlers in einer oder mehreren Komponenten für einen möglichst reibungslosen und fehlerfreien Betrieb zu sorgen. Hierfür stehen drei Möglichkeiten zur Verfügung.