# **High-Power Hybrid Si/SiC Active Neutral Point Clamped Converter**

Dissertation to obtain the degree of Doctor of Engineering (Dr.-Ing) from the Faculty of Computer Science and Electrical Engineering at the University of Rostock

Submitted by:

Pham Ha Trieu To, born on 27.03.1986 in Can Tho, Vietnam

from Rostock.

Rostock, 27.03.2024

## **Thesis Reviewers:**

- 1. Prof. Dr.-Ing. Hans-Günter Eckel, University Rostock, Institute of Electrical Power Engineering, Chair for Power Electronics and Electrical Drives.

- 2. Prof. Dr.-Ing. Mark Matthias Bakran, University Bayreuth, Fakultät für Ingenieurswissenschaften, Lehrstuhl für Mechatronik.

This work was done under the supervision of Prof. Dr.-Ing. Hans-Günter Eckel, University Rostock, Institute of Electrical Power Engineering, Chair for Power Electronics and Electrical Drives from 2019 to 2024.

Submission date: 27.03.2024

Defense date: 16.09.2024

Selbstständigkeitserklärung

Ich versichere hiermit, die vorliegende Dissertation eigenständig und ausschließlich unter

Verwendung der angegebenen Hilfsmittel angefertigt zu haben. Alle öffentlichen Quellen sind

als solche kenntlich gemacht.

Rostock, 27 March 2024

M.Sc. To Pham Ha Trieu

Hiermit erkläre ich, dass die vorgelegte Promotionsschrift bisher weder im Ausland noch

im Inland in gleicher oder ähnlicher Form einer anderen Prüfungsbehörde vorgelegt wurde.

Rostock, 27 March 2024

M.Sc. To Pham Ha Trieu

ii

I would like to say a special thank you to Professor Eckel for his support and giving me a chance to work on this interesting topic. My passion for power electronics has come from his interesting lectures during my master study at university of Rostock. I appreciate for the precious time he spent with me just to show me how to write the first abstract submission. That is the starting point for all my publications.

I would like to thank all the colleagues, who helped me during my working here, in the power electronics lab.

Finally, I would like to express great appreciation to my wife and my family for always supporting me unconditionally during my Phd journey and in my personal life.

## **Abstract**

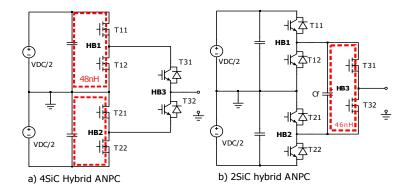

Inverter with low output current ripple is necessary for many applications. Conventional IGBT based two-level inverter usually needs a bulky LCL filter at the output to suppress the high frequency harmonics. The filter volume can be significantly reduced if the three-level inverter is used and even better if it is switched at high frequency. The hybrid Si/SiC active neutral point clamped (ANPC) inverter is an ideal option for this solution. Thanks to the flexibility of different switching schemes, ANPC is able to relocate the fast switching devices to SiC MOSFETs and the slow switching devices to Si IGBTs. By doing so, the switching losses is strongly reduced at high switching frequency. The solution is not new for low power applications where all the switches are discrete devices connected on a small PCB or all the switches are integrated inside a module, which have low commutation loops' inductances. In high power applications, the concept has the main challenge of high commutation loops' inductances which limit the switching speed of the devices. There are two types of hybrid ANPC distinguished by the number of SiC MOSFETs are used: 4SiC and 2SiC hybrid ANPC. The 4SiC version is preferred for high power applications due to its small commutation loops of the high-speed SiC MOSFETs. In contract, 2SiC hybrid ANPC is impossible to use for high power applications because of its MOSFETs' long commutation loops. Actually, the long commutation loops can be decoupled by laying a decoupling capacitor near to SiC MOSFET. But the presence of the decoupling capacitor in the high power 2SiC hybrid ANPC topology poses many challenges in the design process and practical implementation. This dissertation is aimed to address those issues which are very specified for this topology. Additionally, designing a high-speed switching MOSFET presents its own set of challenges. Some novel and interesting solutions to those problems are also proposed in this dissertation. An experimental 500kW 2SiC hybrid ANPC was built and run continuously to prove those proof of concepts.

# Zusammenfassung

Wechselrichter mit geringer Ausgangsstromwelligkeit sind für viele Anwendungen erforderlich. Herkömmliche IGBT-basierte Zwei-Pegel-Wechselrichter benötigen in der Regel einen sperrigen LCL-Filter am Ausgang, um die hochfrequenten Oberwellen zu unterdrücken. Das Volumen des Filters kann erheblich reduziert werden, wenn ein dreistufiger Wechselrichter verwendet wird, und noch besser, wenn er mit hoher Frequenz geschaltet wird. Der hybride Si/SiC-Active Neutral Point Clamped (ANPC)-Wechselrichter ist eine ideale Option für diese Lösung. Dank der Flexibilität verschiedener Schaltschemata ist ANPC in der Lage, die schnell schaltenden Bauelemente auf SiC-MOSFETs und die langsam schaltenden Bauelemente auf Si-IGBTs zu verlagern. Auf diese Weise werden die Schaltverluste bei hoher Schaltfrequenz stark reduziert. Die Lösung ist nicht neu für Anwendungen mit geringem Stromverbrauch, bei denen alle Schalter als diskrete Bauelemente auf einer kleinen Leiterplatte verbunden sind oder alle Schalter in ein Modul integriert sind, das geringe Induktivitäten in den Kommutierungsschleifen aufweist. Bei Anwendungen mit hoher Leistung besteht die größte Herausforderung des Konzepts in den hohen Induktivitäten der Kommutierungsschleifen, die die Schaltgeschwindigkeit der Geräte begrenzen. Es gibt zwei Arten von hybriden ANPC, die sich durch die Anzahl der verwendeten SiC-MOSFETs unterscheiden: 4SiC- und 2SiC-Hybrid-ANPC. Die 4SiC-Version wird aufgrund der kleinen Kommutierungsschleifen der Hochgeschwindigkeits-SiC-MOSFETs für Hochleistungsanwendungen bevorzugt. Der 2SiC-Hybrid-ANPC hingegen kann wegen der langen Kommutierungsschleifen seiner MOSFETs nicht für Hochleistungsanwendungen eingesetzt werden. Die langen Kommutierungsschleifen können zwar durch einen Entkopplungskondensator in der Nähe des SiC-MOSFET entkoppelt werden. Aber das Vorhandensein des Entkopplungskondensators in der 2SiC-Hybrid-ANPC-Topologie für hohe Leistungen stellt viele Herausforderungen im Designprozess und in der praktischen Umsetzung dar. Diese Dissertation befasst sich mit den Problemen, die für diese Topologie besonders wichtig sind. Darüber hinaus stellt die Entwicklung eines Hochgeschwindigkeits-Schalt-MOSFETs eine eigene Reihe von Herausforderungen dar. Einige neuartige und interessante Lösungen für diese Probleme werden in dieser Dissertation ebenfalls vorgeschlagen. Ein experimenteller 500 kW 2SiC-Hybrid-ANPC wird gebaut, um diese Konzepte zu beweisen.

# Contents

| 1. | Inti | roduction                                                     | 1  |

|----|------|---------------------------------------------------------------|----|

|    | 1.1  | Filter inductor's volume                                      | 1  |

|    | 1.2  | Three-level active neutral point clamp (3L-ANPC)              | 5  |

|    |      | 1.2.1 ANPC switching states                                   | 5  |

|    |      | 1.2.2 ANPC's flexible pulse width modulation (PWM) strategies | 7  |

|    |      | 1.2.3 ANPC's different commutation loops                      | 10 |

|    | 1.3  | Hybrid Si/SiC ANPC                                            | 11 |

|    | 1.4  | The motivation and challenges of this dissertation            | 13 |

|    | 1.5  | New contributions from this dissertation                      | 14 |

| 2. | Sw   | ritching Oscillations In a 2SiC Hybrid ANPC                   | 17 |

|    | 2.1  | Equivalent oscillation circuits of a 2SiC hybrid ANPC         | 17 |

|    |      | 2.1.1 Low frequency loop (LF)                                 | 19 |

|    |      | 2.1.2 High frequency loop (HF)                                | 20 |

|    | 2.2  | The unbalanced DC link oscillation in 2SiC hybrid ANPC        | 27 |

| 3. | Hig  | gh Frequency Oscillation Damping                              | 39 |

|    | 3.1  | Skin-effect decoupling capacitor                              | 40 |

|    | 3.2  | Dual soft-ferrite cores                                       | 44 |

|    |      | 3.2.1 Magnetic field inside a linear magnetic material        | 44 |

|    |      | 3.2.2 B-H curves of non-linear magnetic materials             | 46 |

|    |      | 3.2.3 DC-bias superposition and saturable inductor            | 50 |

|    |      | 3.2.4 The ring ferrite core's differential inductance         | 50 |

|    |      | 3.2.5 Deep saturation core's inductance measurement           | 52 |

|    |      | 3.2.6 Core losses and the oscillation damping                 | 55 |

|    |      | 3.2.7 SiC MOSFET's clean switching with dual ferrite cores    | 56 |

|    |      | 3.2.8 Dual cores' behaviors at turn-off                       | 58 |

|    |      | 3.2.9 Dual cores' behaviors at turn-on                        | 63 |

|    |      | 3.2.10 Dual cores' behaviors at reverse-recovery              | 66 |

|    |      | 3.2.11 Dual cores' behaviors at low load current              | 69 |

|    |     | 3.2.12 Core selection                                                         | 69    |

|----|-----|-------------------------------------------------------------------------------|-------|

| 4. | Lov | w Frequency Oscillation Damping                                               | 72    |

|    | 4.1 | Low frequency oscillation                                                     | 72    |

|    | 4.2 | Compare conventional switching states and active cut-off switching states     | 73    |

|    | 4.3 | Active cut-off switching states transitions                                   | 75    |

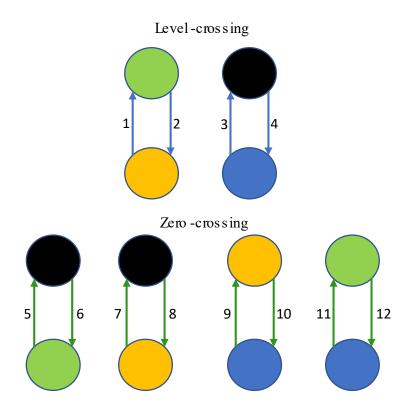

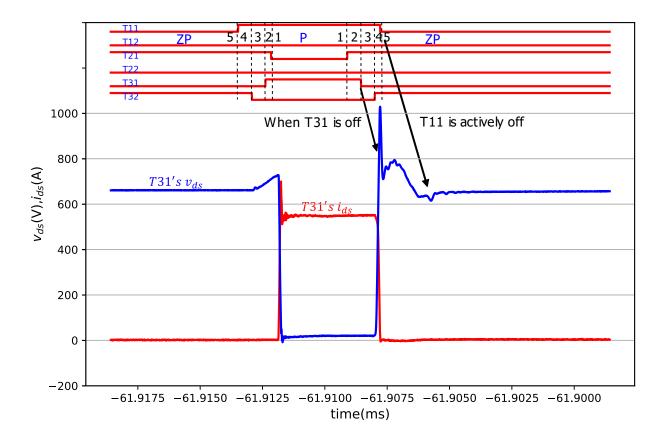

|    |     | 4.3.1 Level-crossing transitions                                              | 76    |

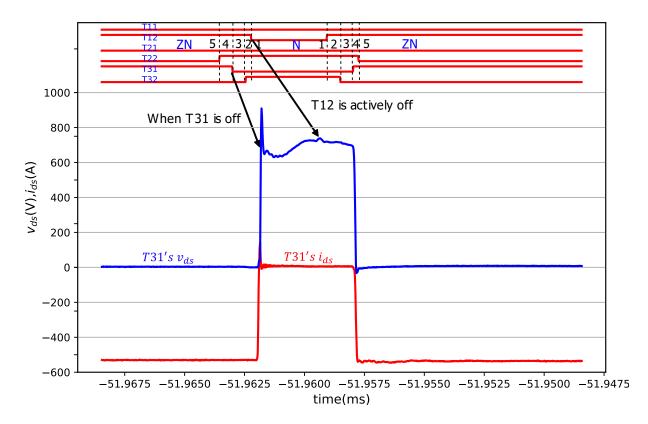

|    |     | 4.3.2 Zero-crossing transitions                                               | 80    |

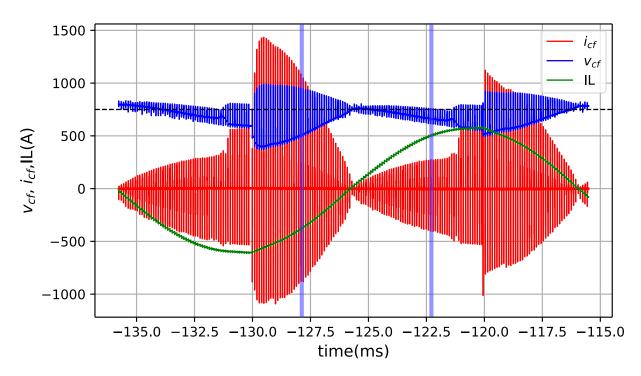

|    | 4.4 | Decoupling capacitor's behaviors during the active cut-off transitions        | 82    |

|    | 4.5 | Decoupling capacitor's voltage drifting                                       | 88    |

|    | 4.6 | Switching transitions time optimization.                                      | 89    |

|    |     | 4.6.1 Level-crossing transition time optimization.                            | 94    |

|    |     | 4.6.2 Zero-crossing transition time optimization                              | 95    |

|    |     | 4.6.3 IGBT's turn-off delay time optimization                                 | 96    |

| 5. | Tur | rn-on Losses Optimization and Overvoltage Protection                          | .100  |

|    | 5.1 | Parasitic turn-on in a half-bridge SiC MOSFET module                          | . 101 |

|    | 5.2 | Reverse-recovery of SiC MOSFET's body diode                                   | .103  |

|    | 5.3 | Reverse-recovery under parasitic turn-on effect                               | . 105 |

|    | 5.4 | Reverse-recovery overvoltage protection                                       | .107  |

|    |     | 5.4.1 Reverse-recovery overvoltage and oscillation modeling                   | . 107 |

|    |     | 5.4.2 Different cases of the reverse-recovery overvoltage                     | .117  |

|    |     | 5.4.3 Reverse-recovery overvoltage protection                                 | .118  |

|    | 5.5 | Turn-on losses optimization                                                   | .120  |

|    |     | 5.5.1 Optimization method                                                     | .121  |

|    |     | 5.5.2 The variation of threshold voltage and the turn-off voltage sensitivity | .127  |

|    | 5.6 | Compare total turn-on losses in different situations                          | .130  |

|    | 5.7 | Compare turn-off losses of different situations                               | . 131 |

| 6. | Dev | vices Characterization                                                        | .134  |

|    | 6.1 | SiC MOSFET module                                                             | .134  |

|    |     | 6.1.1 Double pulse test setup                                                 |       |

|       | 6.1.2 SiC MOSFET losses in nominal operating conditions               | 136          |

|-------|-----------------------------------------------------------------------|--------------|

|       | 6.1.3 Thermal coupling in the double pulse test                       | 137          |

| 6.2   | 2 IGBT module                                                         | 138          |

|       | 6.2.1 Double pulse test setup                                         | 138          |

|       | 6.2.2 IGBT turn-off characterization                                  | 139          |

|       | 6.2.3 IGBT turn-on characterization                                   | 143          |

| 6.3   | 3 Estimated devices' losses                                           | 146          |

| 6.4   | 4 Experimental Result                                                 | 150          |

|       | 6.4.1 Three phases current waveform                                   | 150          |

|       | 6.4.2 Continuous operation experiment                                 | 152          |

|       | 6.4.3 Thermal modeling                                                | 157          |

| 6.5   | 5 Compare 2SiC and 4SiC hybrid ANPC                                   | 161          |

| 7. Co | onclusion and Future Works                                            | 167          |

| 7.1   | l Conclusion                                                          | 167          |

| 7.2   | 2 Future works                                                        | 169          |

| 7.3   | 3 Publications                                                        | 170          |

| Appe  | endix 1 : Coupled LCR circuit theory                                  | 172          |

| A.    | 1.1 Different types of LCR oscillator                                 | 172          |

|       | A.1.1.1 Basic LC oscillator                                           | 172          |

|       | A.1.1.2 LC oscillator with DC voltage source                          | 175          |

|       | A.1.1.3 LCR oscillator.                                               | 176          |

| A.    | 1.2 Decoupling of two coupled LCR networks                            | 177          |

| A.    | 1.3 Superposition of AC circuit theorem                               | 179          |

| A.    | 1.4 Verification of the coupled LCR oscillator model with SIMetrix si | mulation.181 |

| A.    | 1.5 Oscillation trigger mechanisms                                    | 184          |

|       | A.1.5.1 Voltage slope at the output                                   | 185          |

|       | A.1.5.2 Current slope at the input                                    | 186          |

| A.    | 1.6 Stray inductance decoupling condition                             | 188          |

| Anne  | endix 2 : 2SiC Hybrid ANPC Hardware and Software Design               | 190          |

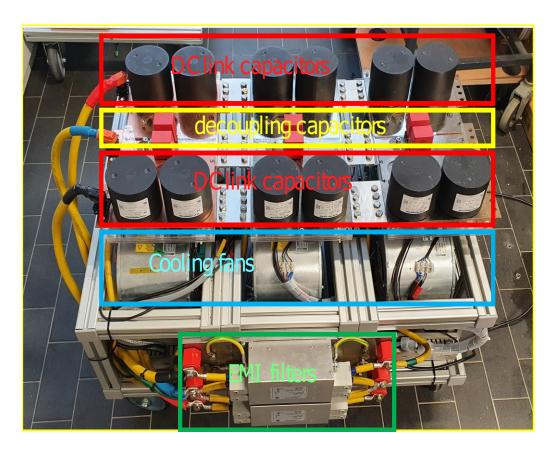

|    | A.2.1 DC link capacitor selection                        | 190      |

|----|----------------------------------------------------------|----------|

|    | A.2.2 Power switches selection                           | 192      |

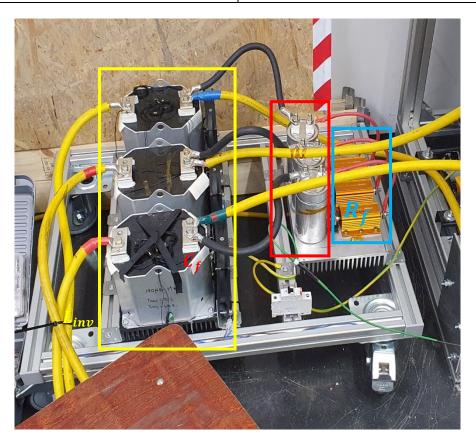

|    | A.2.3 Inverter layout                                    | 192      |

|    | A.2.4 Busbar design.                                     | 193      |

|    | A.2.5 Decoupling capacitor selection                     | 195      |

|    | A.2.6 Ferrite cores selection                            | 200      |

|    | A.2.7 SiC MOSFET Gate driver design                      | 201      |

|    | A.2.7.1 Advanced active clamping circuit                 | 202      |

|    | A.2.7.2 Gate driver isolated power supply                | 205      |

|    | A.2.8 Inverter controller unit                           | 207      |

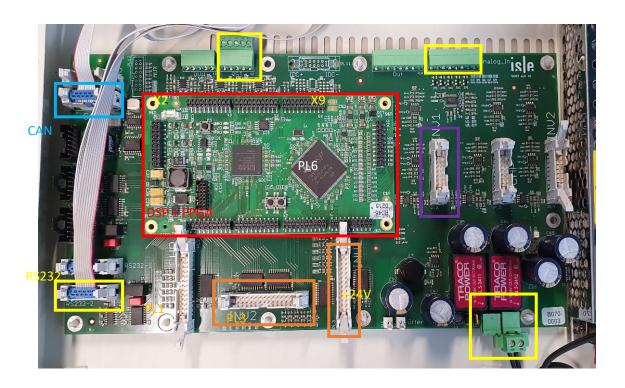

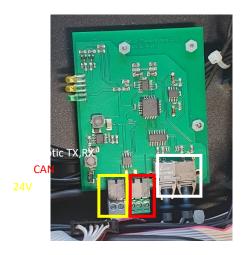

|    | A.2.8.1 Controller board                                 | 208      |

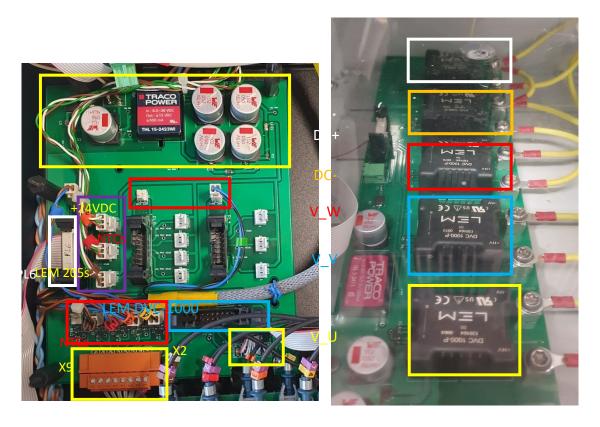

|    | A.2.8.2 Analog board                                     | 208      |

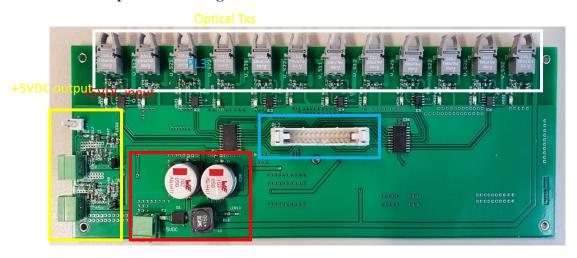

|    | A.2.8.3 Optical switching board                          | 209      |

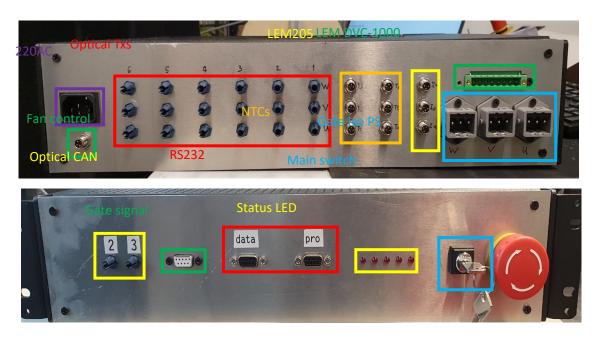

|    | A.2.8.4 Controller panel assembly                        | 210      |

|    | A.2.9 LC filter design                                   | 211      |

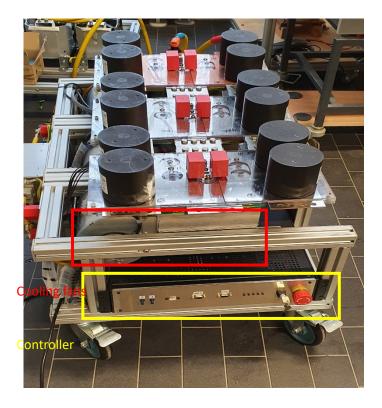

|    | A.2.10 Inverter assembly                                 | 212      |

|    | A.2.11 Software design                                   | 214      |

|    | A.2.11.1 FPGA                                            | 214      |

|    | A.2.11.2 PWM generator                                   | 214      |

|    | A.2.11.3 Active cut-off switching scheme's state machine | 216      |

|    | A.2.12 State machine VDHL code                           | 217      |

| _  |                                                          | <b>.</b> |

| 8. | Reference                                                | 226      |

# **List of Acronyms**

3L-ANPC: Three-level active neutral point clamped

3L-TDANPC: Three-level two-stage decoupled active neutral point clamped

AC: Alternating current

ACL: Active clamping

ADC: Analog-to-digital converter

AGD: Active gate driver

AISI: American Iron and Steel Institute

BW: Band width

CAN: Controller area network

DC: Direct current

DSP: Digital signal processor

EMI: Electromagnetic interference

EMC: Electromagnetic compatibility

EN: European Standard

ESL: Equivalent series inductance

ESR: Equivalent series resistance

FR: Ferrite core

FPGA: Field programmable gate arrays

HF: High frequency

IGBT: Insulated-gate bipolar transistor

LF: Low frequency

MOSFET: Metal oxide semiconductor field effect transistor

PCB: Printed circuit board

PTO: Parasitic turn-on

PWM: Pulse width modulation

RMS: Root mean square

Si: Silicon

SiC: Silicon Carbide

SOA: Safe operating area

THD: Total harmonic distortion

TIM: Thermal interface material

TVS: Transient voltage suppressor

WIFI: Wireless fidelity

# **List of Figures**

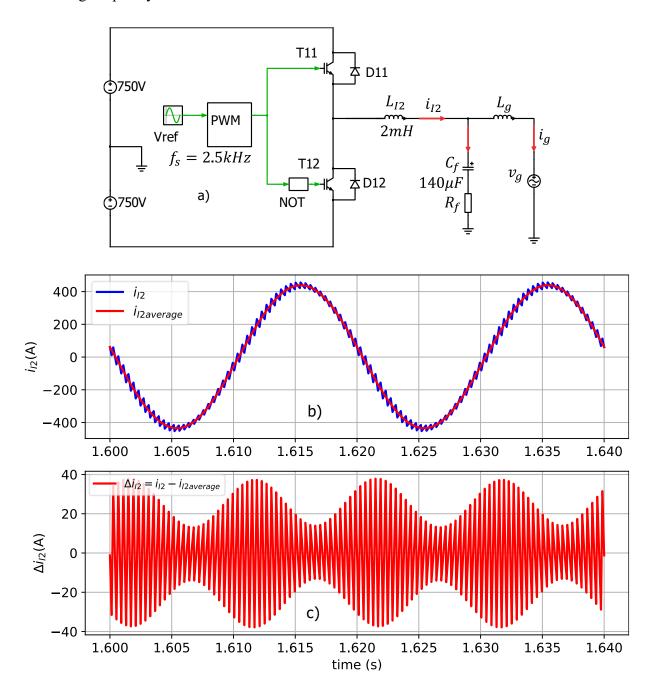

| <b>Figure 1.1:</b> PLECS simulation: a) 2-level inverter fs = 2.5kHz, b) Output current before the LO                        |

|------------------------------------------------------------------------------------------------------------------------------|

| filter and its average value, c) peak to peak current ripple                                                                 |

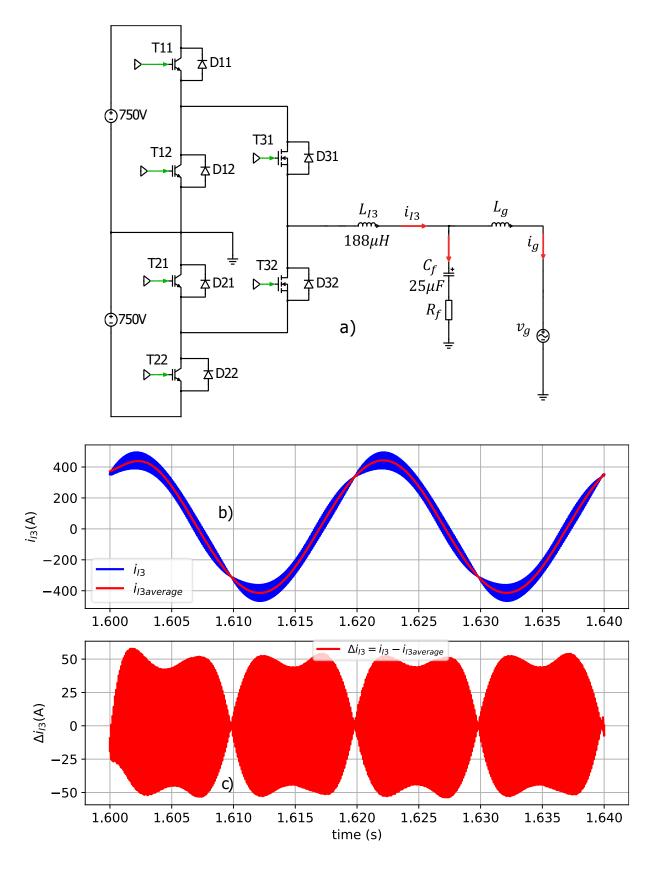

| <b>Figure 1.2:</b> PLECS simulation: a) 3-level inverter fs= 10kHz, b) Output current before the LO                          |

| filter and its average value, c) peak to peak current ripple                                                                 |

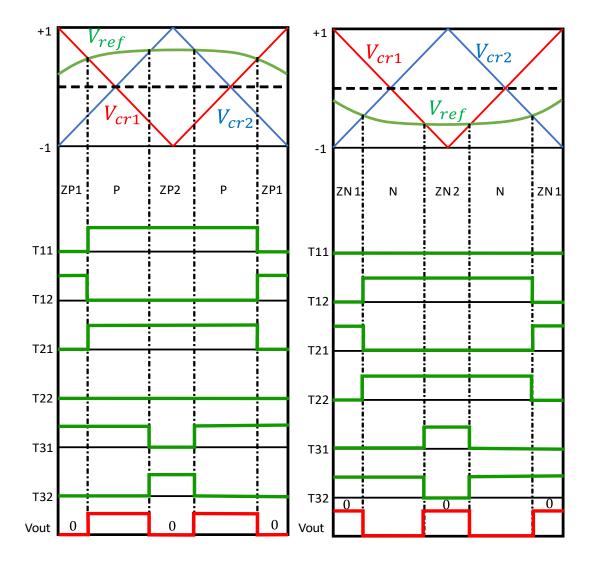

| <b>Figure 1.3:</b> PWM-3 switching pattern. $V_{out}$ has apparently double the switching frequency [14]                     |

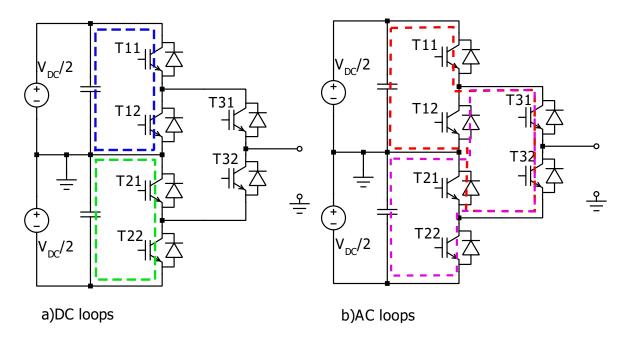

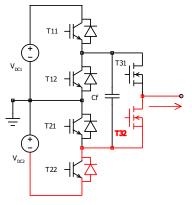

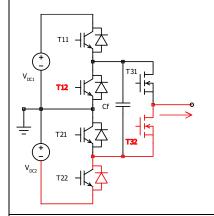

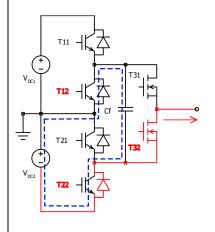

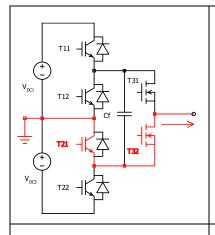

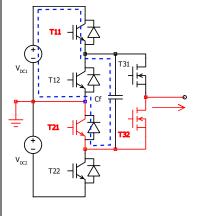

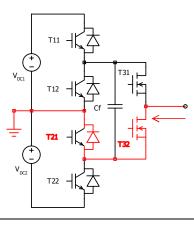

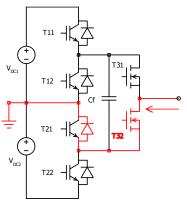

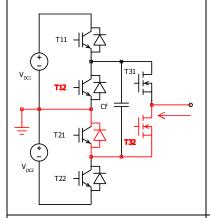

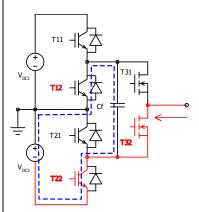

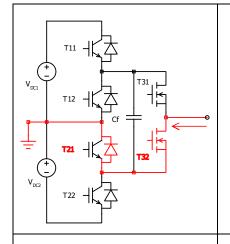

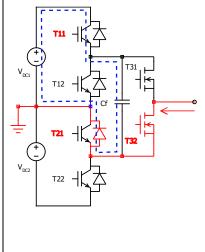

| Figure 1.4: 3-Level Active neutral point clamped (ANPC) topology and its commutation loops                                   |

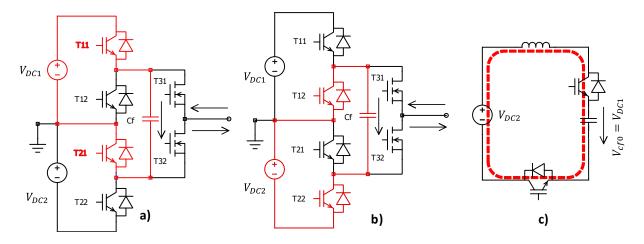

| a) T11, T12, T21, T22's commutation loops: dashed blue, green lines. b) T31, T32's commutation loops: red, pink dashed lines |

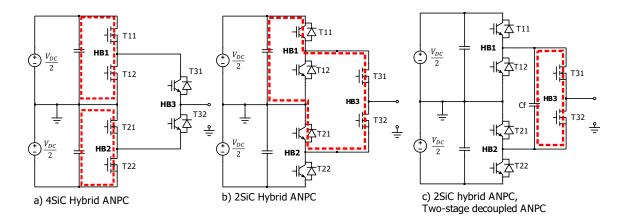

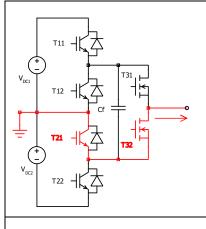

| Figure 1.5: Hybrid ANPC topology, a) 4SiC-Hybrid ANPC [15], b) 2SiC-Hybrid ANPC [21], c                                      |

| Two-stage decoupled ANPC (3L-TDANPC) [26]1                                                                                   |

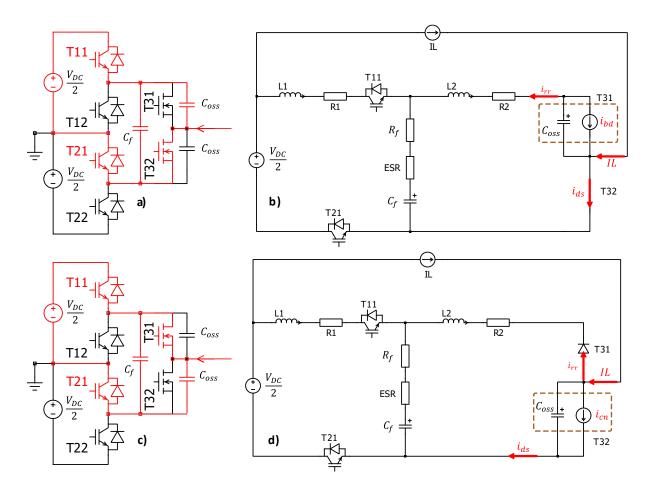

| Figure 1.6: 2SiC hybrid ANPC with decoupling capacitor a) when T32 is on, c) when T32 is of                                  |

| b, d) The equivalent circuit of those 2 cases1                                                                               |

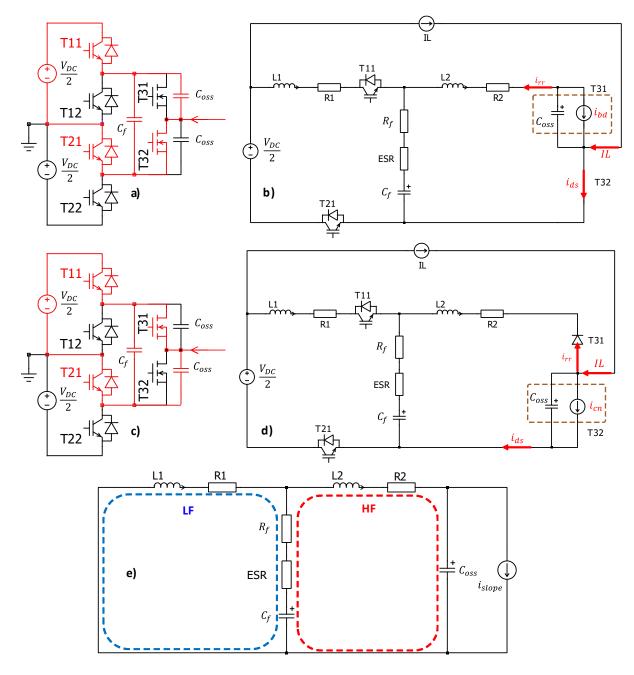

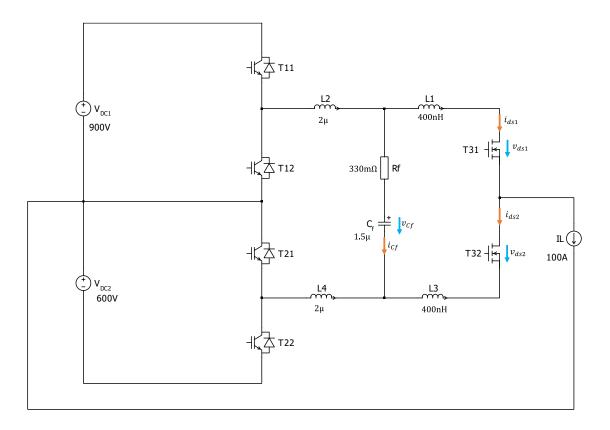

| Figure 2.1: Oscillation circuits in ANPC when a) T32 is turned on, b) Equivalent circuit when                                |

| T31's body diode is in its reverse-recovery, c) T32 is turned off, d) Equivalent circuit during                              |

| T32's turn-off e) The small AC signal equivalent circuit during T32's turn-on and turn-og                                    |

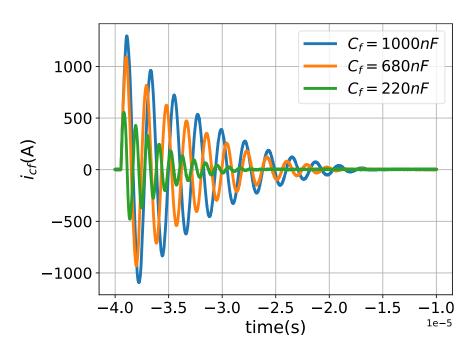

| <b>Figure 2.2:</b> Different capacitor charging current at start-up of the ANPC at 1000 $V_{DC}$ , Cf =                      |

| 1000nF,680nF and 220nF                                                                                                       |

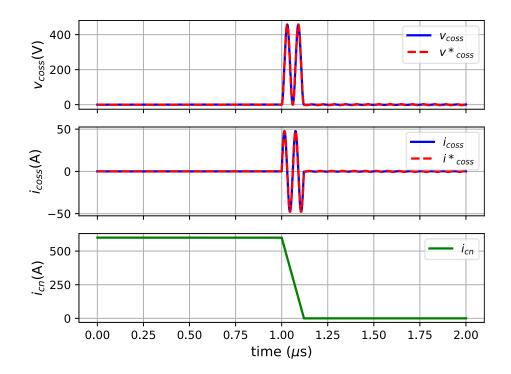

| Figure 2.3: The small signal circuit of the high frequency oscillation circuit (HF) during                                   |

| MOSFET's turn-off current transient2                                                                                         |

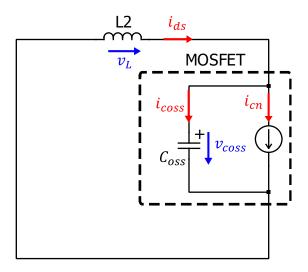

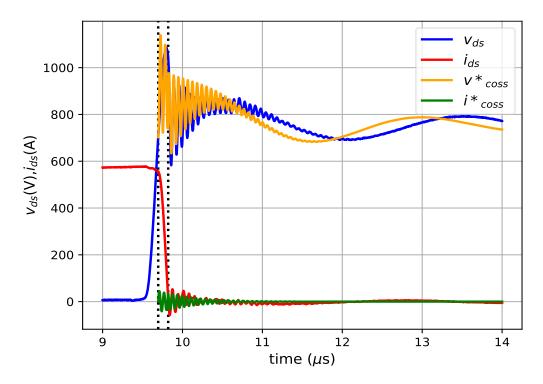

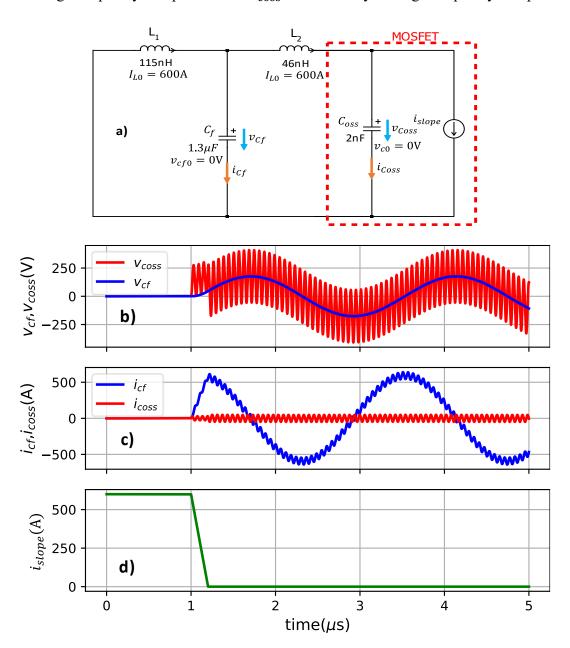

| <b>Figure 2.4:</b> <i>PLECS simulation model of the HF loop triggered by current slope at input.</i> 2.                      |

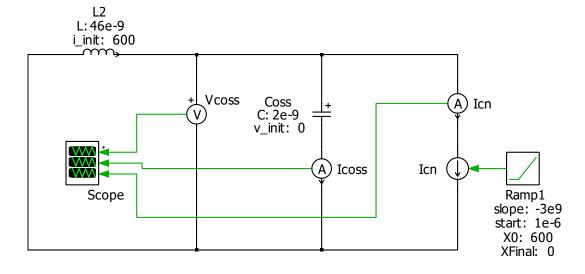

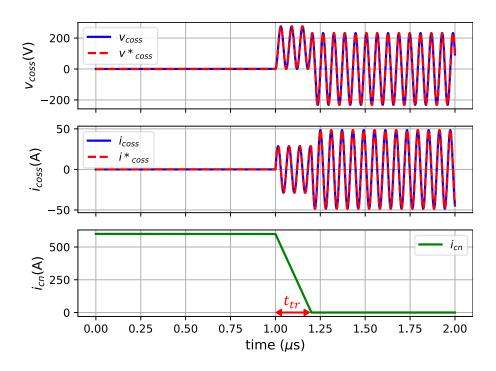

| Figure 2.5: Compare voltage and current waveforms in PLECS simulation (blue solid lines) and                                 |

| analytical model (red dashed line). $ttr = 200 \text{ ns}, a = -3 \text{ A/ns}$                                              |

| <b>Figure 2.6:</b> The steady state oscillation is canceled with proper selection of current slope. $n = -\frac{1}{2}$                |

|---------------------------------------------------------------------------------------------------------------------------------------|

| ttr = 120.4 ns, a = -4.98 A/ns                                                                                                        |

| Figure 2.7: Compare experimental turn-off voltage and current waveforms of a SiC MOSFET is                                            |

| the two-stage decouple ANPC (blue and red lines) with the proposed analytical mode                                                    |

| (orange and green lines)2                                                                                                             |

| <b>Figure 2.8:</b> The unbalanced DC link oscillation in 2SiC hybrid ANPC, a) Cf is charged to $V_{DC}$                               |

| b) ANPC is switched to lower side DC link, c) The equivalent circuit when the ANPC                                                    |

| switched to $V_{DC2}$ with the initial capacitor voltage $V_{DC1}$                                                                    |

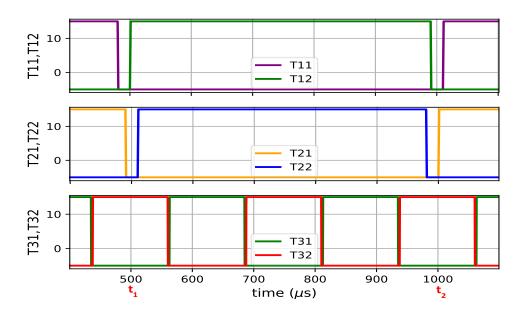

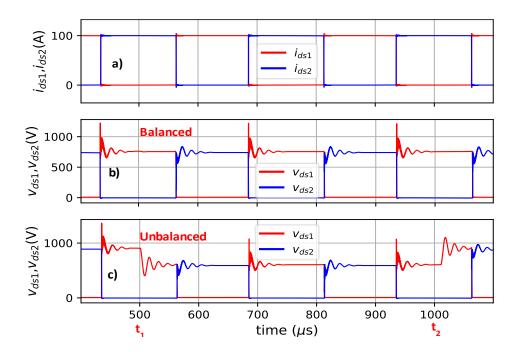

| <b>Figure 2.9:</b> SIMetrix simulation of the unbalanced DClink oscillation in 2SiC hybrid ANPC 2                                     |

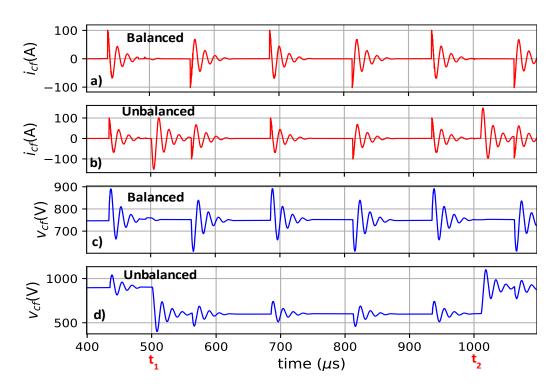

| <b>Figure 2.10:</b> Gate control signals of the SIMetrix simulation. $t_1$ , $t_2$ are zero-crossing transition                       |

| <b>Figure 2.11:</b> SiC MOSFET's voltages and currents when there is balanced and unbalanced D link voltage                           |

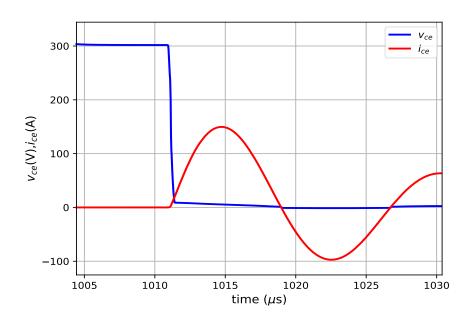

| Figure 2.12: Decoupling capacitor's voltage and current when there is balanced and unbalance  DC link voltage                         |

| Figure 2.13: Voltage and current across T11 during the zero-crossing transition under unbalanced DC link voltage. (Simulation result) |

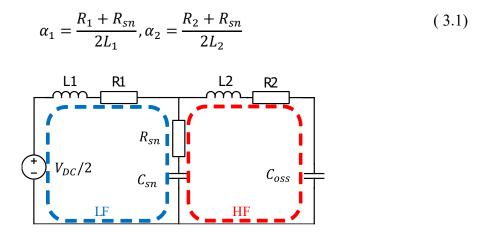

| Figure 3.1: 2SiC Hybrid ANPC oscillator equivalent circuit with RC snubber                                                            |

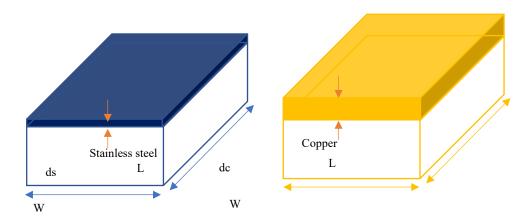

| <b>Figure 3.2:</b> The skin-effect decoupling capacitor a) conduction cooled capacitor b) stainless steed plates                      |

| Figure 3.3: The skin effect of different conduct material                                                                             |

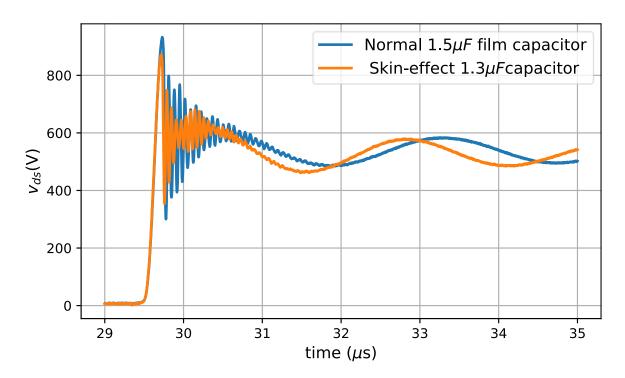

| Figure 3.4: The experimental result of the turn-off voltage across SiC MOSFET using normal                                            |

| 1500nF film capacitor and 1300nF special capacitor with stainless steel plates                                                        |

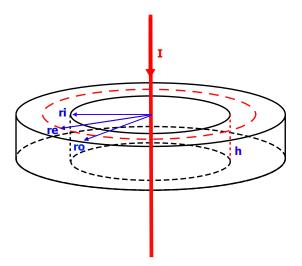

| Figure 3.5: The toroidal ferrite core is excited with current I                                                                       |

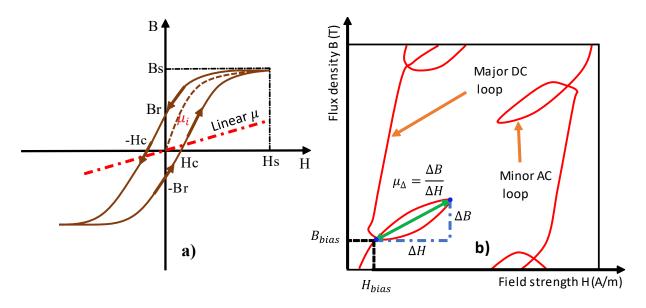

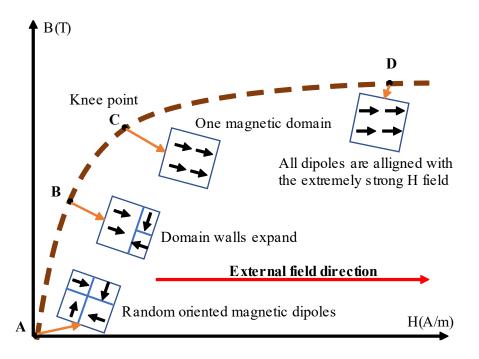

| Figure 3.6: B-H curves of none-linear magnetic material: a) Major DC loop when the material                          | al  |

|----------------------------------------------------------------------------------------------------------------------|-----|

| is under slow and large signal field strength, b) Major DC loop superposition with the sma                           | ıll |

| signal minor AC loops. The incremental permeability of the minor loop $\mu\Delta$ is the slope of                    | 9f  |

| the minor loop at Hbias, Bbias4                                                                                      | 6   |

| Figure 3.7: Magnetic domains' behaviors along the one branch of the B-H curves, black arrow                          | VS  |

| are the domain's magnetic dipoles, magnetic domains are presented with the rectangles.4                              | 17  |

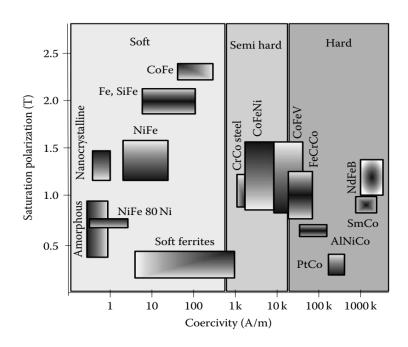

| <b>Figure 3.8:</b> Different type of non-linear magnetic material based on Coercivity [72]                           | 8   |

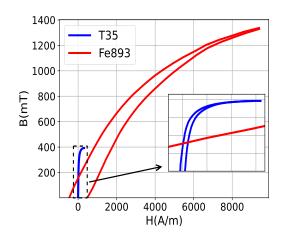

| <b>Figure 3.9:</b> B-H curves of soft ferrite MnZn T35 [73] and iron powder Fe893 [74]                               | 9   |

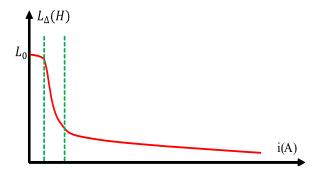

| <b>Figure 3.10:</b> Differential inductance of the ferrite core in different regions of the excitation current [99]. |     |

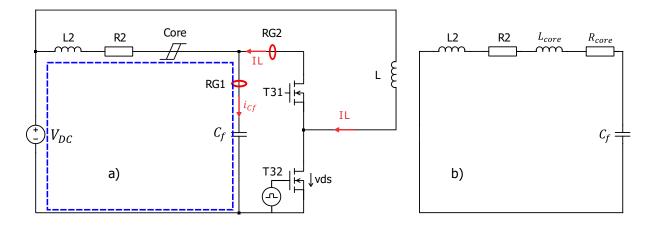

| Figure 3.11: Single pulse test setup to measure the differential inductance of the ferrite con                       | re  |

| under DC bias excitation current. a) schematic of the test setup, blue dashed line is the                            | ıe  |

| resonance circuit. b) the equivalent circuit of the resonant circuit5                                                | 3   |

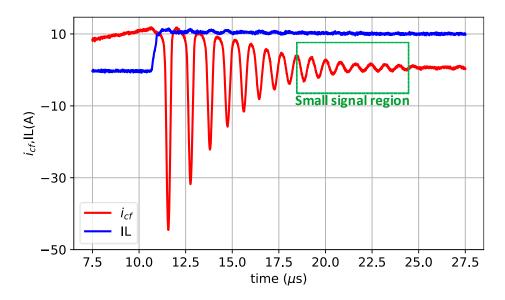

| Figure 3.12: Capacitor's current (red line) and load current (blue line) waveform during sing pulse test.            |     |

|                                                                                                                      |     |

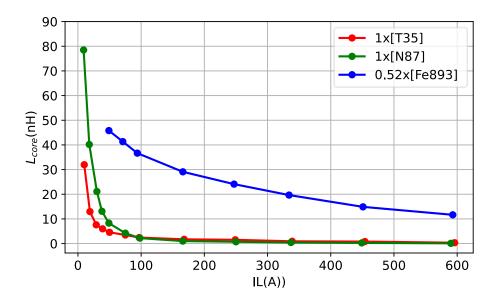

| <b>Figure 3.13:</b> The differential inductance of different magnetic core measured at 25°C in roll-o                |     |

| and deep saturation region5                                                                                          | 5   |

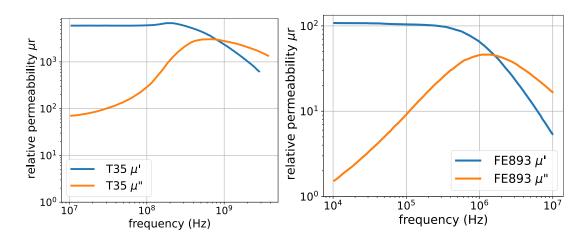

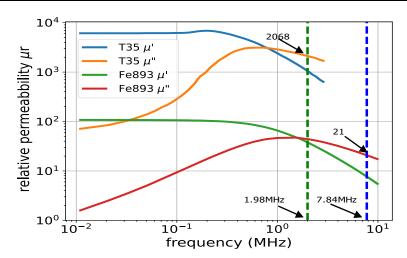

| Figure 3.14: The relative permeability of different magnetic material: soft-ferrite T35 [73], Iron                   | n   |

| powder Fe893[74]5                                                                                                    | 6   |

| Figure 3.15: Simplified equivalent circuit of ferrite core in high frequency range                                   | 6   |

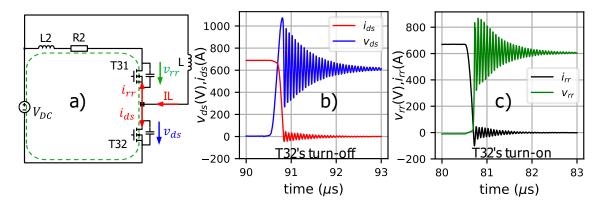

| Figure 3.16: Double pulse test setup: a) without ferrite core, b) T32 is turned off, voltage and                     | ıd  |

| current of T32. c)T32 is turned on, voltage and current of T315                                                      | 7   |

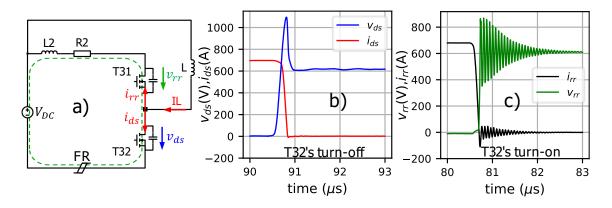

| <b>Figure 3.17:</b> Double pulse test setup: a) with ferrite core FR at -DC terminal, b) T32 is turned               | ≀d  |

| off, voltage and current of T32. c)T32 is turned on, voltage and current of T315                                     | 7   |

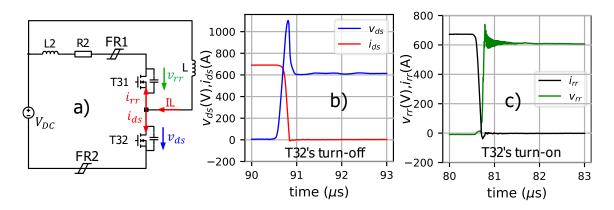

| Figure 3.18: Double pulse test setup: a) with dual ferrite cores FR1, FR2, b) T32 is turned of                  |

|-----------------------------------------------------------------------------------------------------------------|

| voltage and current of T32. c)T32 is turned on, voltage and current of T315                                     |

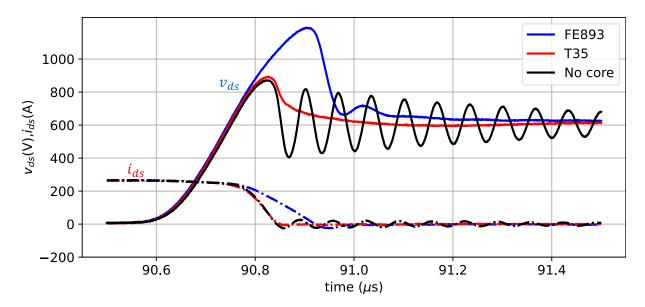

| Figure 3.19: Voltage and current waveform of the lower MOSFET T32 during its turn-off with                      |

| FE893 core (blue lines), T35 core (red lines), and no core (black lines). Solid lines are                       |

| voltages, dashed lines are currents. $V_{DC}=600V$ , $IL=250A$ , $T_{j}=25^{\circ}C$ , $R_{goff}=18\Omega$ 5    |

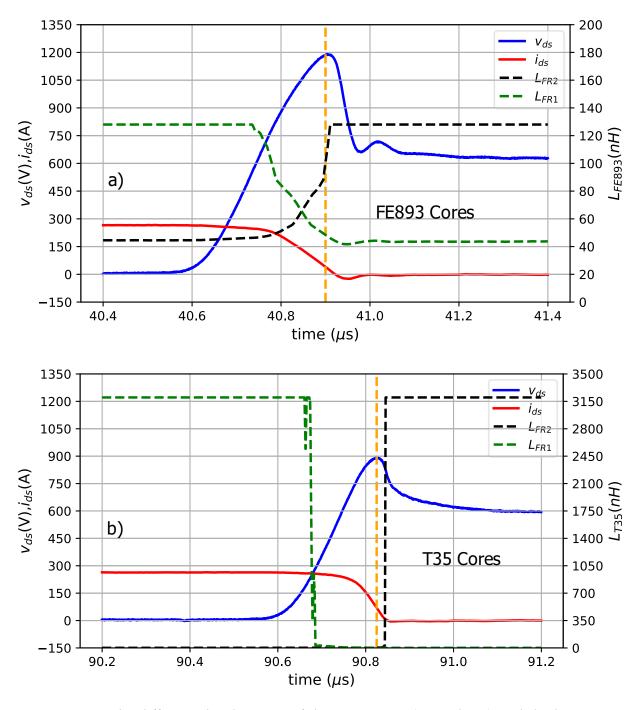

| Figure 3.20: The differential inductance of the upper core (green lines) and the lower core (black)             |

| lines) during turn-off. a) iron powder core Fe893. b) soft-ferrite T35. $V_{DC}=600V,\ IL=0.000$                |

| 250A, $T_j = 25$ °C, $R_{goff} = 18\Omega$ 6                                                                    |

| Figure 3.21: The complex permeability of T35 material and iron powder Fe893 at the turn-o                       |

| oscillation frequencies [73,74]6                                                                                |

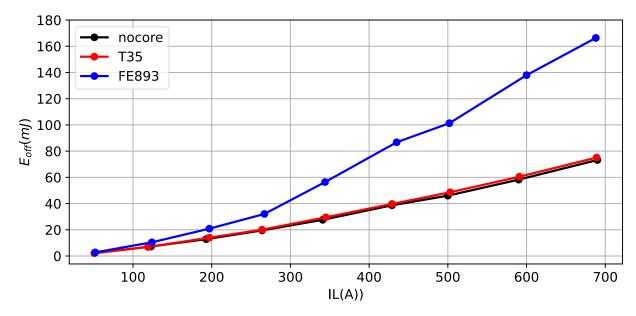

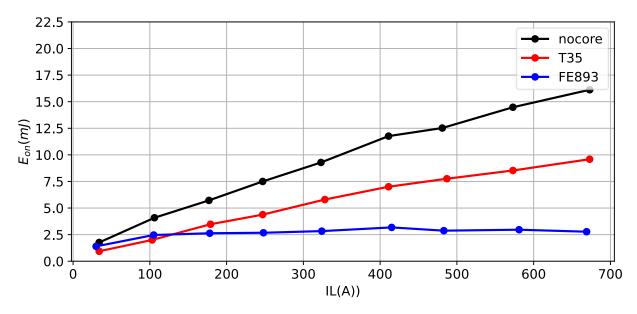

| <b>Figure 3.22:</b> Turn-off losses on SiC MOSFET T32 in three experiment cases. $V_{DC} = 600V$ , $T_j = 600V$ |

| $25$ °C, $R_{goff} = 18\Omega$ 6                                                                                |

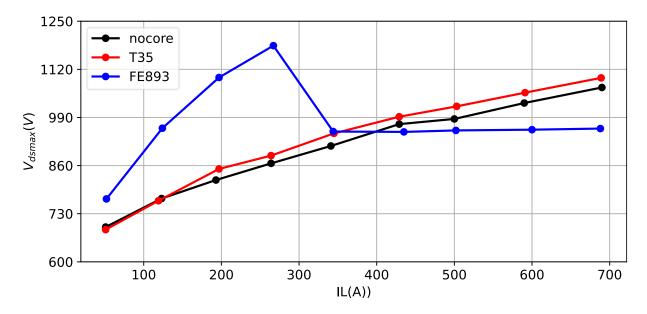

| Figure 3.23: Turn-off overvoltages on SiC MOSFET T32 in three experiment cases. The activ                       |

| clamping is implemented to protect the SiC MOSFET from high overvoltage when IL> $270$ .                        |

| only for FE893 cases. $V_{DC} = 600V$ , $T_j = 25$ °C, $R_{goff} = 18\Omega$                                    |

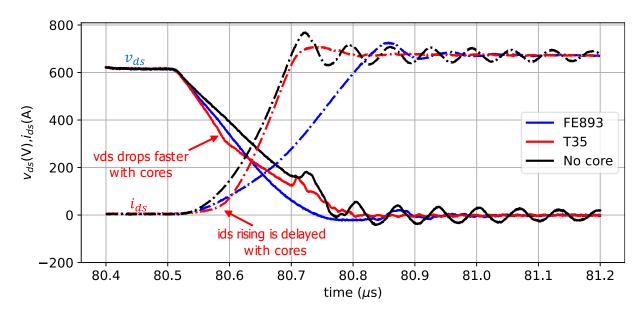

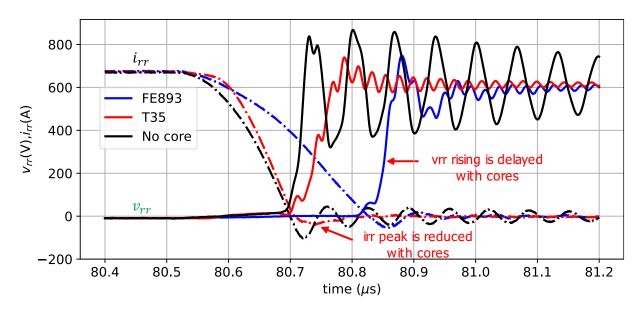

| Figure 3.24: Voltage and current waveform of the lower MOSFET T32 during its turn-on with                       |

| FE893 core (blue lines), T35 core (red lines), and no core (black lines). Solid lines are                       |

| voltages, dashed lines are currents. $V_{DC}=600V$ , $IL=660A$ , $T_j=25$ °C, $R_{gon}=5\Omega$ 6               |

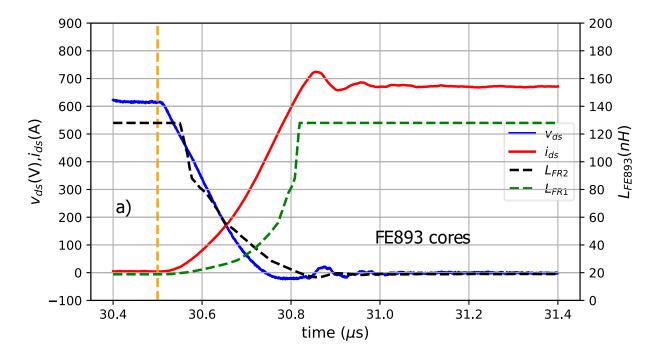

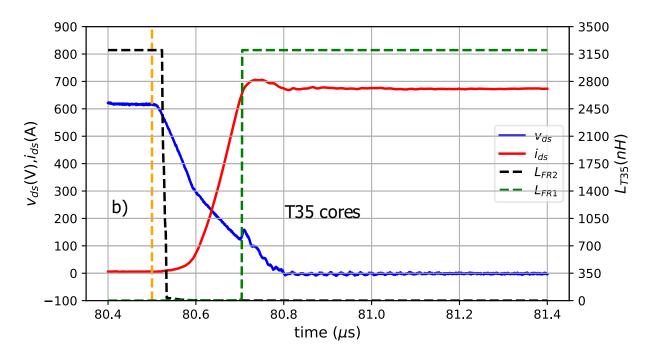

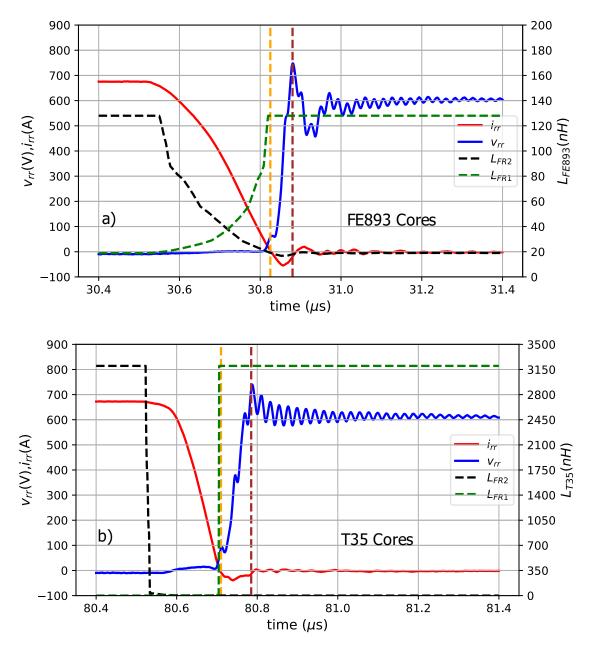

| Figure 3.25: The differential inductance of the upper and lower core during turn-on. a) iro                     |

| powder core Fe893. b) soft-ferrite MnZn T35. The orange dashed line marks the time v                            |

| starts dropping6                                                                                                |

| <b>Figure 3.26:</b> Turn-on losses on SiC MOSFET T32 in three experiment cases. $V_{DC} = 600V$ , $T_j = 600V$  |

| $25$ °C, $R_{gon} = 5\Omega$ 6                                                                                  |

| Figure 3.27: Voltage and current waveforms of the upper MOSFET during its body diode                            |

| reverse recovery with FE893 core (blue lines), T35 core (red lines), and no core (blac                          |

| lines). Solid lines are voltages, dashed lines are currents. $V_{DC} = 600V$ , $IL = 660A$ , $T_j = 600V$       |

| $25^{\circ}C R_{con} = 50$                                                                                      |

| Figure 3.28: The differential inductance of the upper and lower core during turn-on. a) is                    |  |

|---------------------------------------------------------------------------------------------------------------|--|

| powder core Fe893. b) soft-ferrite MnZn T35. The orange dashed lines mark the time th                         |  |

| reverse-recovery starts, the brown dashed lines mark the reverse-recovery current slope                       |  |

|                                                                                                               |  |

|                                                                                                               |  |

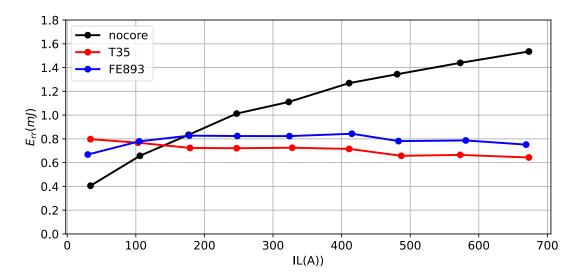

| Figure 3.29: Reverse-recovery losses on T31's body diode in three experiment cases. $V_{DC}$                  |  |

| 600V, $T_j = 25$ °C, $R_{gon} = 5\Omega$                                                                      |  |

| <b>Figure 3.30:</b> Reverse-recovery overvoltage on T31's body diode in three experiment cases. $V_L$         |  |

| $= 600V, T_j = 25$ °C, $R_{gon} = 5\Omega$                                                                    |  |

| <b>Figure 3.31:</b> Turn-off voltage and current waveform at IL = 50A and IL = 700A, T35 dual core            |  |

| Figure 4.1: Low frequency oscillation circuit in 2SiC hybrid ANPC. A) the LF circuit (gree                    |  |

| dashed line) when the ANPC is in its state P and ZP. B) the simplified equivalent L                           |  |

| oscillation circuit7                                                                                          |  |

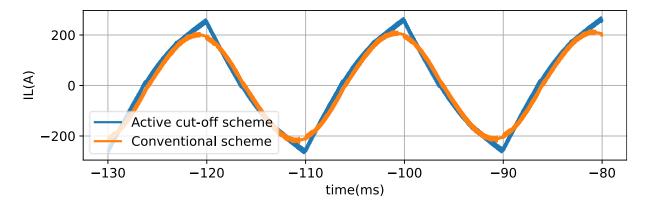

| Figure 4.2: Low frequency oscillation with the conventional switching states (orange line) and                |  |

| the active cut-off switching states (blue line) when the ANPC changes from P to dead time                     |  |

| and dead time to ZP7                                                                                          |  |

| Figure 4.3: Four switching states of hybrid 2SiC ANPC N, P, ZN, ZP and their 12 potential                     |  |

| transitions. The transitions can be divided to level-crossing and zero-crossing groups 7                      |  |

| <b>Figure 4.4:</b> <i>T31's voltage (blue line) and current (red line) waveforms during the level-crossin</i> |  |

| transitions 1 and 2 between P and ZP when the $IL > 0$                                                        |  |

| <b>Figure 4.5:</b> <i>T31's voltage (blue line) and current (red line) waveform during the level-crossin</i>  |  |

| transitions 3 and 4 between N and ZN when the $IL < 0$ .                                                      |  |

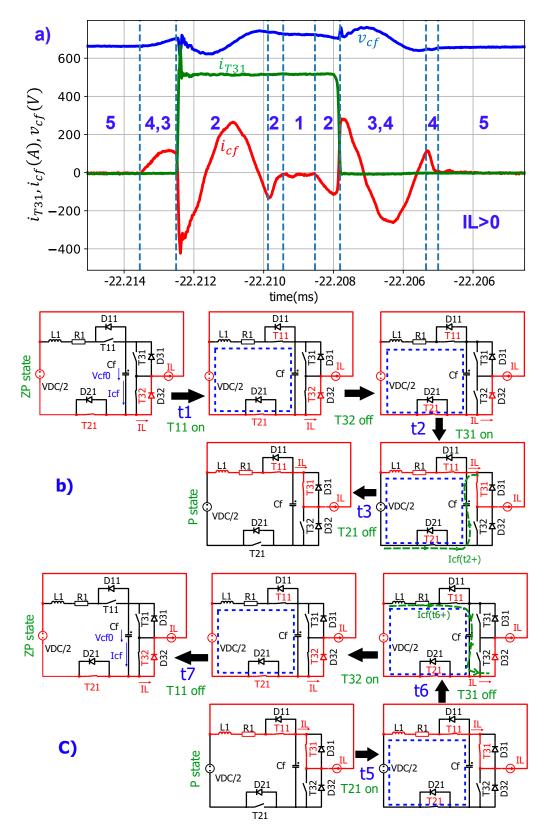

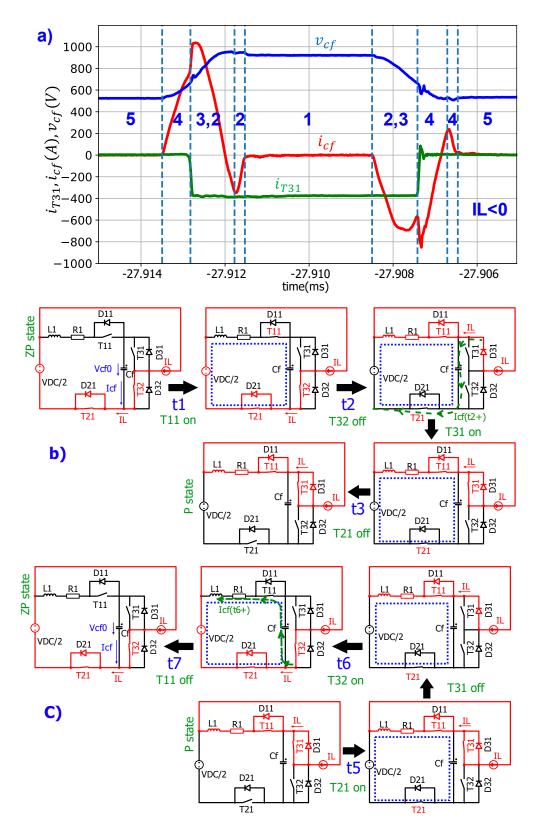

| Figure 46. Decoupling agreeiton's voltage (blue line) and appear (and line) during a                          |  |

| <b>Figure 4.6:</b> Decoupling capacitor's voltage (blue line) and current (red line) during on                |  |

| fundamental cycle of the load current (green line)8                                                           |  |

| Figure 4.7: Measurement result: Decoupling capacitor's voltage (blue lines) and current (red             |

|----------------------------------------------------------------------------------------------------------|

| lines) during level-crossing transition between P and ZP states when the load current IL >               |

| 085                                                                                                      |

| Figure 4.8: Measurement result: Decoupling capacitor's voltage (blue lines) and current (red             |

| lines) during level-crossing transition between $P$ and $ZP$ states when the load current $IL$ <         |

| 086                                                                                                      |

| <b>Figure 4.9:</b> Reverse-recovery process of D21 during $t_3$ and $t_4$                                |

| <b>Figure 4.10:</b> PLECS simulation to verify the transition behavior from step 4 to step 2. Diodes are |

| PLECS's library model with reverse-recovery effect87                                                     |

| Figure 4.11: Drifting voltage of the decoupling capacitor and the switching losses on IGBT. a            |

| during the level crossing transition P, ZP, $vT11 = VDC2-vcf$ . b) when $IL > 0$ , c) when $IL > 0$      |

| < 0                                                                                                      |

| Figure 4.12: The smallest turn-on and turn-off time during the switching at very small modulation        |

| index90                                                                                                  |

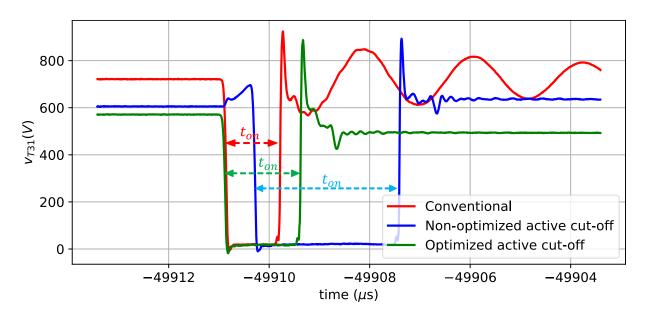

| Figure 4.13: Compare the shortest available ton time between the conventional switching                  |

| scheme (dashed red arrow) and the active cut-off (dashed blue arrow). The voltage acros.                 |

| T31 during P, ZP transitions at $IL = 450A$ 90                                                           |

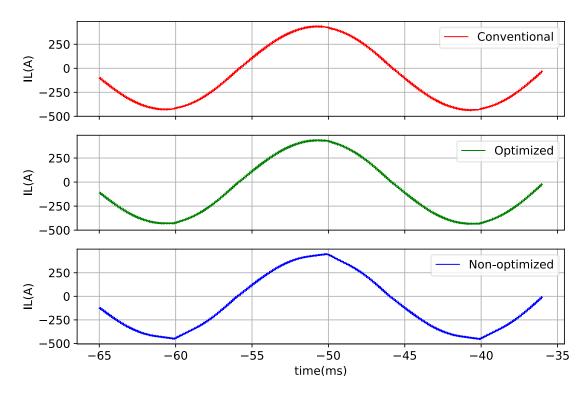

| Figure 4.14: Load current waveform at the same modulation index = $0.03$ when using                      |

| conventional and active cut-off switching scheme90                                                       |

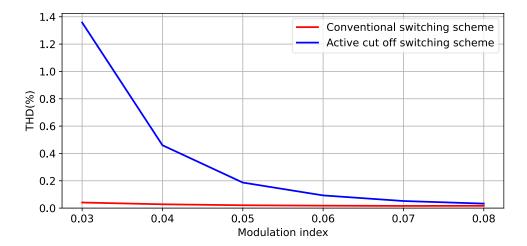

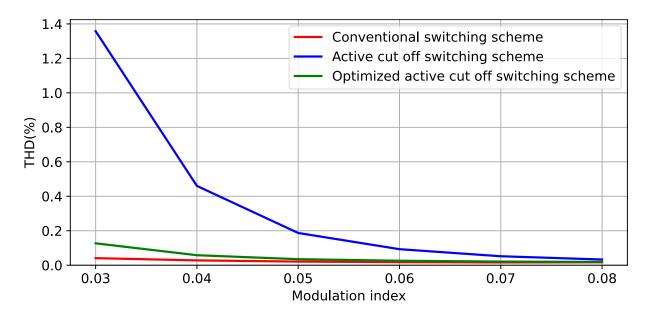

| Figure 4.15: Compare THD of load current over modulation index from conventional and active              |

| cut-off switching scheme9                                                                                |

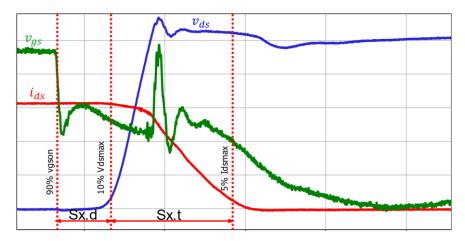

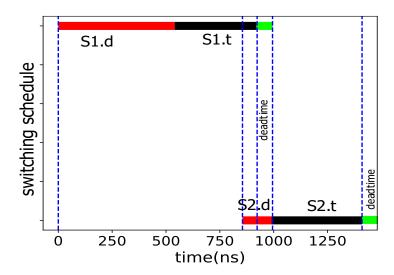

| Figure 4.16: Turn-off's delay phase (Sx.d): from 90% $V_{gson}$ to 10% of the maximum of the             |

| operating voltage and the turn-off's transition phase (Sx.t): from 10% of the maximum o                  |

| the operating voltage to 5% of the maximum of the operating current92                                    |

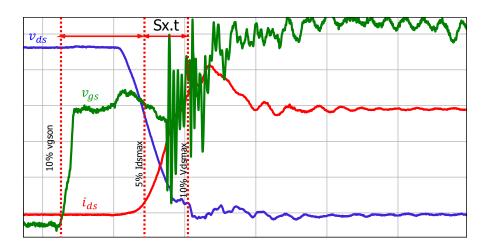

| Figure 4.17: Turn-on's delay phase (Sx.d): from the 10% $V_{gson}$ to 10% of the maximum of the                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| operating current and the turn-on's transition phase (Sx.t): from 5% of the maximum of the                                                                     |

| operating current to $10\%$ of the maximum of the operating voltage92                                                                                          |

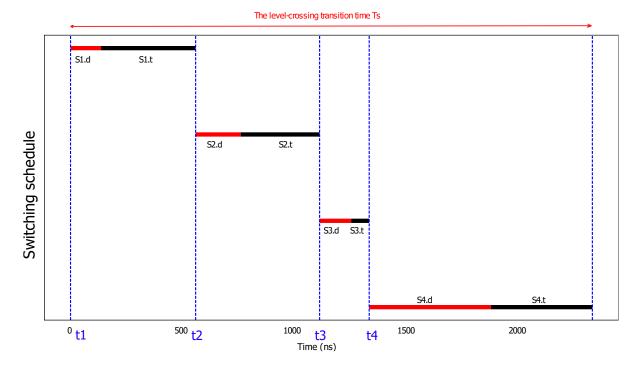

| Figure 4.18: Non-optimal switching schedule of the level-crossing transition. The red line is the                                                              |

| delay phase (Sx.d) and the black line is the transient phase (Sx.t). t <sub>1</sub> , t <sub>2</sub> , t <sub>3</sub> , t <sub>4</sub> are the trigger events. |

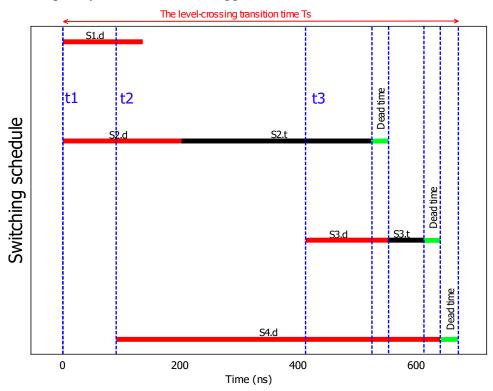

| Figure 4.19: Optimal switching schedule of the level-crossing transition                                                                                       |

| <b>Figure 4.20:</b> Optimal zero-crossing transition 7, 8, 11, 12 switching schedules. The red lines are                                                       |

| the delay phase and the black lines are the transient phase, the green lines are the deadtime.                                                                 |

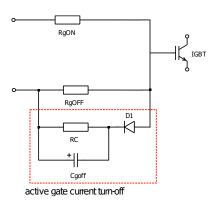

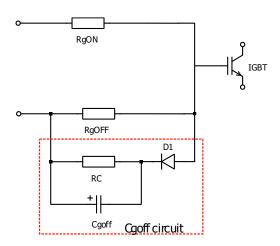

| <b>Figure 4.21:</b> $C_{goff}$ circuit can flash out the IGBT's gate charges faster                                                                            |

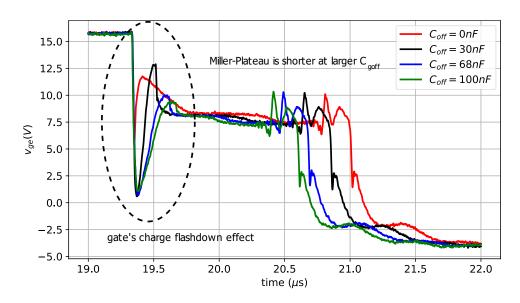

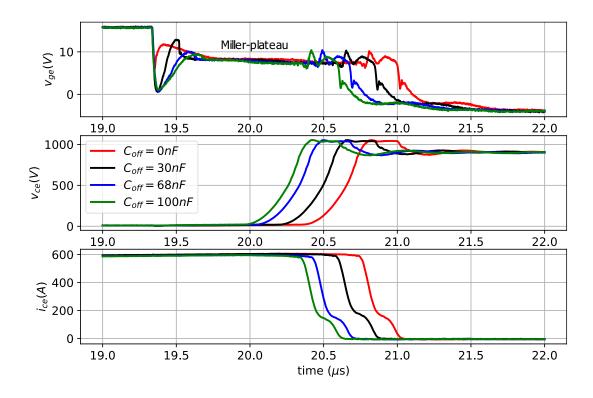

| <b>Figure 4.22:</b> Turn-off gate voltage with different $C_{goff}$ value. The higher $C_{goff}$ is the shorter Miller-                                        |

| Plateau becomes97                                                                                                                                              |

| Figure 4.23: Compare the smallest ton time at the peak of the load current between the                                                                         |

| conventional switching scheme (dashed red arrow), the non-optimized active cut-off (dashed                                                                     |

| blue arrow) and the optimized active cut-off (dashed green arrow). The voltage across T31                                                                      |

| during the P, ZP transitions at $IL = 450A$                                                                                                                    |

| Figure 4.24: Level-crossing transition time optimization leads to lower load current THD at low                                                                |

| modulation index98                                                                                                                                             |

| Figure 4.25: Load current waveform with different switching schemes: Conventional (red line),                                                                  |

| optimized active cut-off (green line) and non-optimized active cut-off (blue line) 99                                                                          |

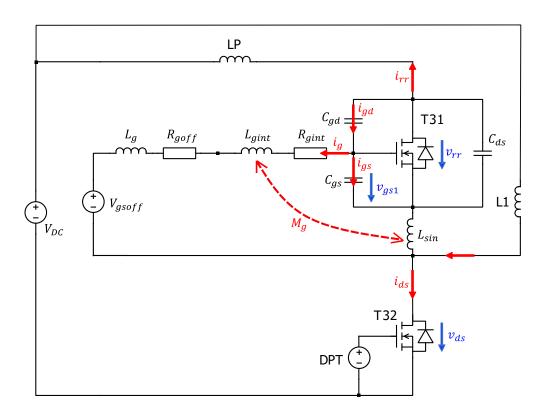

| Figure 5.1: SiC MOSFET half-bridge double pule test set-up with detail T31 parasitic elements                                                                  |

| and magnetic coupling Mg between T31's gate circuit network and didsdt of T32 101                                                                              |

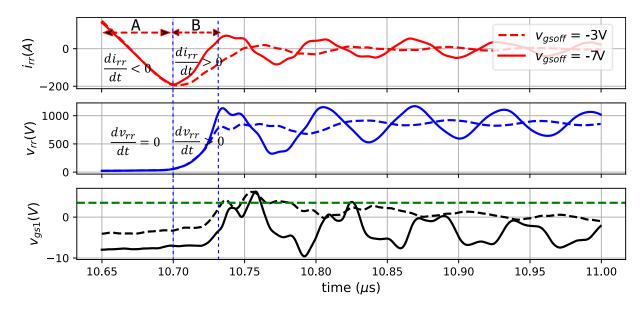

| <b>Figure 5.2:</b> The upper gate voltage $(v_{gsl})$ at different di/dt and du/dt phase during the turn-on of                                                 |

| T32 at turn-off gate voltage $V_{gsoff} = -3V$ (dashed lines) and $V_{gsoff} = -7V$ (solid lines) compare                                                      |

| to the threshold voltage (dashed green line). Module FF3MR12KM1P with Kelvin terminal                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DC} = 900V$ , $IL = 600A$ , $T_j = 150$ °C, $Vth = 3.15V$                                                                                                  |

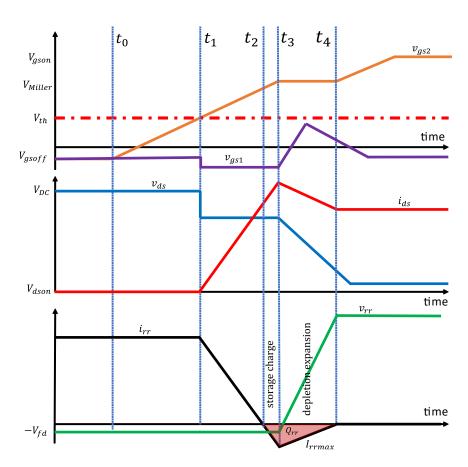

| <b>Figure 5.3:</b> Turn-on process of T32 and the reverse-recovery on T31's body diode                                                                         |

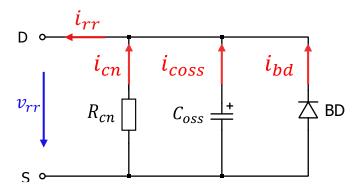

| Figure 5.4: Equivalent circuit of the MOSFET during its body diode's reverse-recovery under                                                                    |

| parasitic turn-on                                                                                                                                              |

| Figure 5.5: Three positive effects of parasitic turn-on effect during the depletion phase of the                                                               |

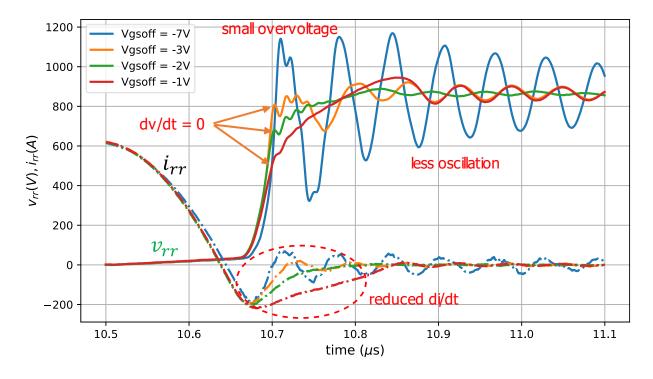

| reverse-recovery. $V_{DC} = 900V$ , $IL = 600A$ , $R_{gon} = 5.6 \Omega$ , $R_{goff} = 5.1 \Omega$ , $T_j = 150^{\circ}C$ , $V_{gsoff} = [-7V, -3V, -2V, -1V]$ |

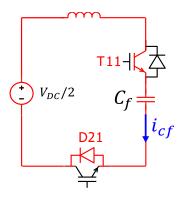

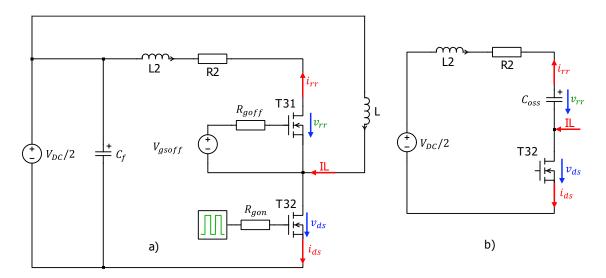

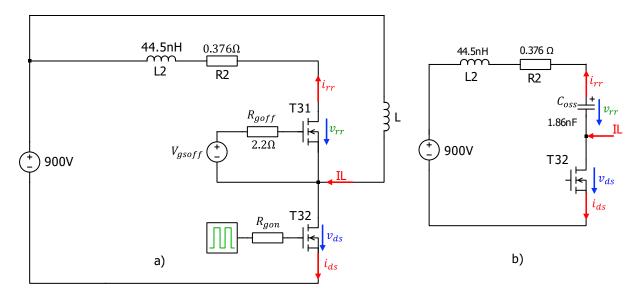

| Figure 5.6: a) Equivalent circuit of 2SiC Hybrid ANPC during the reverse-recovery of T31's                                                                     |

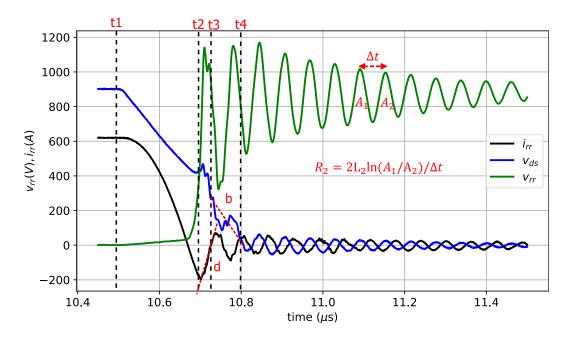

| body diode, b) Small signal circuit during the turn-on of T32 108                                                                                              |

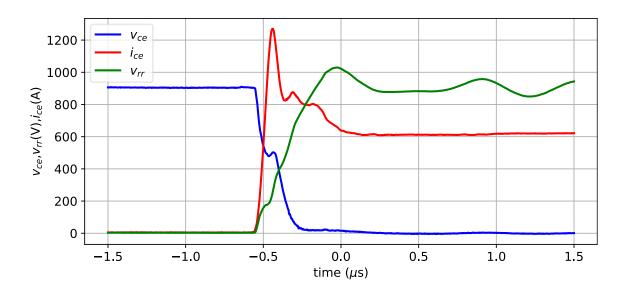

| Figure 5.7: Regular reverse-recovery waveform and the commutation circuit's resistance R2 and                                                                  |

| inductance $L_2$ extraction from the measured waveform                                                                                                         |

| Figure 5.8: Two-level double pulse test experiment to verify the analytical model proposed in                                                                  |

| equation (5.36). a) The 2-level turn-on double pulse test schematic, b) Equivalent circuit a                                                                   |

| the reverse-recovery $t=t_3$                                                                                                                                   |

| <b>Figure 5.9:</b> Case 1: $R_{gon} = 4.7 \Omega$ , $R_{goff} = 2.2 \Omega$ , $V_{gsoff} = -7V$ , $V_{gson} = 15V$ , fitting the calculated                    |

| model (red dashed line) to the measurement result (green line) 114                                                                                             |

| <b>Figure 5.10:</b> Case 2: $R_{gon} = 4.7 \Omega$ , $R_{goff} = 2.2 \Omega$ , $V_{gsoff} = -2V$ , $V_{gson} = 15V$ , fitting the calculated                   |

| model (red dashed line) to the measurement result (green line)                                                                                                 |

| <b>Figure 5.11:</b> Case 3: $R_{gon} = 2.2 \Omega$ , $R_{goff} = 2.2 \Omega$ , $V_{gsoff} = -2V$ , $V_{gson} = 15V$ fitting calculated mode                    |

| (red dashed line) to the measurement result (green line)                                                                                                       |

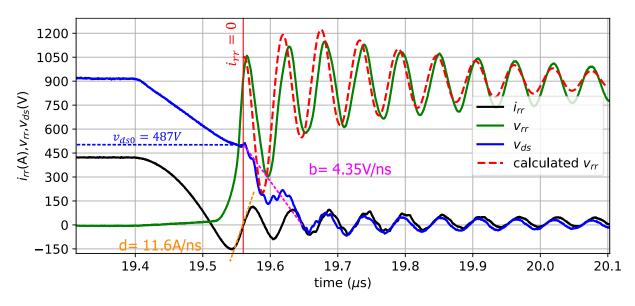

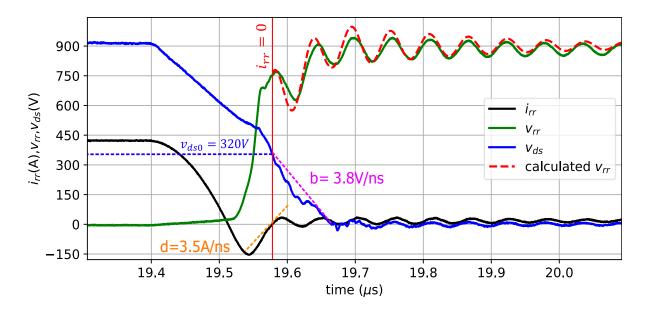

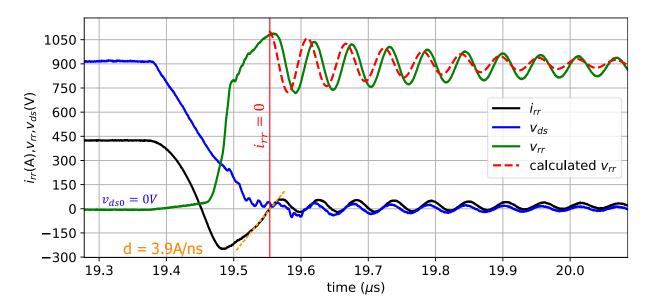

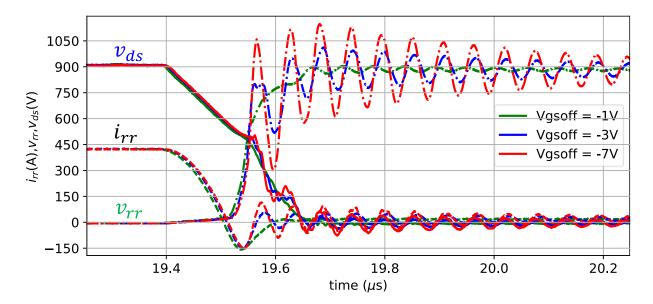

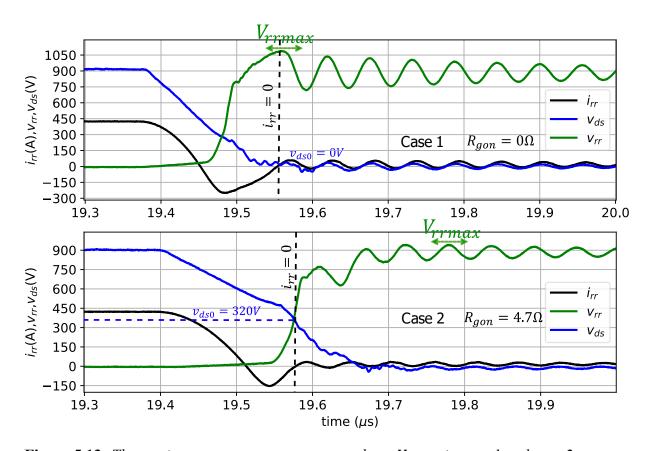

| Figure 5.12: Reverse-recovery waveforms with different turn-off gate voltages and the same gate                                                                |

| resistances: $R_{gon} = 4.7\Omega$ . The voltage slopes b are similar. The oscillation amplitudes are                                                          |

| smaller when the reverse-recovery current slope d is slower                                                                                                    |

| Figure 5.13. The maximum reverse recovery everyaltage Verman in case 1 and case 2                                                                              |

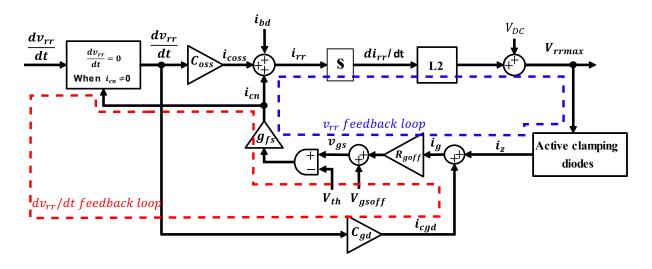

| Figure 5.14: Feedback control loops of active clamping (dashed blue line) and parasitic turn-o                                | Э'n        |

|-------------------------------------------------------------------------------------------------------------------------------|------------|

| (dashed red line) in case 1                                                                                                   | 19         |

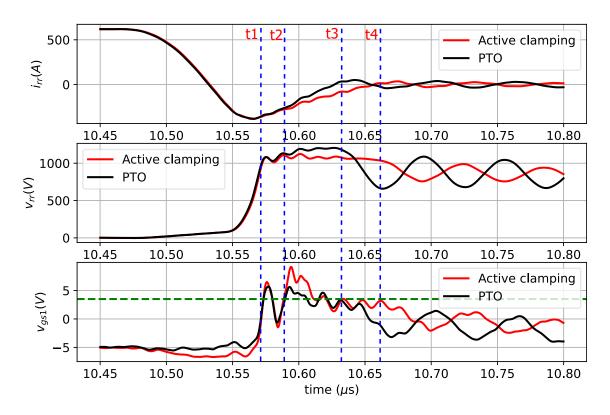

| Figure 5.15: The difference between the active clamping (red lines) and parasitic turn-on (black)                             | ck         |

| lines) during the reverse-recovery. $V_{DC}=1800V$ , $IL=600A$ , $R_{gon}=0\Omega$ , $R_{goff}=5.1~\Omega$ , $T_{j}$          | =          |

| 150°C, $V_{gsoff} = -5V$ , VTVS = 1020V, Vth = 3.15V                                                                          | 20         |

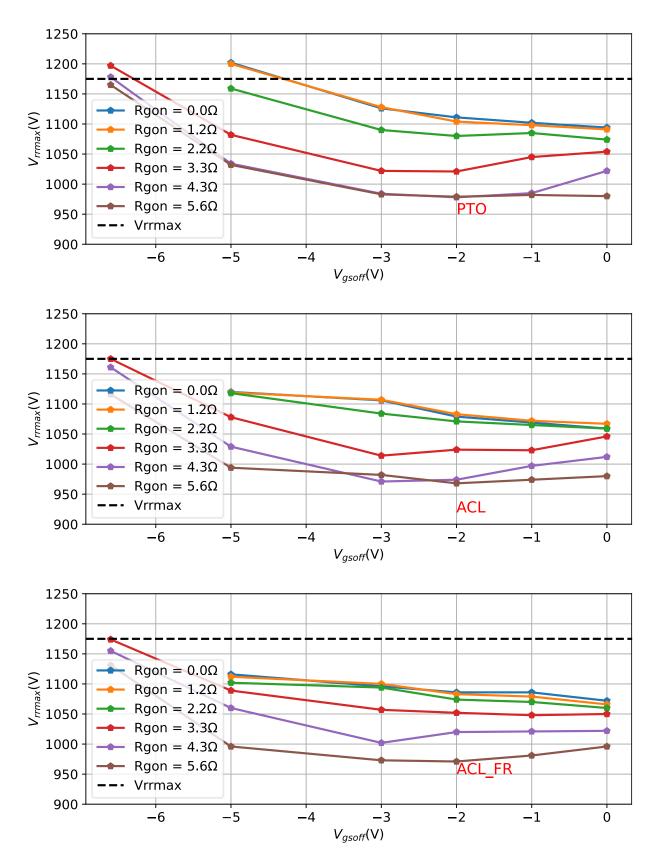

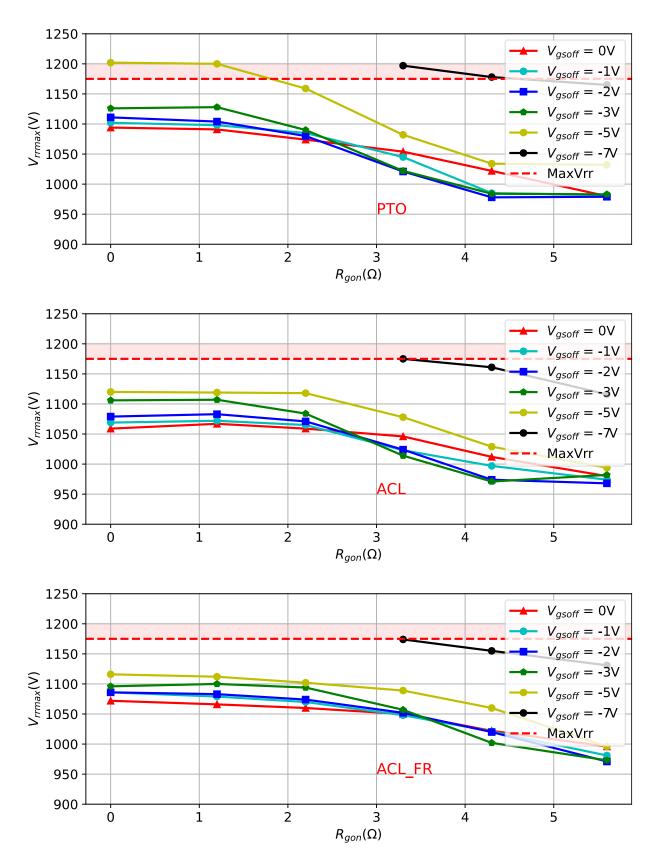

| <b>Figure 5.16:</b> Reverse-recovery overvoltage over the $V_{gsoff}$ for 3 different cases, at $V_{DC}$ = 1800               | V,         |

| $IL = 600A$ , $T_j = 150$ °C, $R_{goff} = 5.1\Omega$ .                                                                        | 22         |

| <b>Figure 5.17:</b> Reverse-recovery overvoltage over the $R_{gon}$ for 3 different cases, at $V_{DC}$ = 1800 $V$ , $R_{gon}$ | ΙL         |

| $= 600A, T_j = 150$ °C, $R_{goff} = 5.1$                                                                                      | 23         |

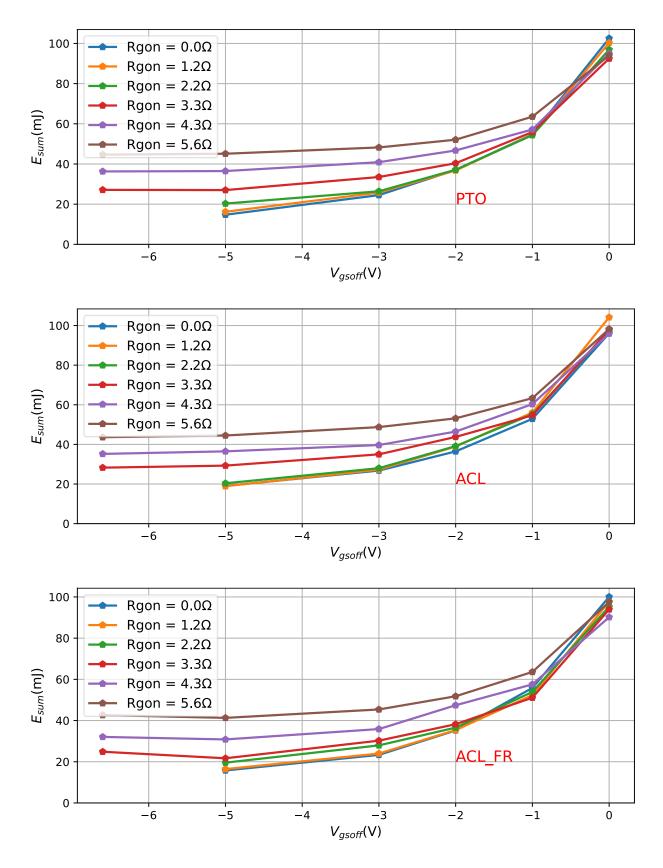

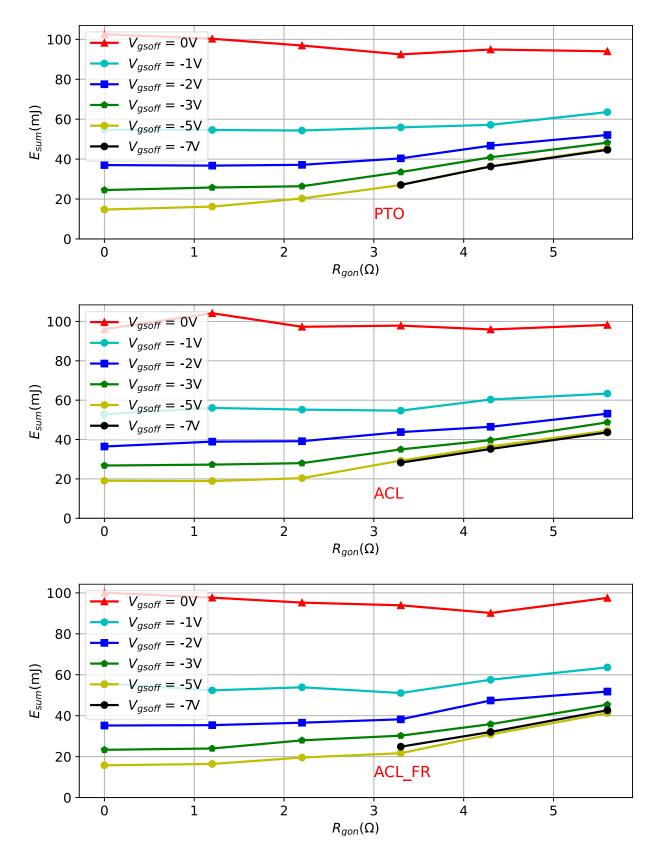

| <b>Figure 5.18:</b> The total turn-on losses over the $V_{gsoff}$ for 3 different cases, at $V_{DC}$ = 1800V, IL              | =          |

| 600A, $T_j = 150$ °C, $R_{goff} = 5.1\Omega$                                                                                  | 24         |

| <b>Figure 5.19:</b> The total turn-on losses over the $R_{gon}$ for 3 different cases, at $V_{DC}$ = 1800V, IL                | =          |

| 600A, $T_j = 150$ °C, $R_{goff} = 5.1\Omega$                                                                                  | 25         |

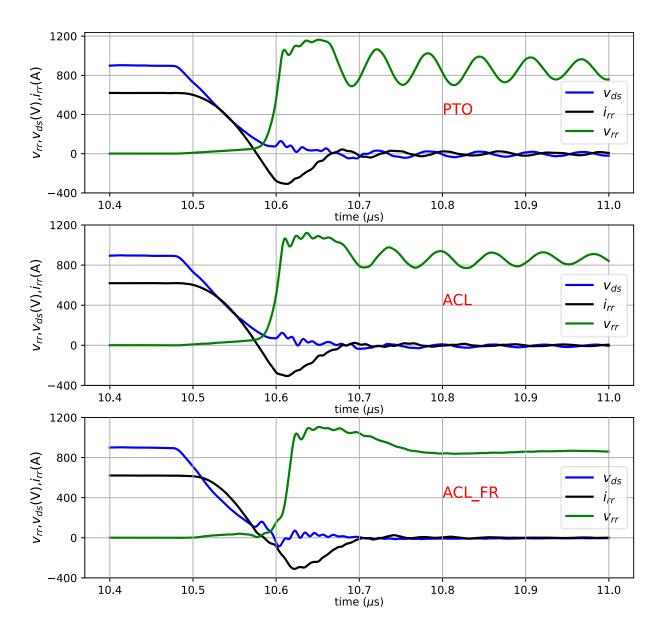

| <b>Figure 5.20:</b> Reverse-recovery waveforms at $V_{gsoff} = -5V$ and $R_{gon} = 2.2\Omega$ , $R_{goff} = 5.1\Omega V_{DO}$ | <u>;</u> = |

| 1800V, $IL = 600A$ , $Tj = 150$ °C in 3 cases: PTO: parasitic turn-on, ACL: active clampin                                    | g,         |

| ACL FR: active clamping and dual ferrite cores                                                                                |            |

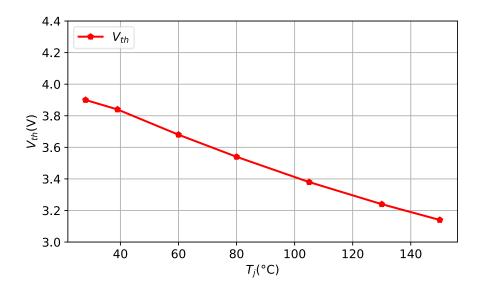

| <b>Figure 5.21:</b> The variation of FF3MR12KM1P MOSFET's threshold voltage against the junction temperature                  |            |

| 1                                                                                                                             |            |

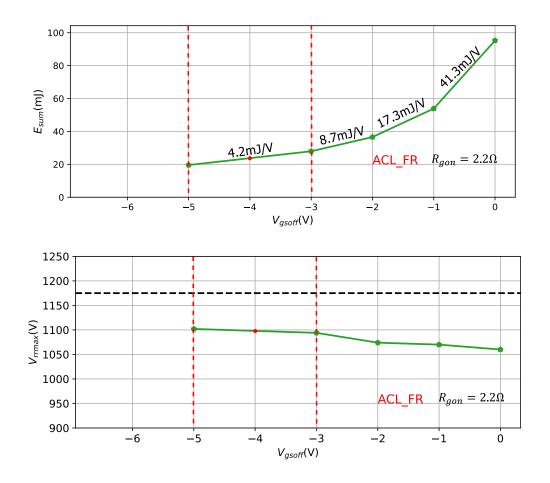

| <b>Figure 5.22:</b> The total turn-on losses $E_{sum}$ a) and the reverse-recovery overvoltage $V_{rrmax}$ b)                 | in         |

| case of $R_{gon}=2.2\Omega$ when the active clamping and ferrite cores (ACL-FR) are used. $V_{DC}$                            | <u>;</u> = |

| $1800V$ , $IL = 600A$ , $T_j = 150$ °C, $R_{goff} = 5.1\Omega$                                                                | 29         |

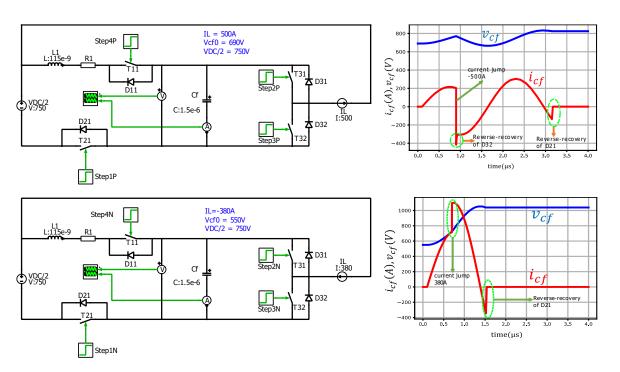

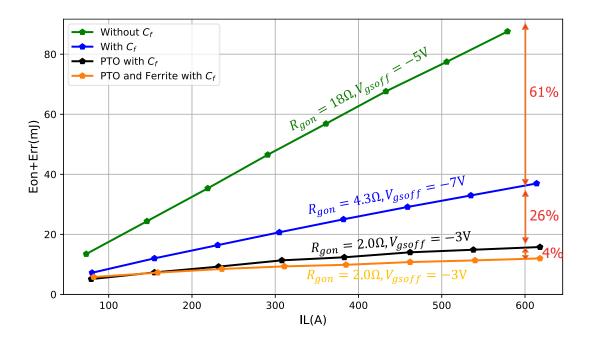

| <b>Figure 5.23:</b> Compare the total turn-on losses in different scenarios, $V_{DC} = 1500V$ , $25^{\circ}C$ 13              | 30         |

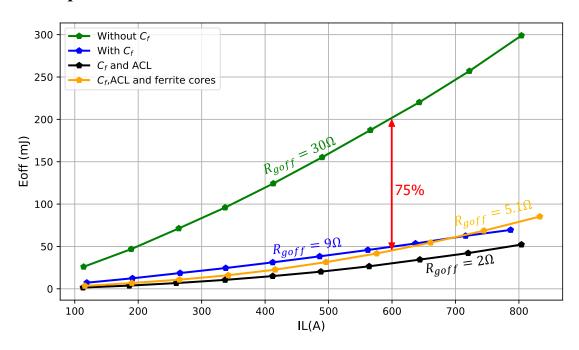

| <b>Figure 5.24:</b> Compare the turn-off losses in different scenarios, $V_{DC}$ = 1500V, 25°C                                | 31         |

| <b>Figure 5.25:</b> SiC MOSFET's turn-off voltage and current in different cases. $V_{DC} = 1500V$ , 25°c                     | <i>C</i> . |

| 13                                                                                                                            | 27         |

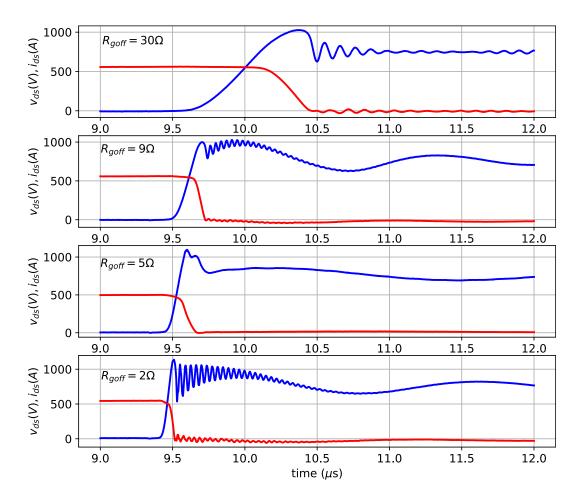

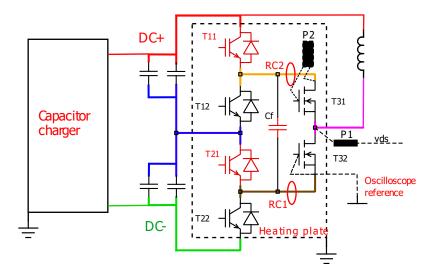

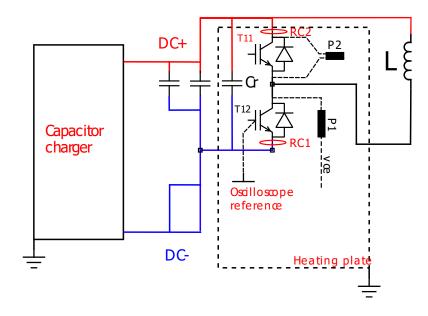

| <b>Figure 6.1:</b> Double pulse test setup for the characterization of the SiC MOSFET                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

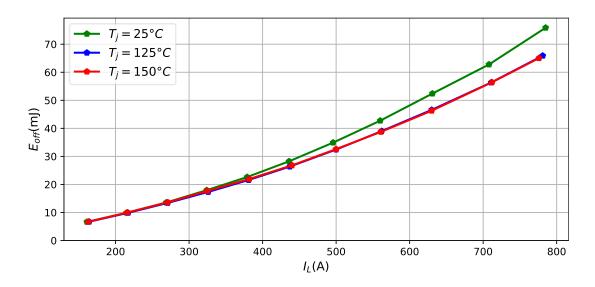

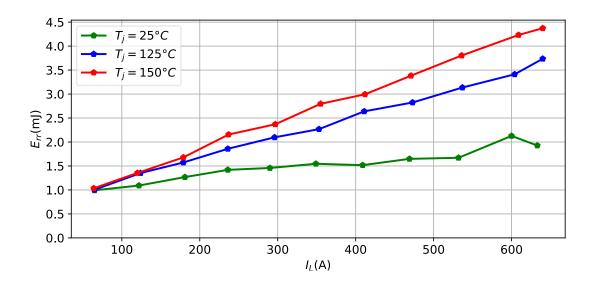

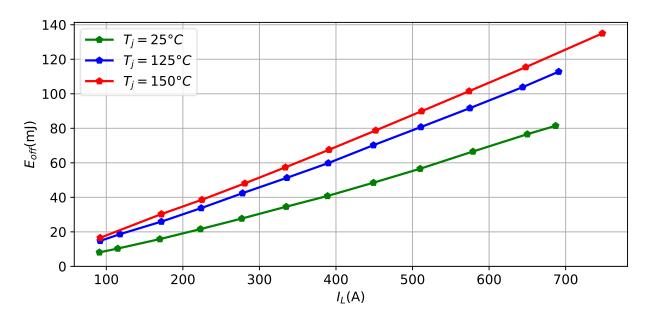

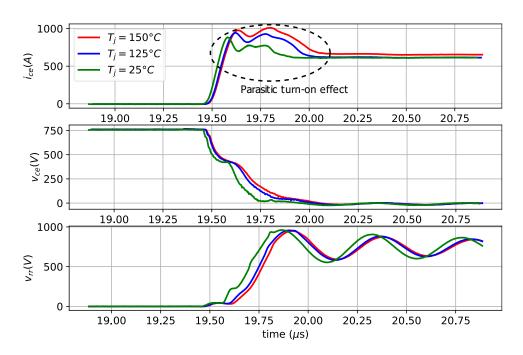

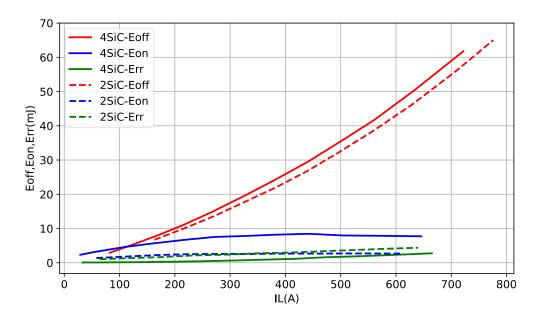

| <b>Figure 6.2:</b> Turn-off losses at different load currents and temperatures. Switching conditions $V_{DG}$ = 1500V, $T_j = 25$ °C, 125°C, 150°C, L $\sigma$ = 46nH, $V_{gsoff} = -4V$ , $R_{gon} = 2.2\Omega$ , $R_{goff} = 5.1\Omega$ TVS' breakdown voltage = 1020V                                                                                                          |

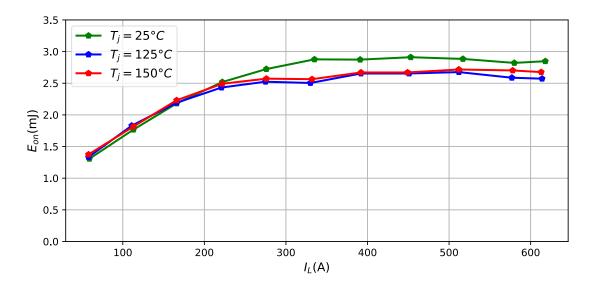

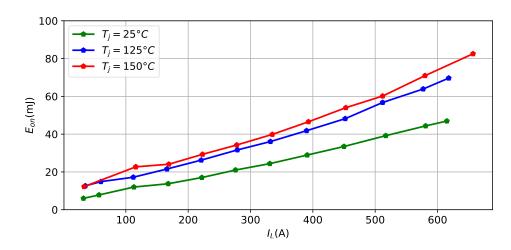

| <b>Figure 6.3:</b> Turn-on losses at different load currents and temperatures. Switching conditions $V_{DG}$                                                                                                                                                                                                                                                                      |

| = 1500V, $T_j = 25$ °C, 125°C, 150°C, $L\sigma = 46$ nH, $V_{gsoff} = -4V$ , $R_{gon} = 2.2\Omega$ , $R_{goff} = 5.1\Omega$                                                                                                                                                                                                                                                       |

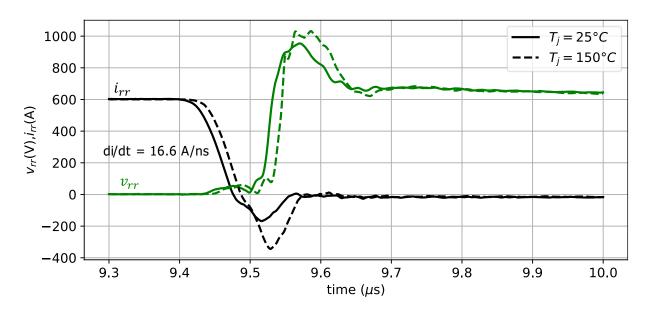

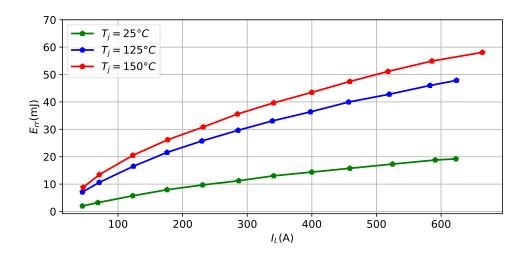

| TVS' breakdown voltage = 1020V136                                                                                                                                                                                                                                                                                                                                                 |

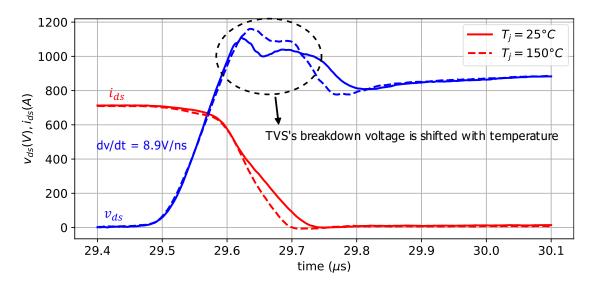

| <b>Figure 6.4:</b> Reverse-recovery losses at different load currents and temperatures. Switching conditions $V_{DC} = 1500V$ , $T_j = 25^{\circ}C$ , $125^{\circ}C$ , $150^{\circ}C$ , $L\sigma = 46$ nH, $V_{gsoff} = -4V$ , $R_{gon} = 2.2\Omega$ $R_{goff} = 5.1\Omega$ , $TVS'$ breakdown voltage = $1020V$ .                                                                |

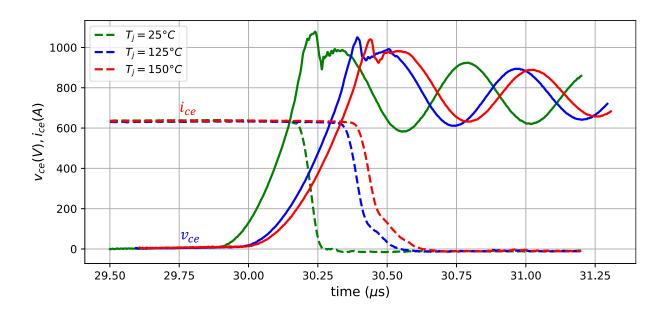

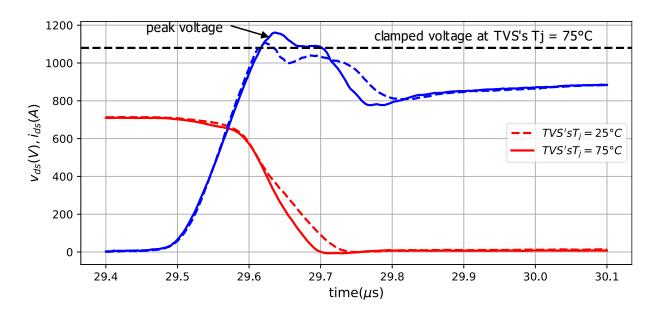

| <b>Figure 6.5:</b> SiC MOSFET's turn-off waveforms. Switching conditions $V_{DC} = 1500V$ , $T_j = 25^{\circ}C$ (solid lines), $150^{\circ}C$ (dashed lines), $L\sigma = 46$ nH, $V_{gsoff} = -4V$ , $R_{gon} = 2.2\Omega$ , $R_{goff} = 5.1\Omega$ , $TVS$ breakdown voltage at $25^{\circ}C = 1000V$ , $TVS$ ' breakdown voltage at $75^{\circ}C = 1060V$ , with ferrite cores. |

| <b>Figure 6.6:</b> SiC MOSFET's turn-on waveforms. Switching conditions $V_{DC} = 1500V$ , $IL = 600A$                                                                                                                                                                                                                                                                            |

| $T_j = 25$ °C (solid lines), 150°C (dashed lines), L $\sigma = 46$ nH, $V_{gsoff} = -4V$ , $R_{gon} = 2.2\Omega$ , $R_{goff} = 5.1\Omega$ , with ferrite cores                                                                                                                                                                                                                    |

| <b>Figure 6.7:</b> <i>IGBT's double pulse test setup.</i> 139                                                                                                                                                                                                                                                                                                                     |

| <b>Figure 6.8:</b> $C_{goff}$ circuit to reduce the turn-off delay time                                                                                                                                                                                                                                                                                                           |

| <b>Figure 6.9:</b> Cgoff circuit switching waveform with different $C_{goff}$ . Switching conditions: $V_{DC} = 900V$ , $IL = 600A$ , $T_j = 25$ °C, $RC = 200\Omega$ , $R_{goff} = 7.5\Omega$ , $V_{gsoff} = -5V$ , $TVS$ 's breakdown voltage at $1020V$ .                                                                                                                      |

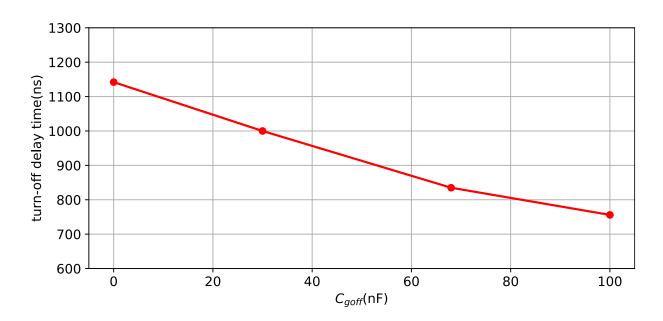

| <b>Figure 6.10:</b> Turn-off delay time with different $C_{goff}$ . Switching conditions: $V_{DC} = 900V$ , $IL = 1000$                                                                                                                                                                                                                                                           |

| 600A, $T_j = 25$ °C, $RC = 200\Omega$ , $R_{goff} = 7.5\Omega$ , $V_{gsoff} = -5V$                                                                                                                                                                                                                                                                                                |

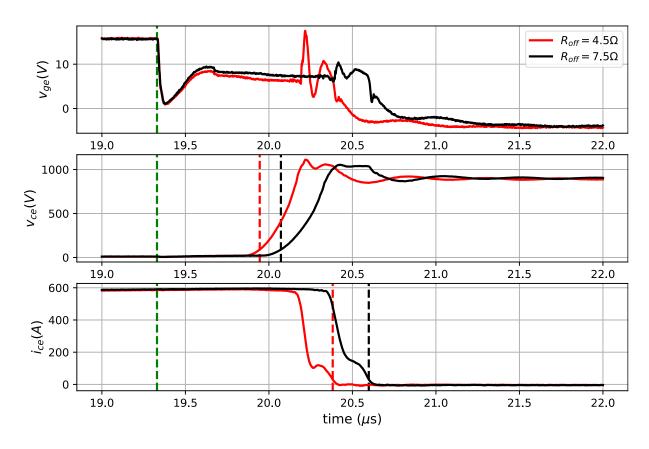

| <b>Figure 6.11:</b> Cgoff circuit with different $R_{goff}=4.5\Omega$ , $7.5\Omega$ . The green dashed line marks the                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| start of the transition, the dashed lines mark the end of the turn-off delay phase and the dash                                               |

| doted lines mark the end of the transient phase. $V_{DC} = 900V$ , $IL = 600A$ , $T_j = 25$ °C 14                                             |

| Figure 6.12: Turn-off losses at different load currents and temperatures. Switching conditions                                                |

| TVS breakdown voltage at 1020V, $V_{DC}$ =750V, $R_{goff}$ = 4.5 $\Omega$ , $C_{goff}$ = 100nF, $RC$ = 200 $\Omega$                           |

| $V_{gsoff} = -5V. 		 142$                                                                                                                     |

| Figure 6.13: Turn-off transients at different junction temperature. Switching conditions: TVS                                                 |

| breakdown voltage at 1020V, $V_{DC}$ =750V, IL = 600A, $R_{goff}$ = 4.5 $\Omega$ , $C_{goff}$ = 100nF, RC =                                   |

| $200\Omega, V_{gsoff} = -5V.$                                                                                                                 |

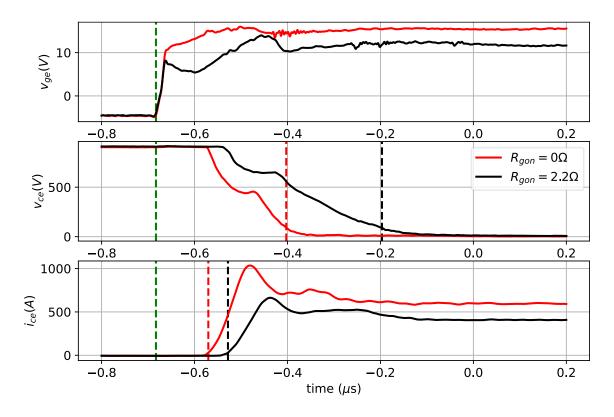

| <b>Figure 6.14:</b> <i>IGBT's turn-on switching waveforms with</i> $R_{gon} = \partial \Omega$ , $V_{DC} = 900V$ , $IL = 600A$ , $T_j = 600A$ |

| 150°C                                                                                                                                         |

| <b>Figure 6.15:</b> Turn-on switching waveforms with different $R_{gon} = 0\Omega$ , 2.2 $\Omega$ . The green dashed line                     |

| marks the start of the transition, the red and black dashed lines mark the end of the turn-or                                                 |

| delay phase and the dash-doted red and black lines mark the end of the transient phase. $V_{D\theta}$                                         |

| $= 900V, IL = 600A, T_j = 25^{\circ}C.$                                                                                                       |

| <b>Figure 6.16:</b> Turn-on switching waveforms at different temperature. Switching conditions: $V_{D0}$                                      |

| =750V, $IL = 600A$ , $R_{gon} = 2.2\Omega$ , $V_{gsoff} = -5V$                                                                                |

| <b>Figure 6.17:</b> Turn-on losses at different load current and temperature. Switching conditions: $V_{D0}$                                  |

| $=750V$ , $R_{gon}=2.2\Omega$ , $V_{gsoff}=-5V$                                                                                               |

| Figure 6.18: Reverse-recovery losses at different load current and temperature. Switching                                                     |

| conditions: $V_{DC} = 750V$ , $R_{gon} = 2.2\Omega$ , $V_{gsoff} = -5V$                                                                       |

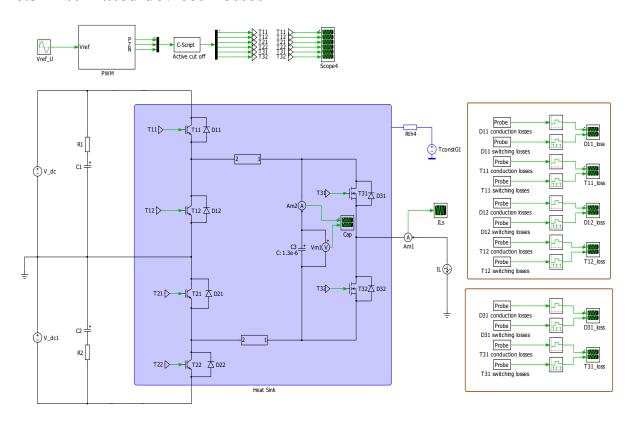

| <b>Figure 6.19:</b> <i>PLECS simulation for semiconductor devices' losses estimation.</i>                                                     |

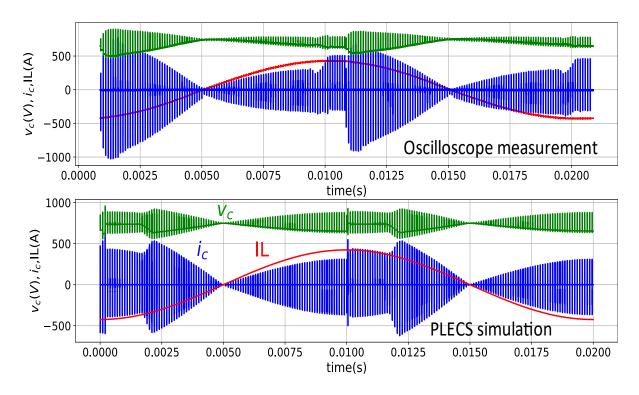

| Figure 6.20: Matching the decoupling capacitor voltage and current waveforms in PLECS                                                         |

| simulation and real measurement147                                                                                                            |

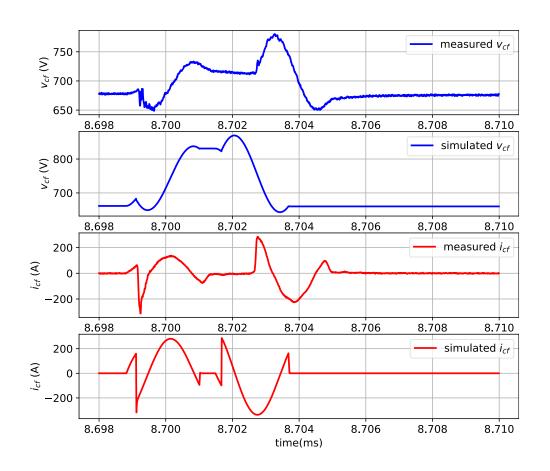

| Figure 6.21: Comparison of Cf voltage and current in real measurement and simulation 148                                                      |

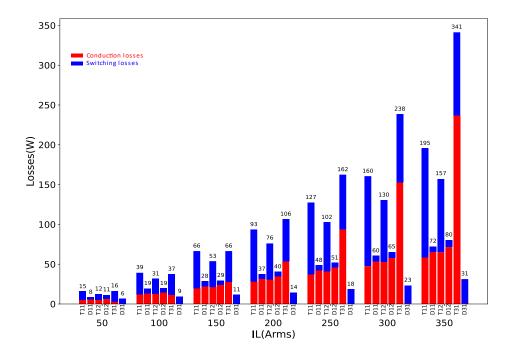

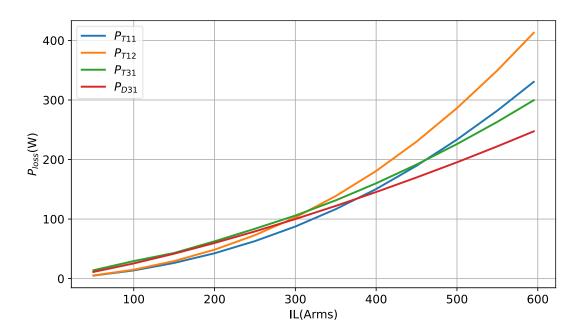

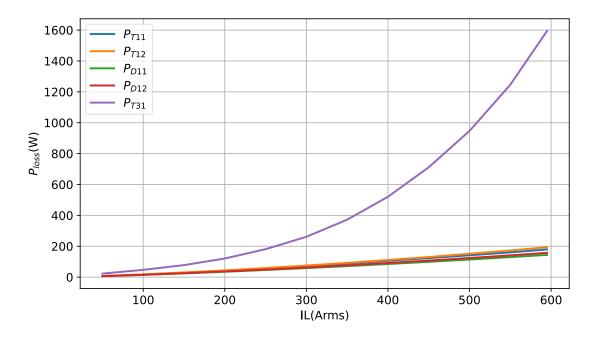

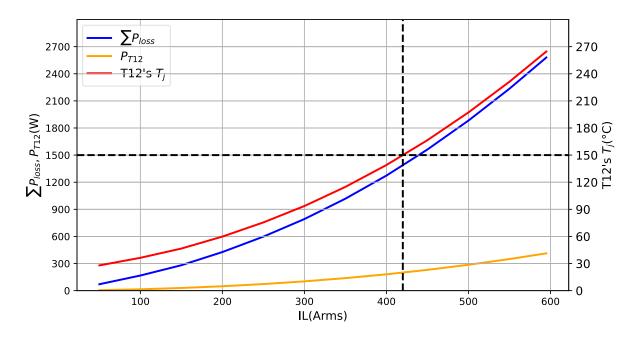

| Figure 6.22: The losses on the semiconductor devices at different operating current and 10kHz                   |

|-----------------------------------------------------------------------------------------------------------------|

| switching frequency148                                                                                          |

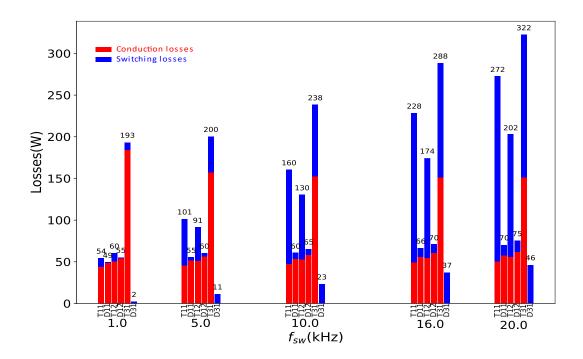

| Figure 6.23: The losses on the semiconductor at different switching frequencies with the active                 |

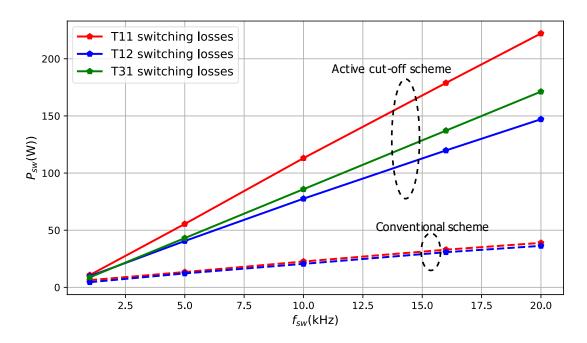

| cut off scheme. IL = 300Arms                                                                                    |

| Figure 6.24: Compare switching losses on the IGBT and MOSFET with active cut-off switching                      |

| scheme (solid lines) and conventional switching scheme (dashed lines). $IL = 300$ Arms. 149                     |

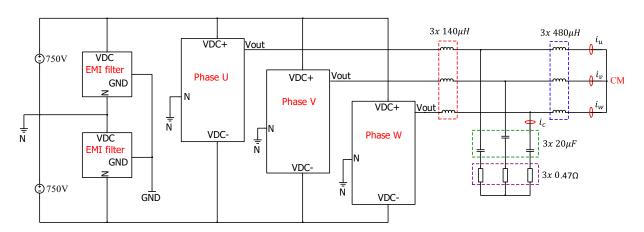

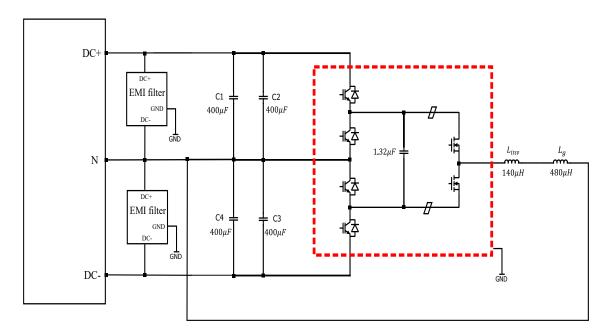

| Figure 6.25: Three phase current waveform measurement diagram                                                   |

| <b>Figure 6.26:</b> Three phase start connected load inductors 3x 480μH-600Arms and the start poin              |

| CM where the 3 phase load currents are measured                                                                 |

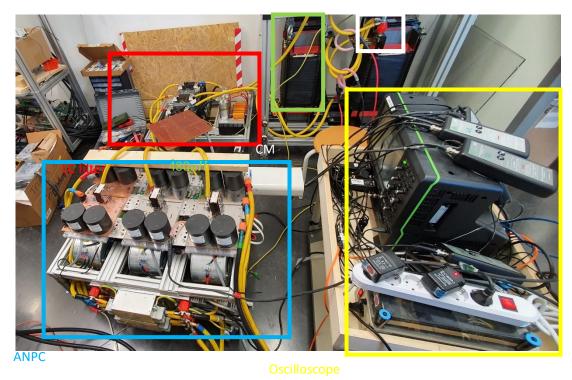

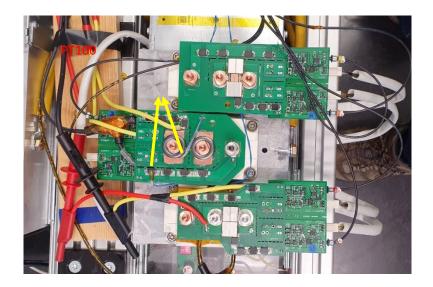

| Figure 6.27: Three phase current waveform measurement test setup                                                |

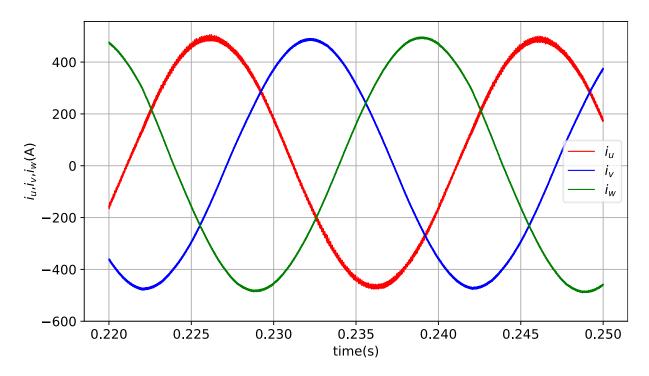

| Figure 6.28: Three phase load current waveform at the steady state nominal current 340Arms                      |

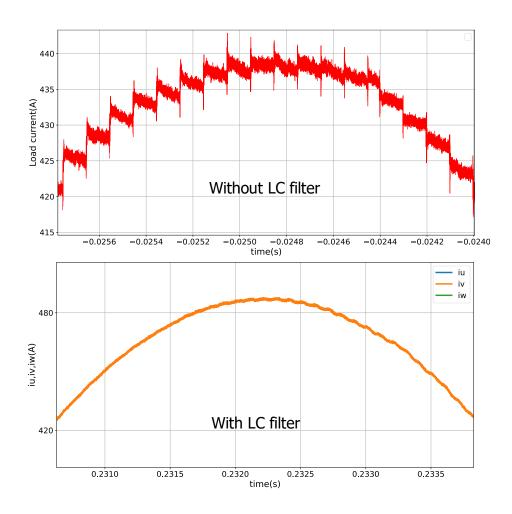

| Figure 6.29: Compare load current with and without LC filter                                                    |

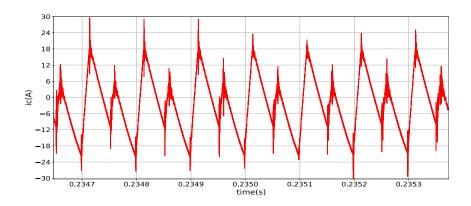

| <b>Figure 6.30:</b> <i>LC filter's capacitor current:</i> Ic = 8Arms, <i>peak-peak current ripple</i> = 36A 152 |

| Figure 6.31: The continuous operation experiment diagram                                                        |

| Figure 6.32: Active clamping diode and ferrite cores temperature are measured with PT100                        |

| sensors                                                                                                         |

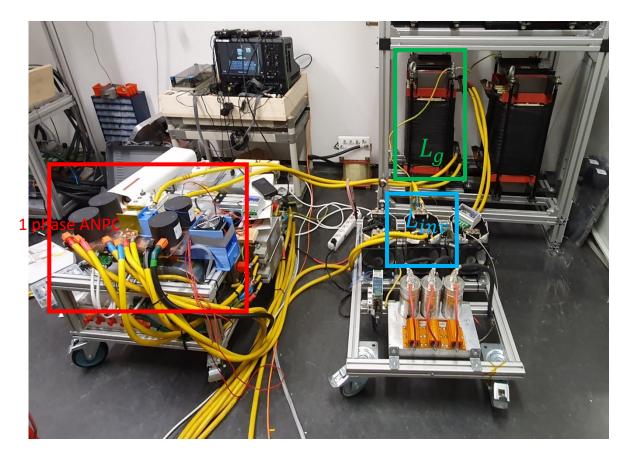

| <b>Figure 6.33:</b> The continuous operation experiment setup for one phase of the ANPC                         |

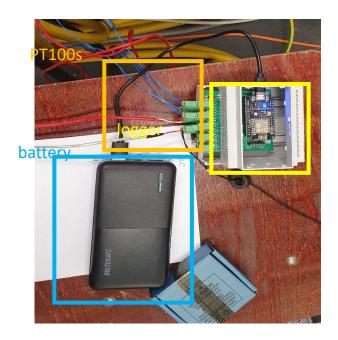

| <b>Figure 6.34:</b> The Wifi temperature logger device with battery supply                                      |

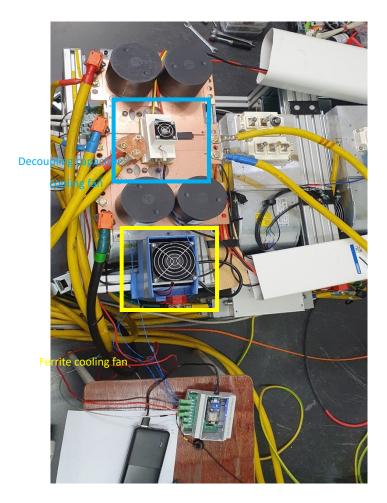

| <b>Figure 6.35:</b> Ferrite cores and decoupling capacitor are cooled with fans                                 |

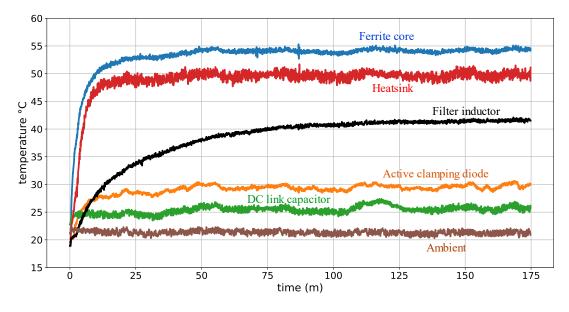

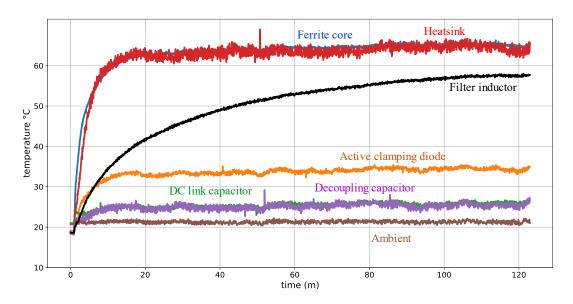

| <b>Figure 6.36:</b> Critical components' temperatures at IL = 210 Arms                                          |

| <b>Figure 6.37:</b> Critical components' temperatures at IL = 280 Arms                                          |

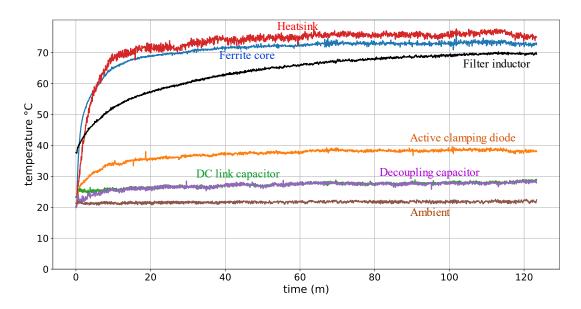

| <b>Figure 6.38:</b> Critical components' temperatures at IL = 305 Arms                                          |

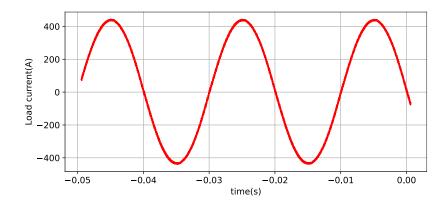

| <b>Figure 6.39:</b> Load current waveform at 305Arms156                                             |

|-----------------------------------------------------------------------------------------------------|

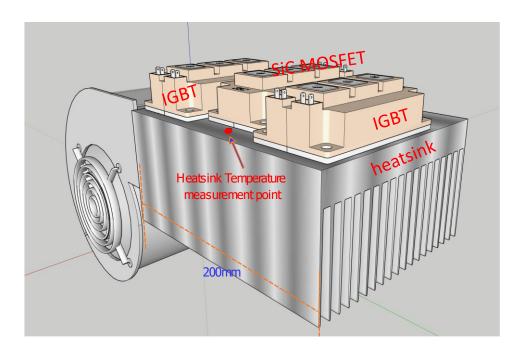

| <b>Figure 6.40:</b> The cooling fan and heatsink temperature measurement point                      |

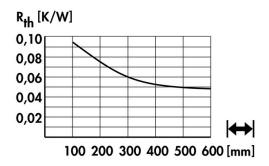

| <b>Figure 6.41:</b> <i>Heatsink Fisher Elektronik LA 25 200 230, length:200mm [64].</i>             |

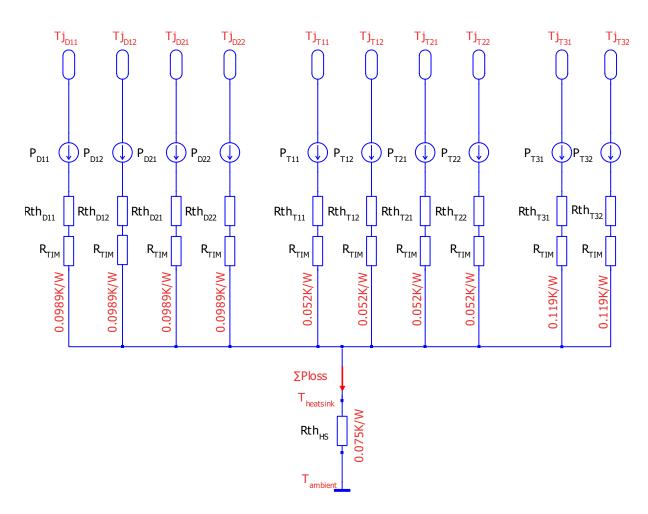

| <b>Figure 6.42:</b> The steady state thermal model of 2SiC hybrid ANPC                              |

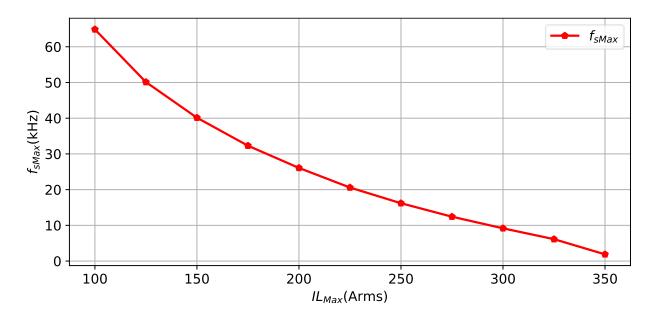

| Figure 6.43: 2SiC hybrid ANPC's maximum output current and maximum switching frequency              |

| for the active cut-off switching scheme to limit the SiC MOSFET's junction temperature              |

| below 150°C                                                                                         |

| <b>Figure 6.44:</b> Compare a) 4SiC hybrid ANPC and b) 2SiC hybrid ANPC                             |

| Figure 6.45: Compare the switching energies of SiC MOSFET in 2SiC hybrid ANPC (dashed               |

| lines) and 4SiC hybrid ANPC (solid lines) at 1500V, 150°C                                           |

| Figure 6.46: The total losses on each semiconductor switch in 4SiC hybrid ANPC at 10kHz             |

| switching with PWM-1, modulation index = $1$                                                        |

| Figure 6.47: The total losses on each semiconductor switch in 2SiC hybrid ANPC at 10kHz             |

| switching with PWM-2, modulation index = $1$                                                        |

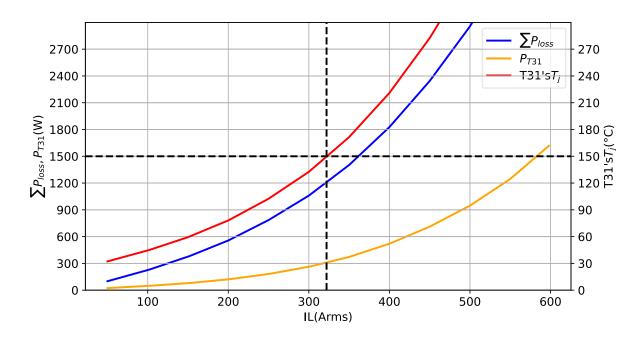

| Figure 6.48: The total losses of T31 in 2SiC hybrid ANPC at 10kHz switching frequency. The          |

| maximum load current that 2SiC ANPC can handle is 320 Arms to keep T31's junction                   |

| temperature below 150°C at 22°C ambient temperature                                                 |

| Figure 6.49: The total losses of T12 in 4SiC hybrid ANPC at 10kHz switching frequency. The          |

| maximum load current that 4SiC ANPC can handle is 420 Arms to keep T12's junction                   |

| temperature below 150°C at 22°C ambient temperature                                                 |

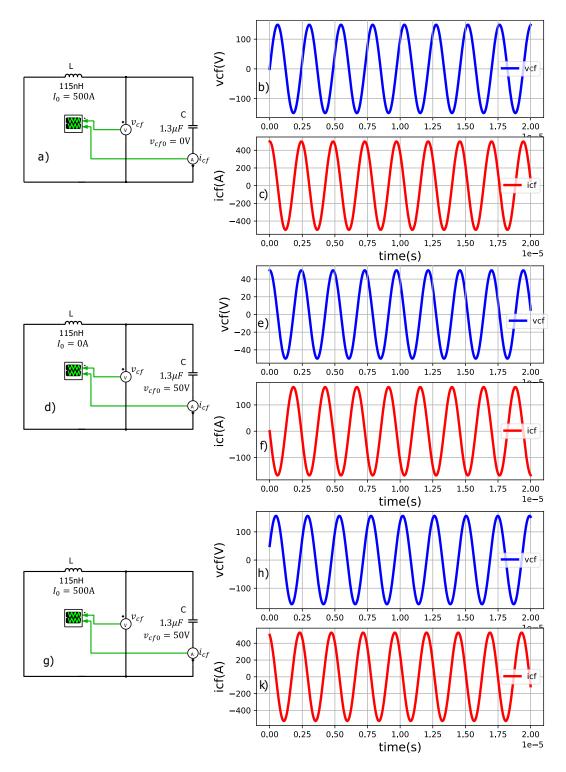

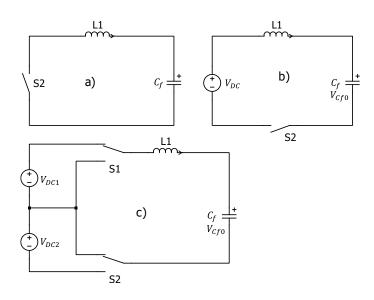

| Figure A. 1.1: LC oscillation circuit with different initial energy storage, a) inductance storage, |

| d) capacitor storage, g) inductance and capacitance storage. Capacitor's voltage and                |

| <i>current in case a: b, c, case d: e, f, case g:h, k.</i>                                          |

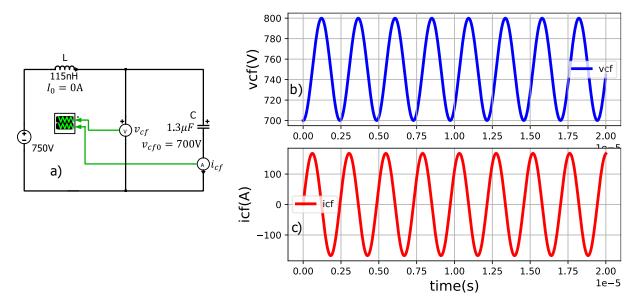

| <b>Figure A. 1.2:</b> a) LC oscillator with DC voltage in the circuit. b, c) voltage and current of the capacitor                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

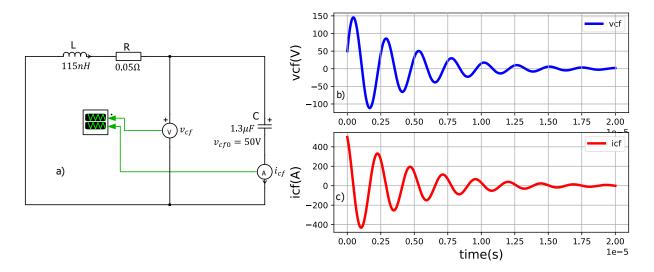

| <b>Figure A. 1.3:</b> a) <i>LCR oscillation circuit. b, c) Capacitor's voltage and current.</i>                                                                                                                                                                                          |

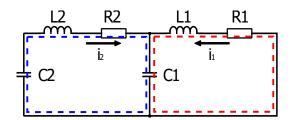

| <b>Figure A. 1.4:</b> Two coupled LCR circui $t$ : $L_1C_1R_1$ and $L_2C_2R_2$                                                                                                                                                                                                           |

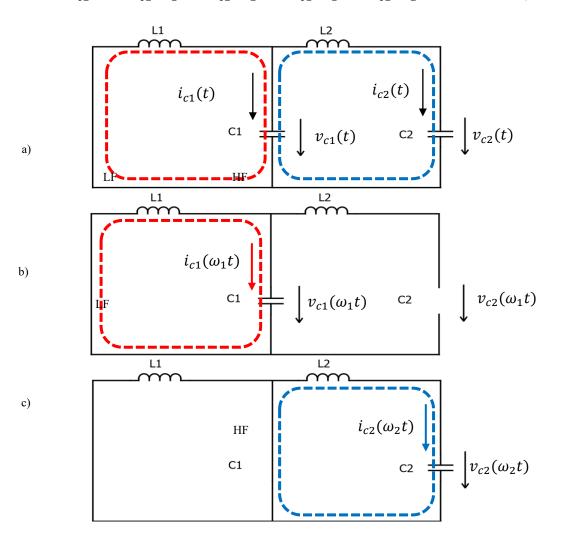

| <b>Figure A. 1.5:</b> The coupled LCR oscillator. a) equivalent circuit in time domain, b) equivalent oscillation circuit at low frequency ω1, c) equivalent oscillation circuit at hig frequency ω2.                                                                                    |

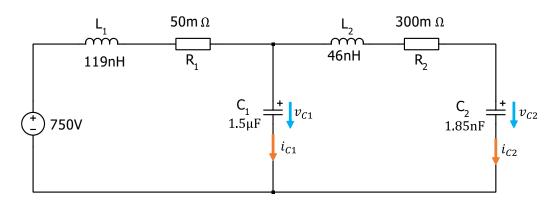

| <b>Figure A. 1.6:</b> SIMetrix simulation of the coupled LCR oscillator                                                                                                                                                                                                                  |

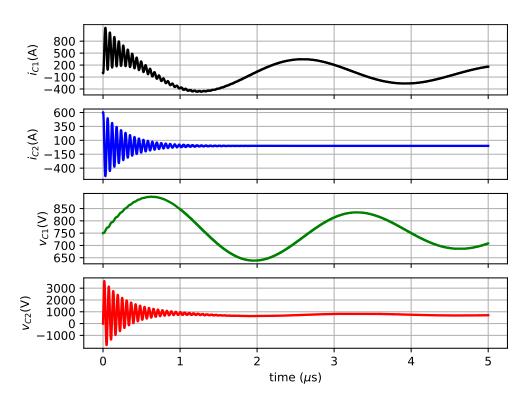

| <b>Figure A. 1.7:</b> SIMetrix simulation result of the coupled LCR oscillator                                                                                                                                                                                                           |

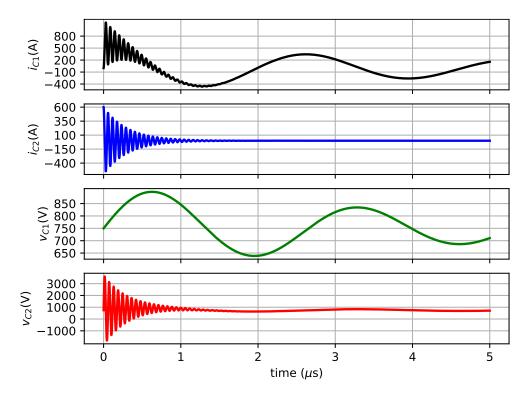

| <b>Figure A. 1.8:</b> Analytical result of the proposed model for the simulation circuit in Figure A. 1.6.                                                                                                                                                                               |

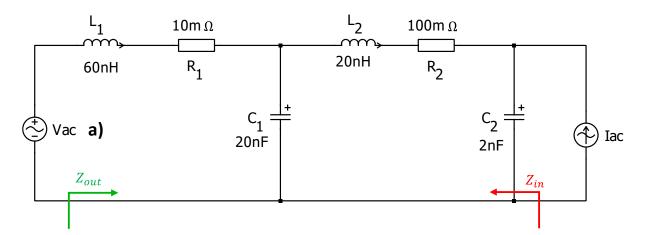

| <b>Figure A. 1.9:</b> a) a coupled LCR network and b) its input impedance (red line) and output impedance (green line) in the frequency domain                                                                                                                                           |

| <b>Figure A. 1.10:</b> Different variants of the voltage slope trigger the oscillation at the output of the oscillator.                                                                                                                                                                  |

| <b>Figure A. 1.11:</b> Small signal simulation of current slope trigger at the input of the coupled Lecircuit.                                                                                                                                                                           |

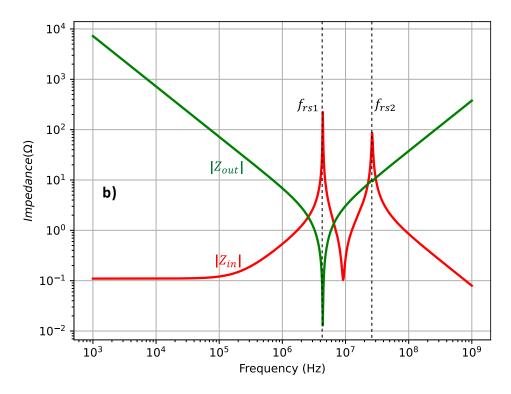

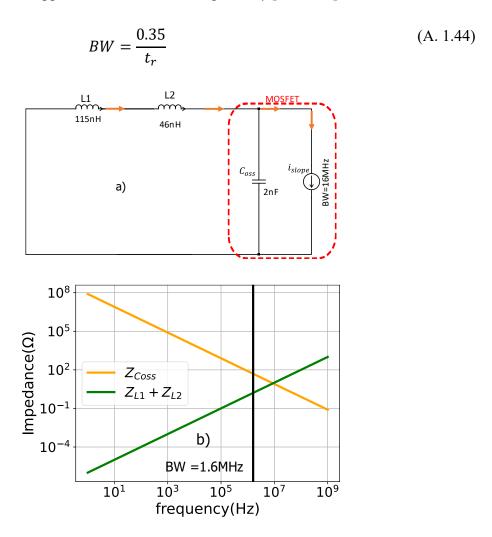

| <b>Figure A. 1.12:</b> a) Current slope at the input of an LC circuit without decoupling capacitor. By The impedance spectrum of $L_1+L_2$ and Coss at the frequency bandwidth of the current slope icn, $BW = 1.6MHz$ , $L_1+L_2 = 161nH$ , $Coss = 2nF$ , $Z_{L1}+Z_{L2} \ll Z_{Coss}$ |

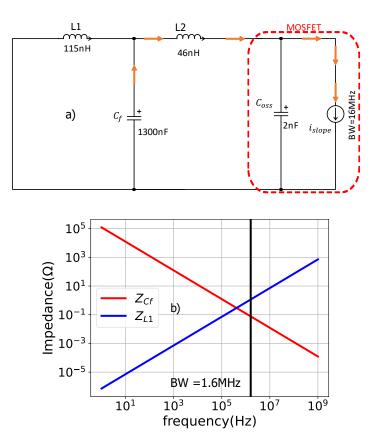

| <b>Figure A. 1.13:</b> a) Current slope at the input of a coupled LC circuit formed by inserting decoupling capacitor Cf. The impedance of $L_1$ and Cf at the frequency bandwidth of the current slope icn, $BW = 1.6MHz$ , $L1 = 115nH$ , $Cf = 1.3\mu F$ , $ZCf \ll ZL1$              |

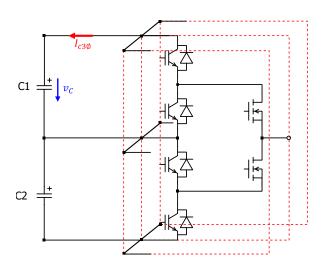

| <b>Figure A. 2.1:</b> 3 phases ANPC and 3-phases DC link capacitor current                                                                                                                                                                                                               |

| <b>Figure A. 2.2:</b> DC link capacitors for 1 phase of the hybrid ANPC                                                                                                                                                                                                                  |

| <b>Figure A. 2.3:</b> Single phase layout of the hybrid ANPC inverter                                                                                                                                                                        |

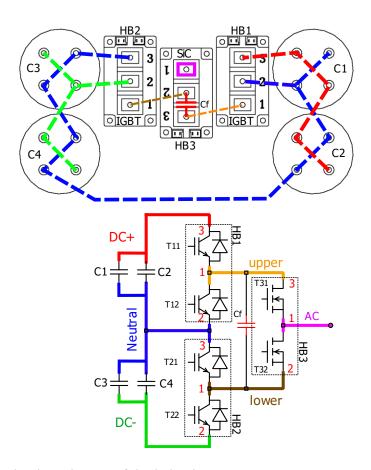

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

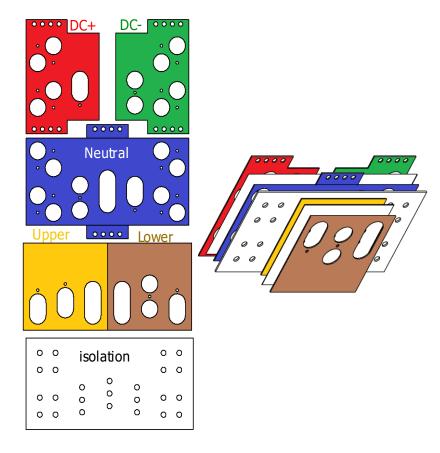

| <b>Figure A. 2.4:</b> Busbar layers and their arrangement                                                                                                                                                                                    |

| <b>Figure A. 2.5:</b> Different commutation loops' inductance in the hybrid ANPC. a) MOSFE commutation loop without decoupling capacitor: 115nH, b) IGBT's commutation loop 48nH, c) MOSFET commutation loop with decoupling capacitor: 46nH |

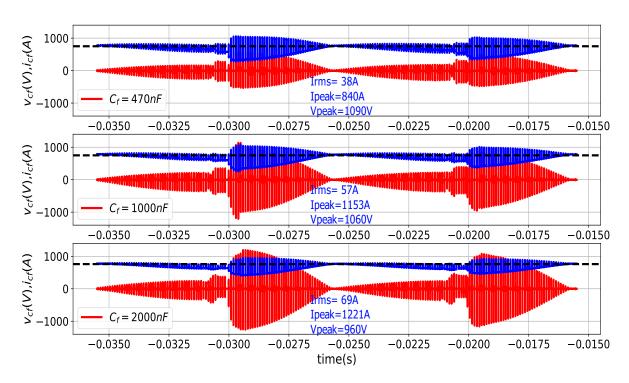

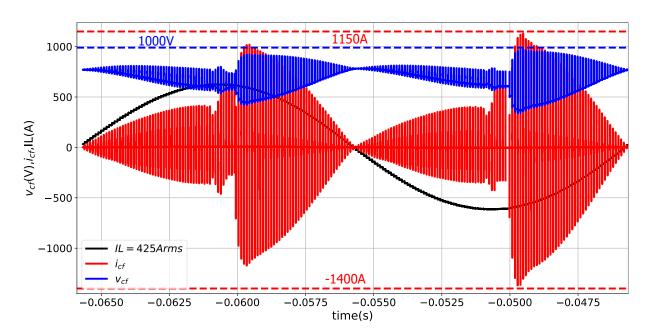

| <b>Figure A. 2.6:</b> Film capacitor's voltage and current waveform in one fundamental cycle, $V_{DC} = 1500V$ , $IL(rms) = 300A$ at different capacitor values.                                                                             |

| <b>Figure A. 2.7:</b> Conduction cooled capacitors are recommended for the decoupling capacito [59].                                                                                                                                         |

| <b>Figure A. 2.8:</b> Voltage and current of decoupling capacitor Cf = 1320nF during switching at ILmax = 625A,1500V                                                                                                                         |

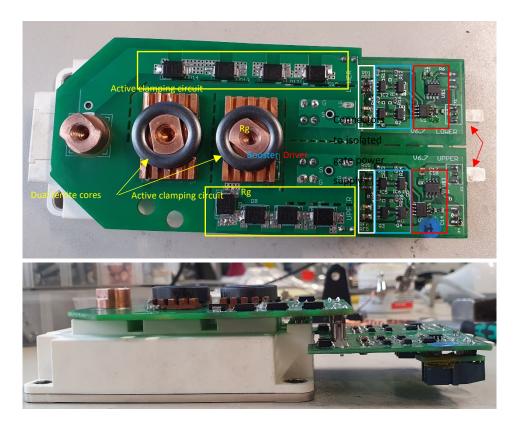

| <b>Figure A. 2.9:</b> <i>Gate driver and its assembly with the SiC MOSFET module.</i> 20                                                                                                                                                     |

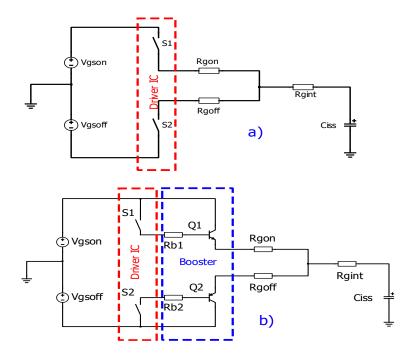

| <b>Figure A. 2.10:</b> The equivalent gate circuit of the MOSFET. Rgint, Ciss is the internal gate resistor and the input capacitor of the MOSFET module. a) without booster, b) with booster (dashed blue line)                             |

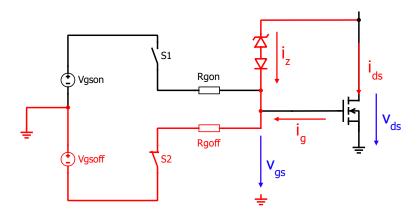

| Figure A. 2.11: Conventional active clamping.                                                                                                                                                                                                |

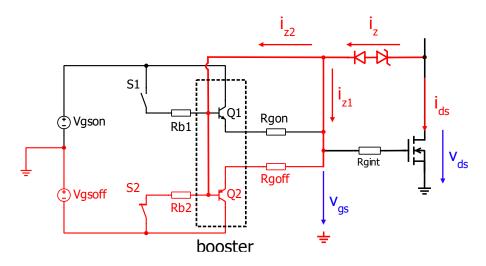

| Figure A. 2.12: Advanced active clamping                                                                                                                                                                                                     |

| <b>Figure A. 2.13:</b> The breakdown voltage of the TVS diodes increases with temperature which TVS' breakdown voltage at $25^{\circ}C = 1000V$ (solid lines), TVS' breakdown voltage at $75^{\circ}C = 1060V$ (dashed line).                |

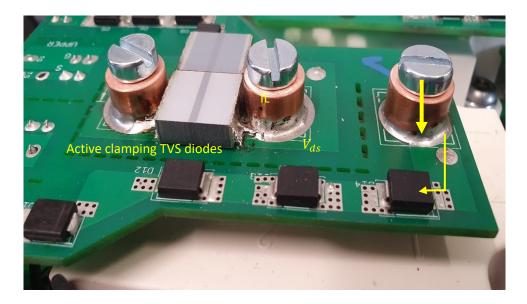

| Figure A. 2.14: Active clamping PCB with the special copper terminals allow high load current                                                                                                                                                |

| passing through and give the feedback voltage to the TVS diodes20:                                                                                                                                                                           |

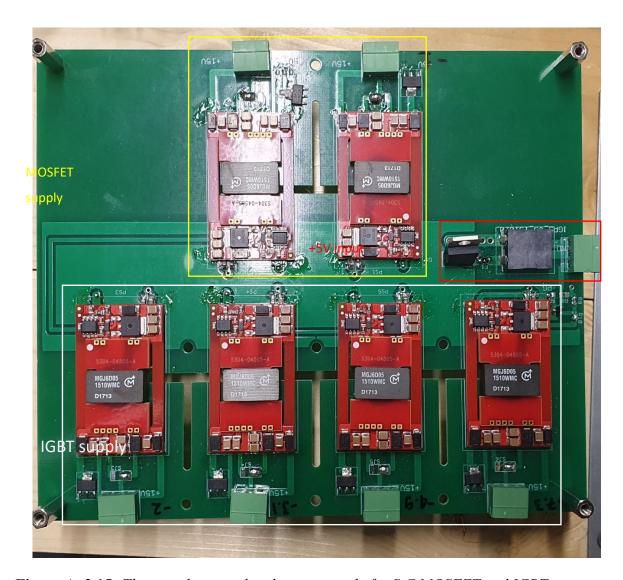

| <b>Figure A. 2.15:</b> The gate driver isolated power supply for SiC MOSFET and IGBT 200                                                                                                                                                     |

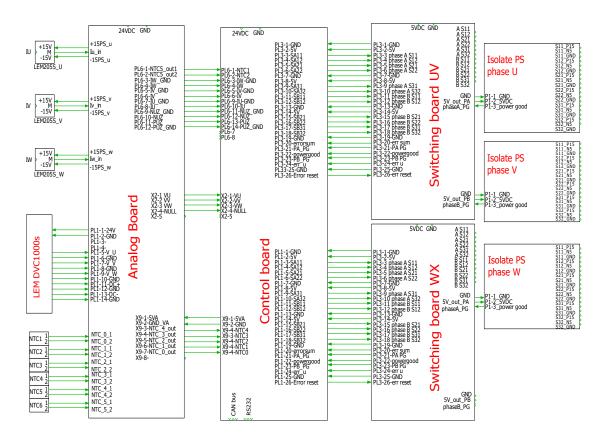

| Figure A. 2.16: Inverter's controller unit wiring diagram                                                                                                                                                                                    |

| Figure A. 2.17: The inverter's controller board.                              | 208        |

|-------------------------------------------------------------------------------|------------|

| Figure A. 2.18: The inverter's analog board and LEM DVC-1000 board            | 209        |

| Figure A. 2.19: The inverter's optical switching board.                       | 209        |

| Figure A. 2.20: Internal of the controller panel.                             | 210        |

| Figure A. 2.21:The back and front of the controller unit.                     | 210        |

| Figure A. 2.22: Optical CAN bus converter board.                              | 211        |

| Figure A. 2.23: LC filter assembly.                                           | 212        |

| Figure A. 2.24: Three phases assembly of the hybrid ANPC-front side           | 213        |

| Figure A. 2.25: Three phases assembly of the hybrid ANPC-back side            | 213        |

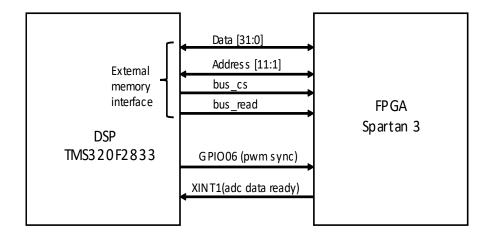

| Figure A. 2.26: The DSP and FPGA parallel communication.                      | 214        |

| Figure A. 2.27: The PWM generator signals are synchronized with the DSP's AD  | C sampling |

| frequency (pwm sync)                                                          | 215        |

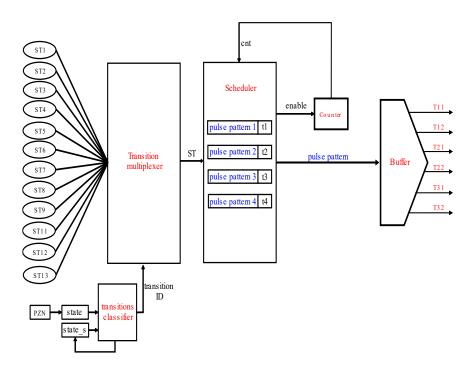

| Figure A. 2.28: Active cut-off switching scheme's state machine block diagram | 216        |

# **List of Tables**

| Table 1.1: PLECS simulation parameters.                                                                 | 2  |

|---------------------------------------------------------------------------------------------------------|----|

| Table 1.2: ANPC's different switching states.                                                           | 5  |

| <b>Table 1.3:</b> <i>PWM-1 [16]</i>                                                                     | 7  |

| Table 1.4: PWM-2 [13].                                                                                  | 8  |

| <b>Table 1.5:</b> <i>PWM-3</i> [14]                                                                     | 8  |

| <b>Table 1.6:</b> <i>PWM-4</i> [10]                                                                     | 8  |

| Table 1.7: Overview of publication on hybrid Si/SiC ANPC.                                               | 12 |

| Table 1.8: 500kW 3L-TDANPC parameters.                                                                  | 16 |

| <b>Table 2.1:</b> Switching transition at $t_1 = 0.5s$ , $IL > 0$ , $VDC1 > VDC2$                       | 32 |

| <b>Table 2.2:</b> Switching transition at $t_2 = 1s$ , $IL > 0$ , VDC1 > VDC2                           | 34 |

| <b>Table 2.3:</b> Switching transition at $t_1 = 0.5s$ , $IL < 0$ , VDC1 > VDC2                         | 35 |

| <b>Table 2.4:</b> Switching transition at $t_2 = 1s$ , $IL < 0$ , VDC1 > VDC2                           | 37 |

| Table 3.1: Common metals and their resistivity, permeability.                                           | 43 |

| Table 3.2: Compare Iron powder FE893 core and soft ferrite T35 core properties                          | 49 |

| Table 3.3: Three different cores are used in the single pulse test to measure the core's of inductance. |    |

| Table 3.4: Estimated oscillation frequency at turn-off of Fe893 core and T35 core.                      | 61 |

| Table 3.5: The upper and lower core's inductance at the overvoltage moment during                       |    |

| <b>Table 4.1:</b> Conventional switching state P. dead time. 7P of the hybrid 4NPC                      | 74 |

| Table 4.2: Active cut-off switching state P, dead time, ZP of the hybrid ANPC                                                                                                 | 75       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Table 4.3: Transition number 2, direction from P to ZP.                                                                                                                       | 77       |

| Table 4.4: Transition number 3, direction from ZN to N.                                                                                                                       | 79       |

| Table 4.5: Transition number 7, direction from ZP to N.                                                                                                                       | 81       |

| Table 4.6: Non-optimal trigger times calculation.                                                                                                                             | 93       |

| Table 4.7: Optimal trigger times calculation.                                                                                                                                 | 95       |

| <b>Table 4.8:</b> Turn-off delay time with different $C_{goff}$ values.                                                                                                       | 97       |

| Table 6.1: Measurement probes' specifications.                                                                                                                                | 135      |

| Table 6.2: Turn-off delay and transient phases of different Rgoff.                                                                                                            | 142      |

| <b>Table 6.3:</b> Turn-on delay and transient phases of different R <sub>gon</sub>                                                                                            | 143      |

| Table 6.4: Temperatures of ANPC's critical components at different operating currents.                                                                                        | 157      |

| Table 6.5: Thermal resistance of the ANPC's components.                                                                                                                       | 158      |

| <b>Table 6.6:</b> Estimated power losses and junction temperatures of the semiconductor during the continuous experiment at $22^{\circ}C$ ambient temperature, $IL = 305Arms$ |          |

| Table 6.7: Estimated power losses and junction temperatures of the semiconductor de                                                                                           | vices at |

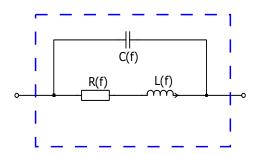

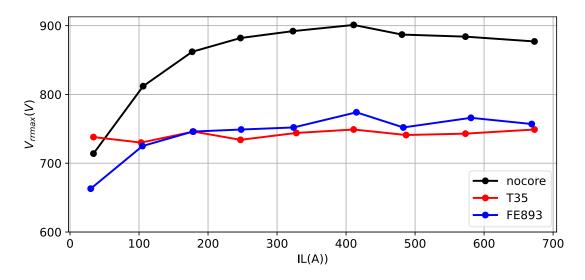

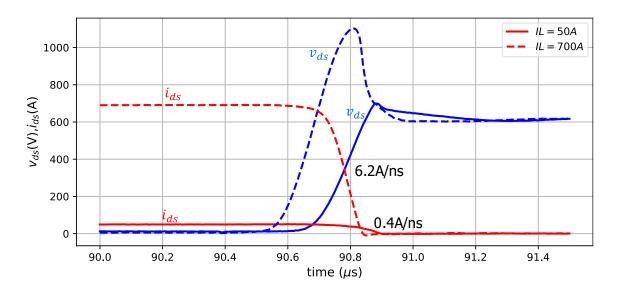

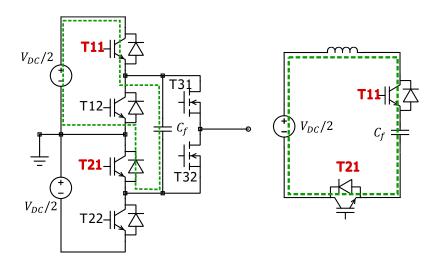

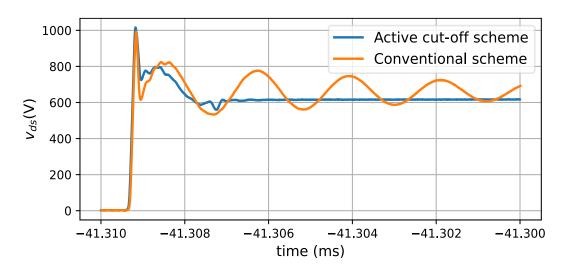

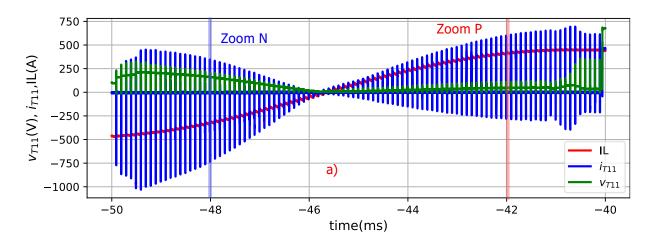

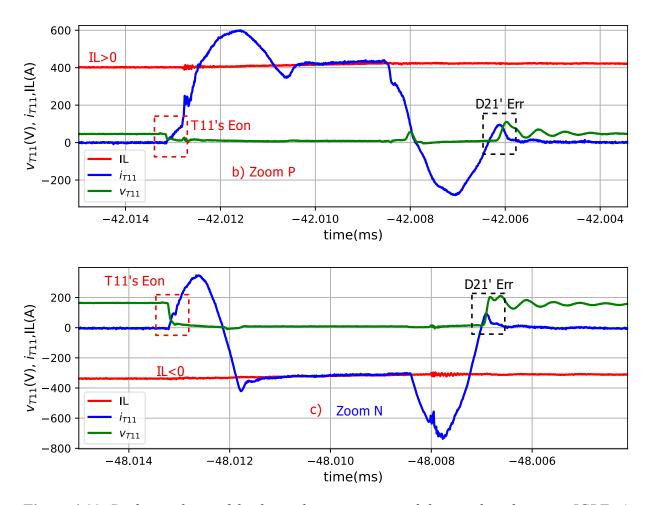

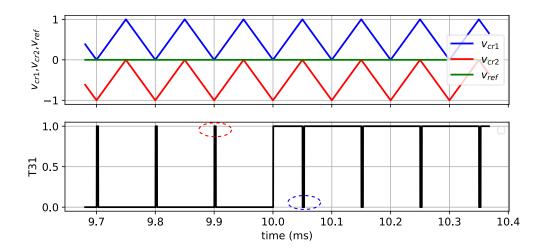

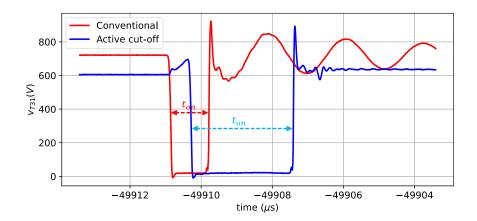

| full modulation index and 22°C ambient temperature, $IL = 305 Arms$                                                                                                           | 160      |